NESA011B march 2023 – june 2023 MSPM0G1105 , MSPM0G1106 , MSPM0G1107 , MSPM0G1505 , MSPM0G1506 , MSPM0G1507 , MSPM0G3105 , MSPM0G3106 , MSPM0G3107 , MSPM0G3505 , MSPM0G3506 , MSPM0G3507

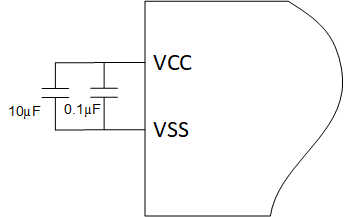

2.4 電源供應器的建議去耦電路

TI 建議將 10-μF 和 100-nF 低 ESR 陶瓷去耦電容器的組合連接到 DVCC 針腳 (請參閱 圖 2-3)。可使用數值較高的電容器,但會影響電源供應軌上升時間。去耦電容器的位置必須儘可能靠近去耦的針腳 (應在數毫米內)。

圖 2-3 電源供應去耦電路

圖 2-3 電源供應去耦電路