SBAA576A may 2023 – june 2023 ADS54J60

5.4 Reading the Frozen DC Offset Values

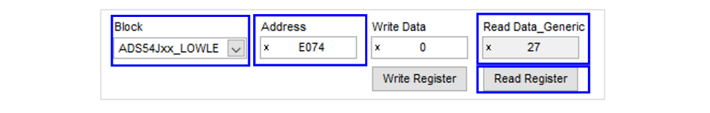

The DC offset correction values are setup to be read and recorded. Using the ADS54JXX GUI, navigate to the ‘Low Level View’ tab. Select the ADS54Jxx_LowLevel block. The 11-bit DC offset correction values can be read and recorded from addresses 0xE074 through 0xE07B for Channel A, and from 0xF074 through 0xF07B for Channel B.

Figure 5-3 ADS54J60 GUI Register R/W

Feature

Figure 5-3 ADS54J60 GUI Register R/W

FeatureTable 5-1 Recorded Frozen DC Offset

Values

| Address (CHA) | DC Offset Correction Value (this example) |

Address (CHB) | DC Offset Correction Value |

|---|---|---|---|

| 0xE074 | 0x27 | 0xF074 | (value) |

| 0xE075 | 0x07 | 0xF075 | (value) |

| 0xE076 | 0x3A | 0xF076 | (value) |

| 0xE077 | 0x07 | 0xF077 | (value) |

| 0xE078 | 0xCC | 0xF078 | (value) |

| 0xE079 | 0x00 | 0xF079 | (value) |

| 0xE07A | 0xCC | 0xF07A | (value) |

| 0xE07B | 0x00 | 0xF07B | (value) |