SBAU378A September 2021 – January 2022 ADS1148 , ADS1248

- Trademarks

- 1Introduction

- 2Getting Started With the ADS1x48EVM

-

3ADS1x48EVM Overview

- 3.1 Analog and Digital Power Supplies

- 3.2 Voltage Reference Options

- 3.3 Clock Options

- 3.4 Digital Interface

- 3.5

Analog Input Connections

- 3.5.1 Connecting a Thermocouple to J5 on the ADS1x48EVM

- 3.5.2 Connecting a Thermistor to J5 on the ADS1x48EVM

- 3.5.3

Connecting an RTD to J6 on the ADS1x48EVM

- 3.5.3.1 Connecting a 2-Wire RTD Using a Low-Side RREF to J6 on the ADS1x48EVM

- 3.5.3.2 Connecting a 2-Wire RTD Using a High-Side RREF to J6 on the ADS1x48EVM

- 3.5.3.3 Connecting a 3-Wire RTD Using One IDAC and a Low-Side RREF to J6 on the ADS1x48EVM

- 3.5.3.4 Connecting a 3-Wire RTD Using One IDAC and a High-Side RREF to J6 on the ADS1x48EVM

- 3.5.3.5 Connecting a 3-Wire RTD Using Two IDACs and a Low-Side RREF to J6 on the ADS1x48EVM

- 3.5.3.6 Connecting a 3-Wire RTD Using Two IDACs and a High-Side RREF to J6 on the ADS1x48EVM

- 3.5.3.7 Connecting a 4-Wire RTD Using a Low-Side RREF to J6 on the ADS1x48EVM

- 3.5.3.8 Connecting a 4-Wire RTD Using a High-Side RREF to J6 on the ADS1x48EVM

- 3.5.3.9 Summary of ADS1x48EVM RTD Configuration Settings

- 3.5.4 Connecting a General-Purpose Input to J5 on the ADS1x48EVM

- 4ADS1x48EVM GUI

- 5Bill of Materials, Printed Circuit Board Layout, and Schematic

- 6Revision History

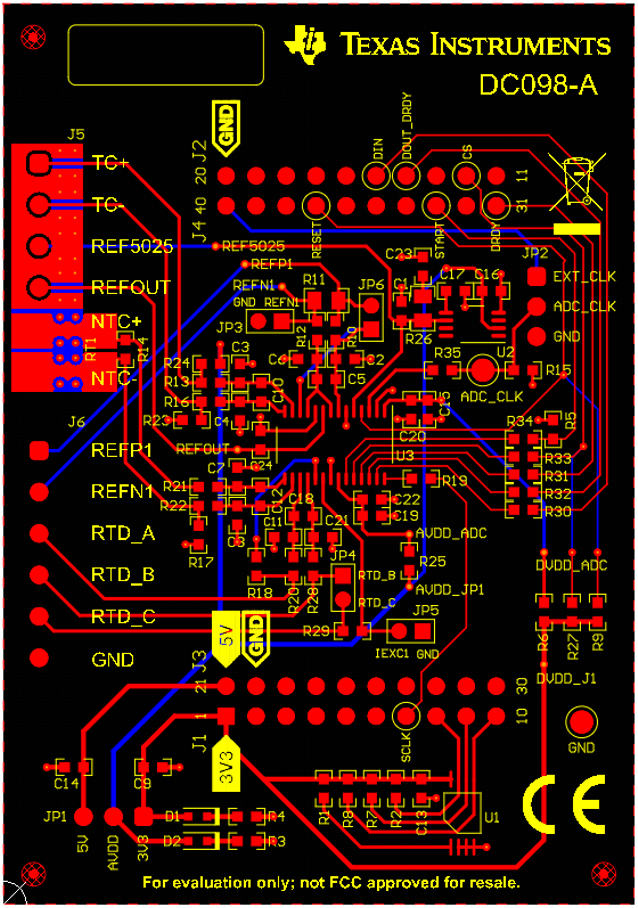

5.2 Printed Circuit Board Layout

Figure 5-1 to Figure 5-7 depict the ADS1x48EVM PCB layout.

Red = top layer; blue = bottom

layer; yellow = top silkscreen; internal GND layers not shown

Figure 5-1 Composite PCB Layout Figure 5-2 Top Silkscreen

Figure 5-2 Top Silkscreen Figure 5-4 Internal Ground Layer

1

Figure 5-4 Internal Ground Layer

1 Figure 5-6 Bottom Layer

Figure 5-6 Bottom Layer Figure 5-3 Top Layer

Figure 5-3 Top Layer Figure 5-5 Internal Ground Layer

2

Figure 5-5 Internal Ground Layer

2 Figure 5-7 Bottom Silkscreen

Figure 5-7 Bottom Silkscreen