SBOK079 October 2023 TPS7H2140-SEP

PRODUCTION DATA

- 1

- Abstract

- Trademarks

- 1 Introduction

- 2 Single-Event Effects (SEE)

- 3 Device and Test Board Information

- 4 Irradiation Facility and Setup

- 5 Depth, Range, and LETEFF Calculation

- 6 Test Setup and Procedures

- 7 Destructive Single-Event Effects (DSEE)

- 8 Single-Event Transients (SET)

- 9 Event Rate Calculations

- 10Summary

- 11References

3 Device and Test Board Information

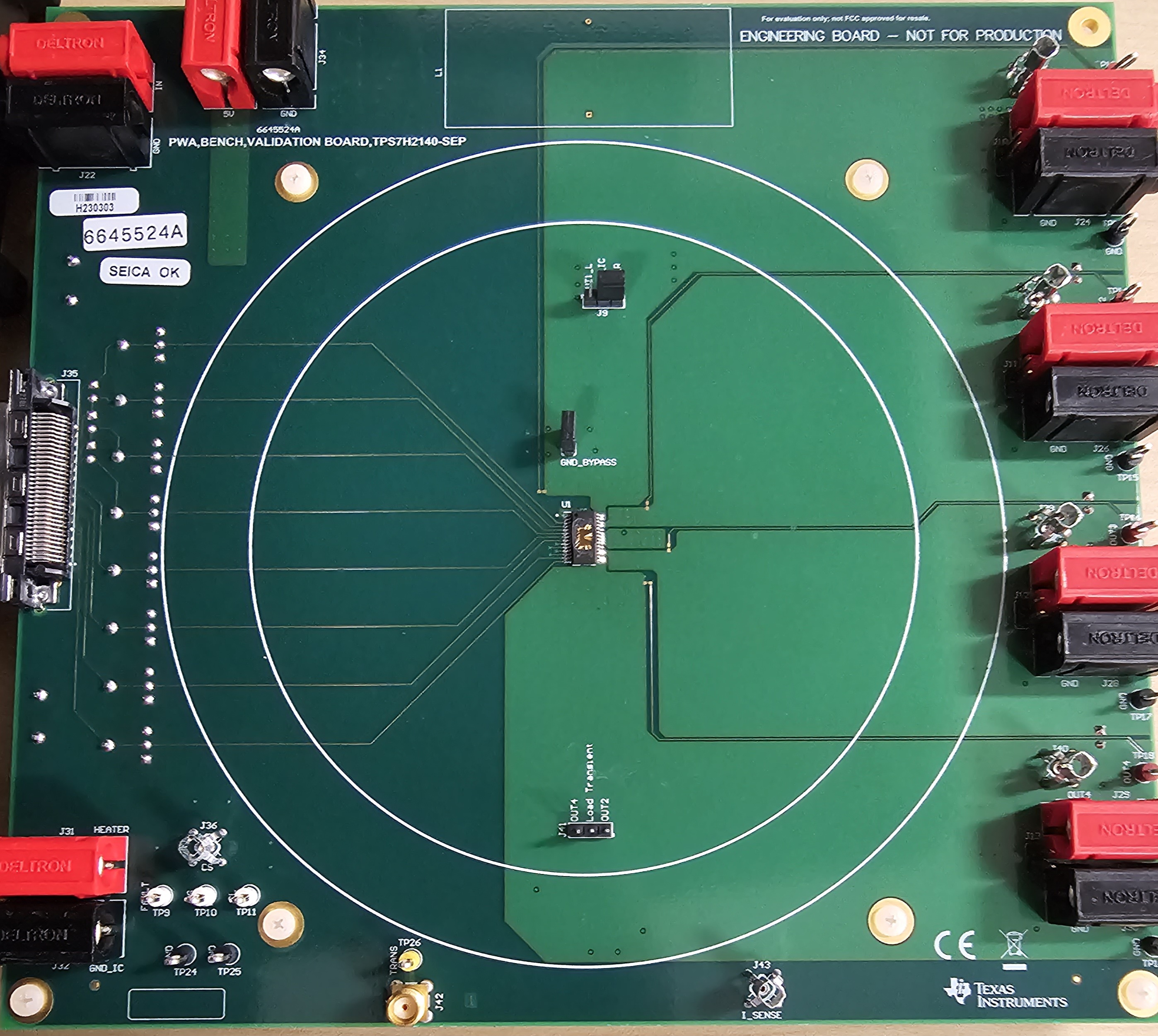

The TPS7H2140-SEP is packaged in a 28-pin HTSSOP plastic package as shown in Figure 3-1. An evaluation board designed for radiation testing was used to evaluate the performance and characteristics of the TPS7H2140-SEP under heavy-ions. Figure 3-2 shows the top view of the evaluation board used for the radiation testing. Figure 3-3 shows the EVM board schematics used for the heavy-ion testing campaign.

![TPS7H2140-SEP Photograph of Delidded TPS7H2140-SEP [Left] and Pinout Diagram [Right] GUID-20230914-SS0I-ZXFM-JCPK-C8PMNNBJSVF5-low.svg](/ods/images/SBOK079/GUID-20230914-SS0I-ZXFM-JCPK-C8PMNNBJSVF5-low.svg)

The package was delidded to reveal the die face for all heavy-ion testing.

Figure 3-1 Photograph of Delidded TPS7H2140-SEP [Left] and Pinout Diagram [Right] Figure 3-2 TPS7H2140-SEP Board Top

View

Figure 3-2 TPS7H2140-SEP Board Top

View Figure 3-3 TPS7H2140-SEP SEE Validation

EVM Schematic

Figure 3-3 TPS7H2140-SEP SEE Validation

EVM Schematic