SBOU293E November 2022 – August 2024

- 1

- Description

- Features

- 4

- 1Evaluation Module Overview

- 2Hardware

-

3Software

- 3.1

OPTEVM Software

- 3.1.1 Hardware Requirements

- 3.1.2 Software Installation

- 3.1.3 Typical OPTEVM Hardware Setup

- 3.1.4 Launching the OPT300x/4xxxEVM Software

- 3.1.5 OPTEVM Software Operation

- 3.1.6 Controls

- 3.1.7 OPTxxxDTSEVM Variants

- 3.1.8 Scripts Window

- 3.1

OPTEVM Software

- 4Hardware Design Files

- 5Additional Information

- 6Related Documentation from Texas Instruments

- 7Revision History

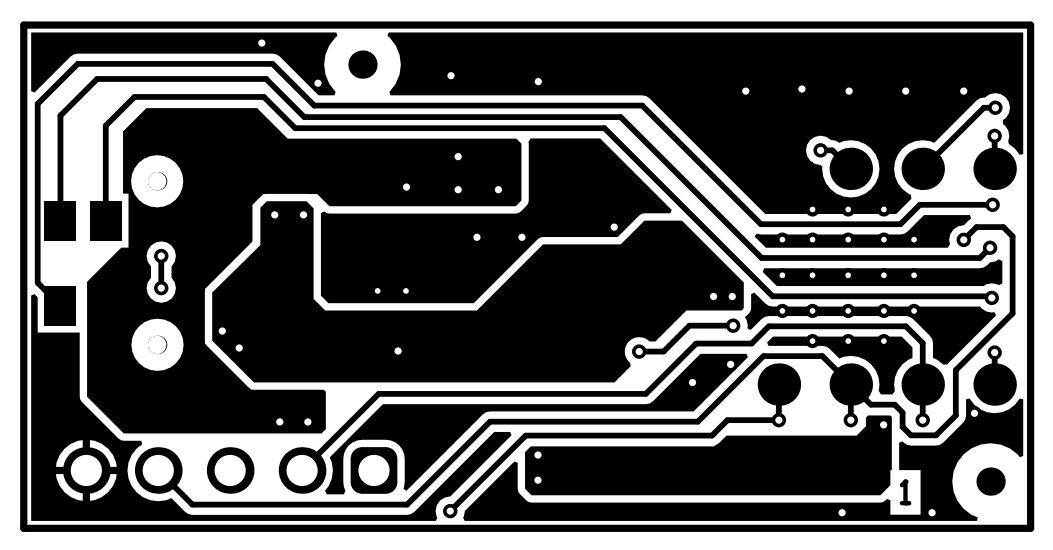

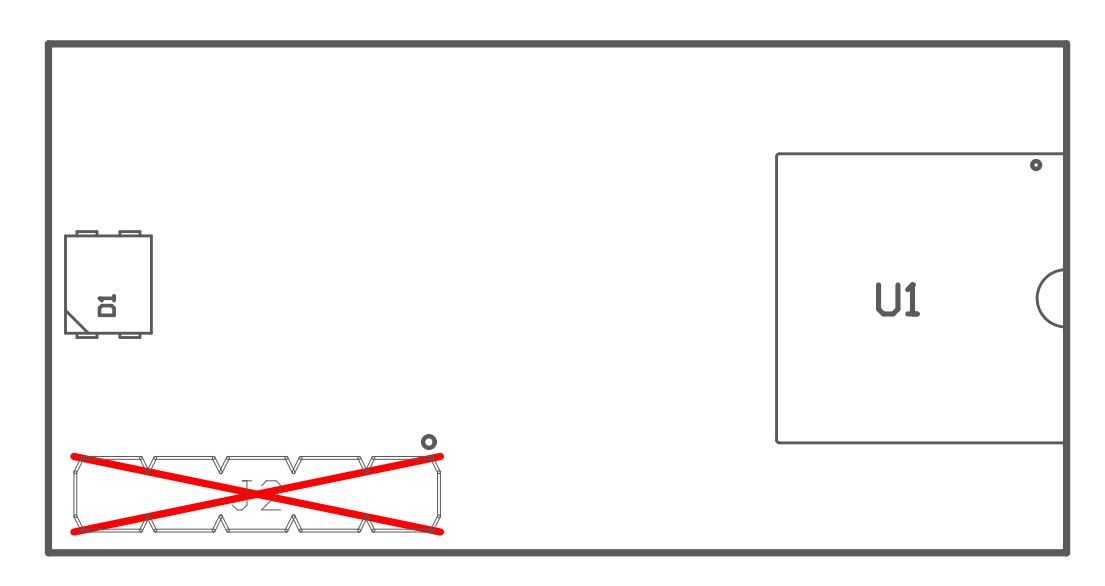

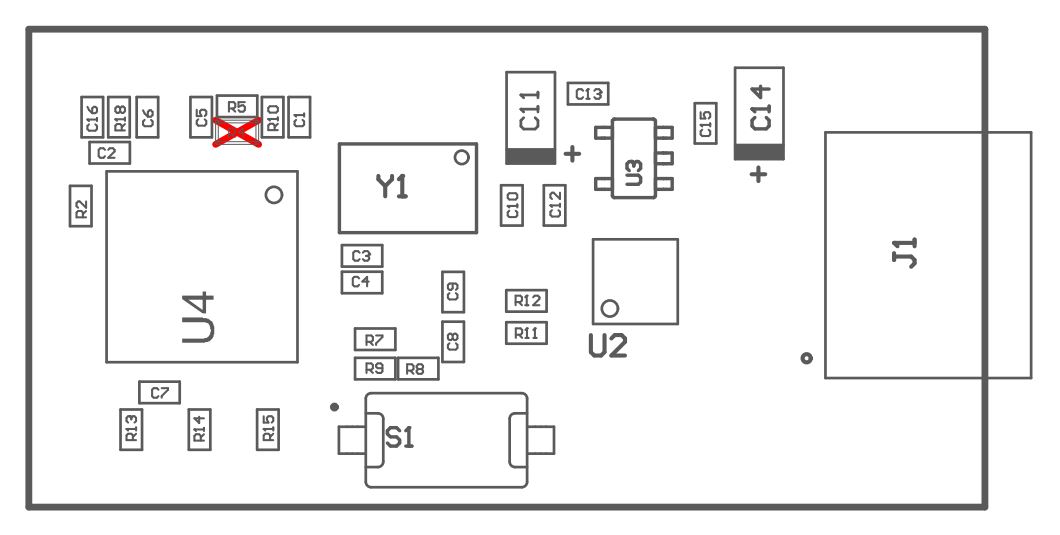

4.2.2 PCB Layout

Figure 5-2 and Figure 5-3 show the top and bottom PCB layers, respectively, of the test board. Figure 5-4 and Figure 5-5 show the assembly drawings of the top and bottom PCB layers, respectively.

Figure 4-7 PCB Top

Layer

Figure 4-7 PCB Top

Layer Figure 4-8 PCB

Bottom Layer

Figure 4-8 PCB

Bottom Layer Figure 4-9 PCB Top-Layer Assembly

Drawing

Figure 4-9 PCB Top-Layer Assembly

Drawing Figure 4-10 PCB Bottom-Layer Assembly

Drawing

Figure 4-10 PCB Bottom-Layer Assembly

Drawing