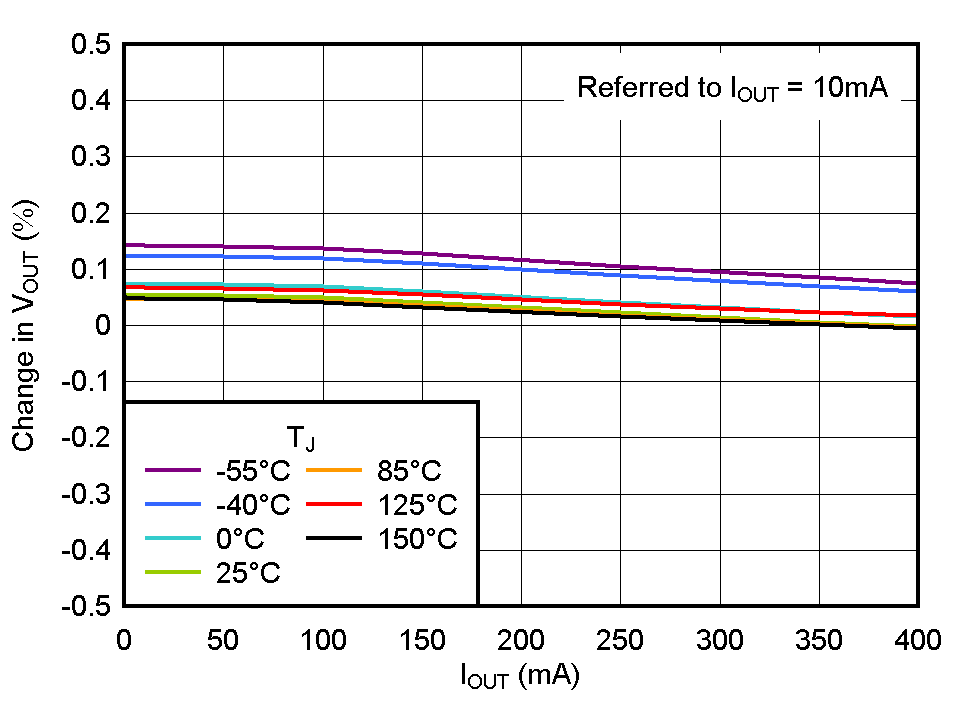

For all voltage versions, at TJ = 25°C,

VIN = VOUT(nom) + 0.5 V, IOUT = 10 mA,

VEN = 1.7 V, and COUT = 0.1 μF, unless otherwise

noted.

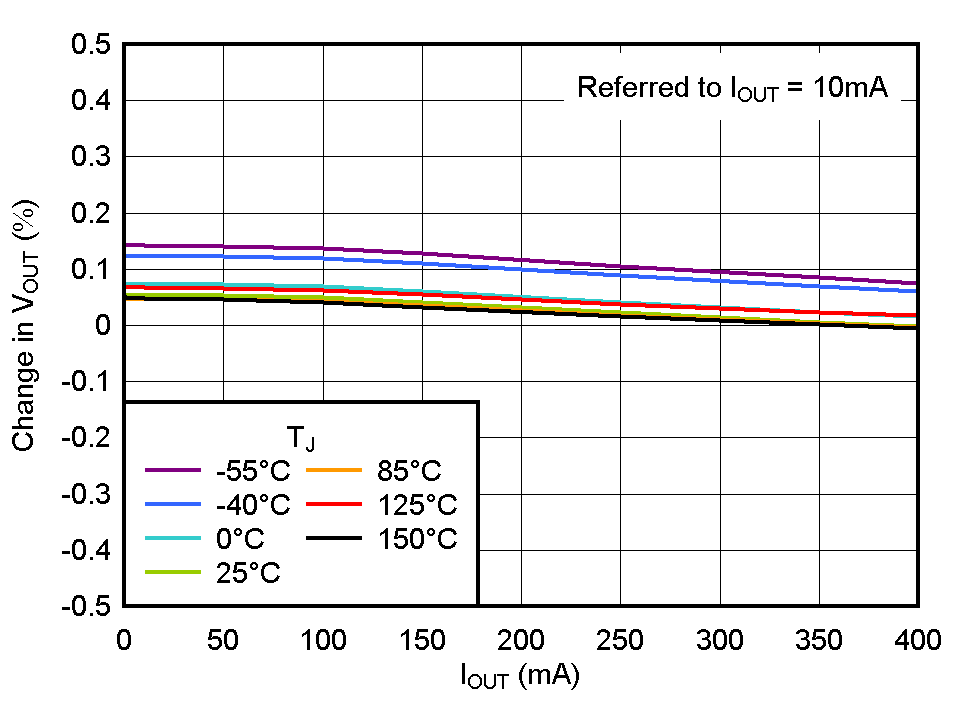

Figure 5-1 Load

Regulation

Figure 5-1 Load

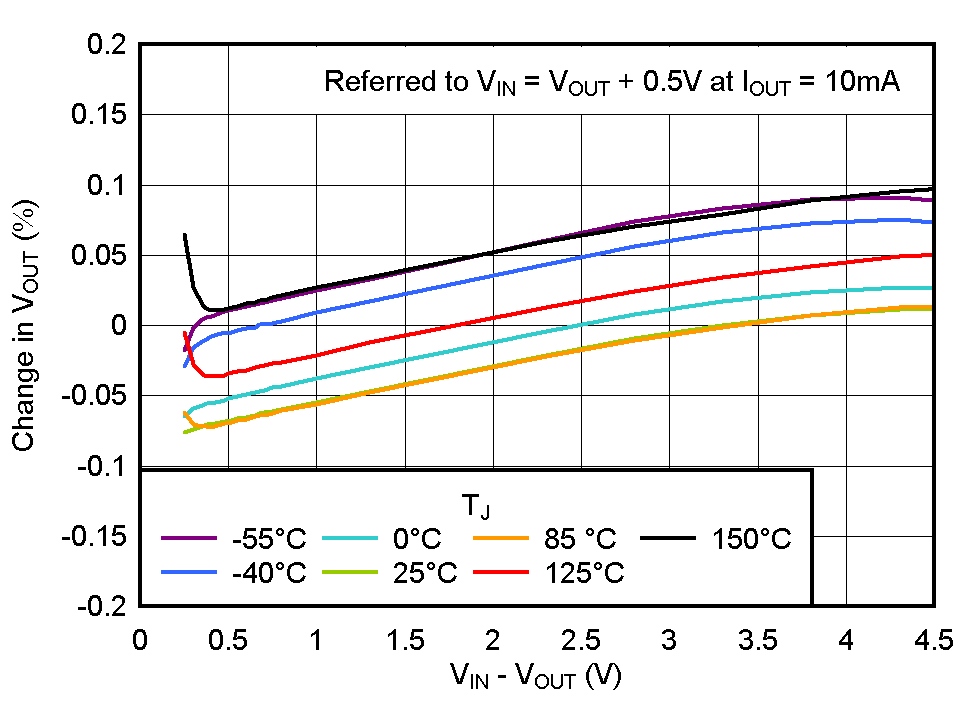

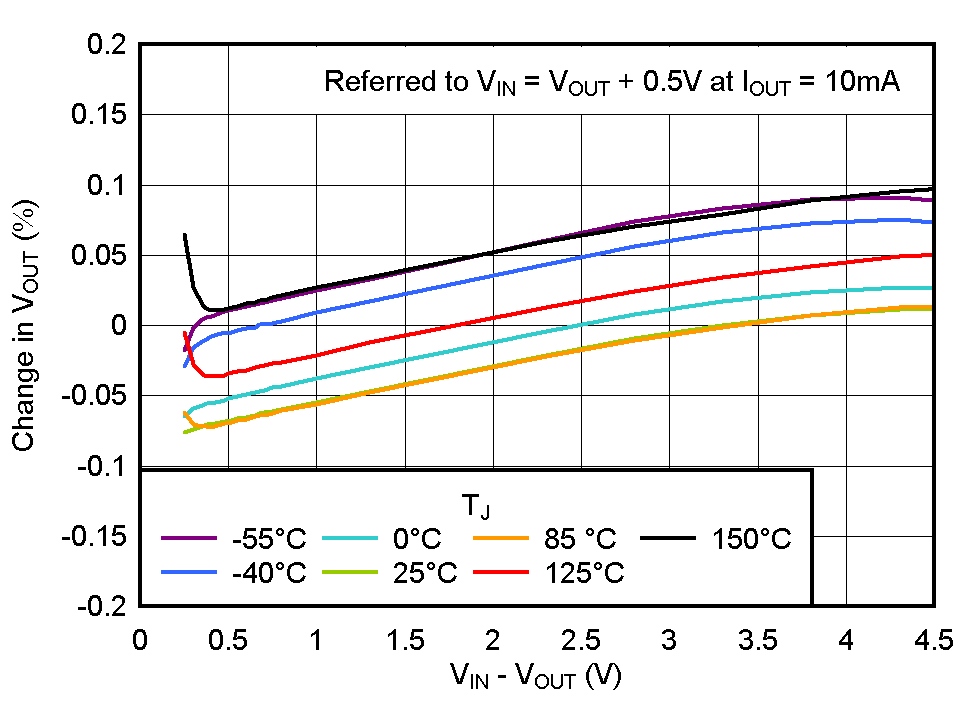

Regulation Figure 5-3 Line

Regulation

Figure 5-3 Line

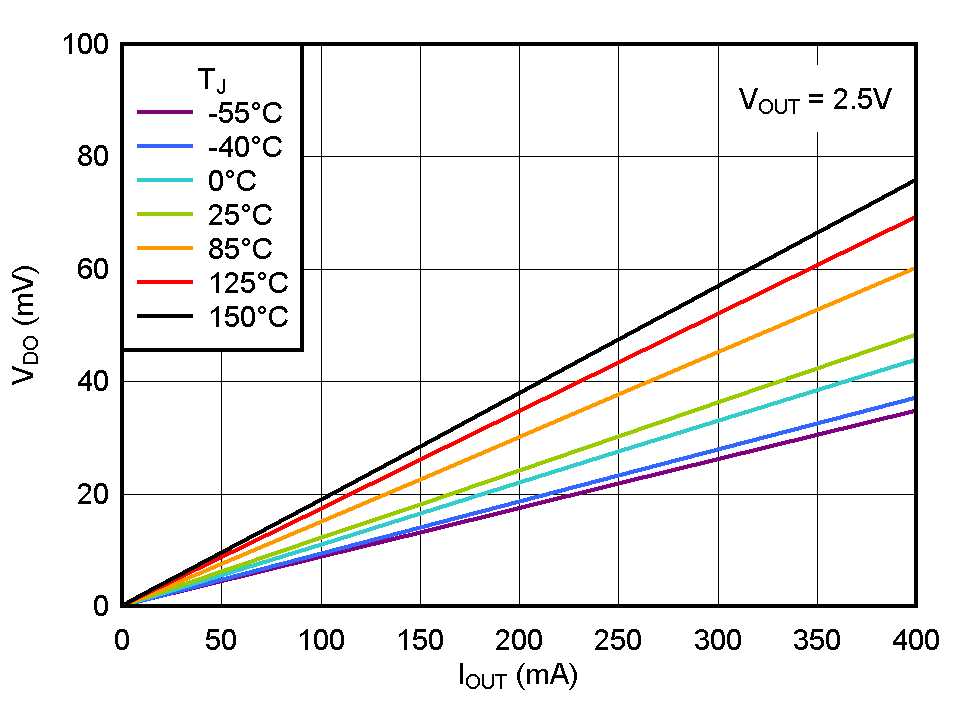

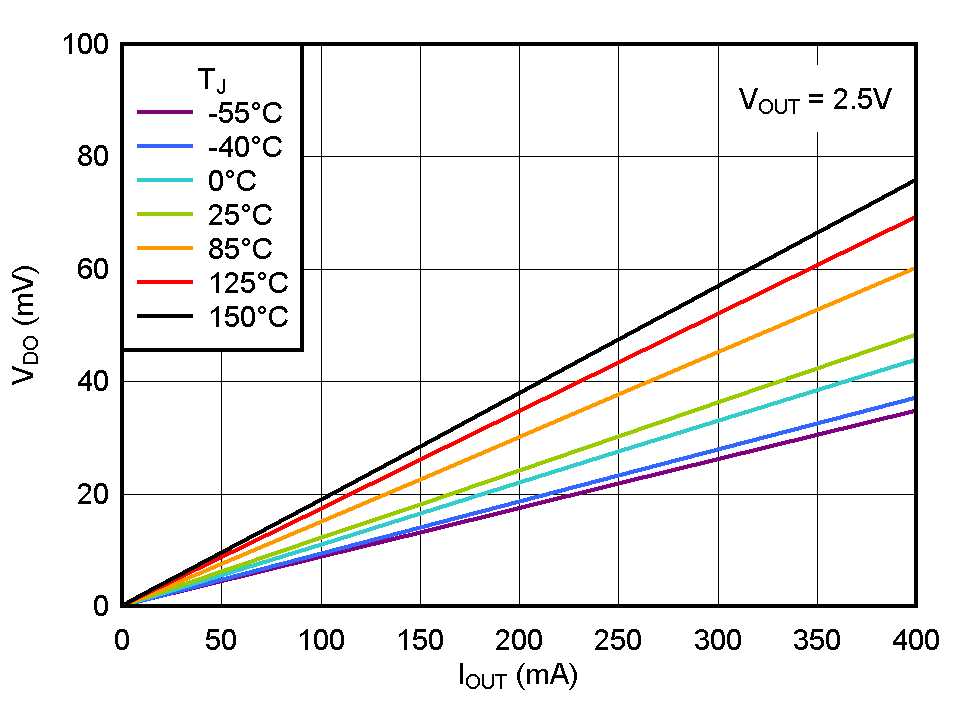

Regulation Figure 5-5 Dropout Voltage vs Output Current

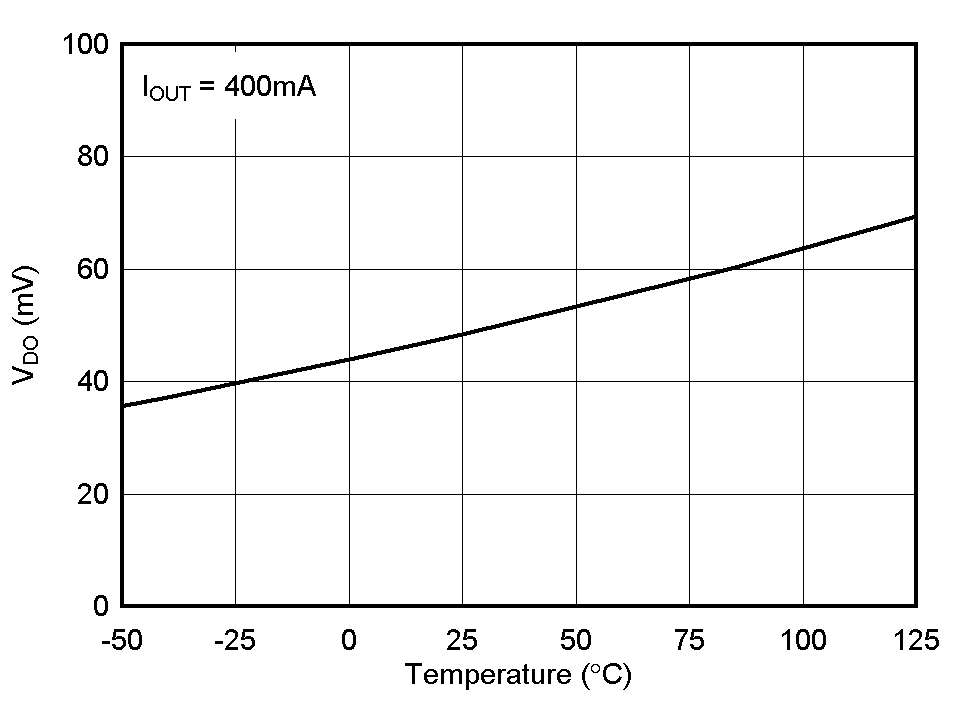

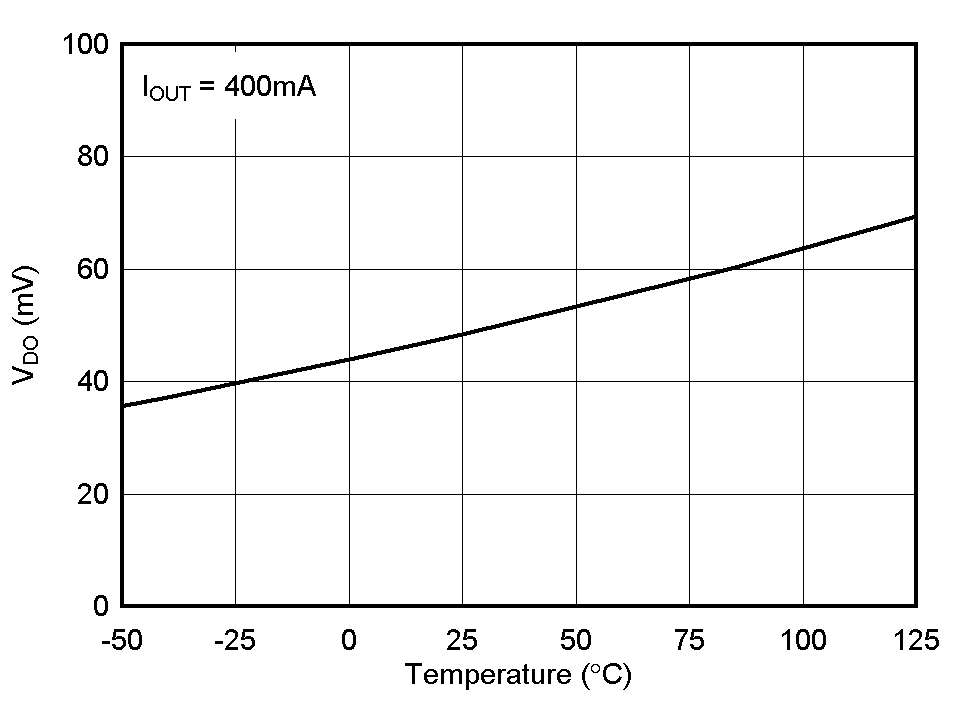

Figure 5-5 Dropout Voltage vs Output Current Figure 5-7 Dropout Voltage vs Temperature

Figure 5-7 Dropout Voltage vs Temperature Figure 5-9 Output Voltage Accuracy Histogram

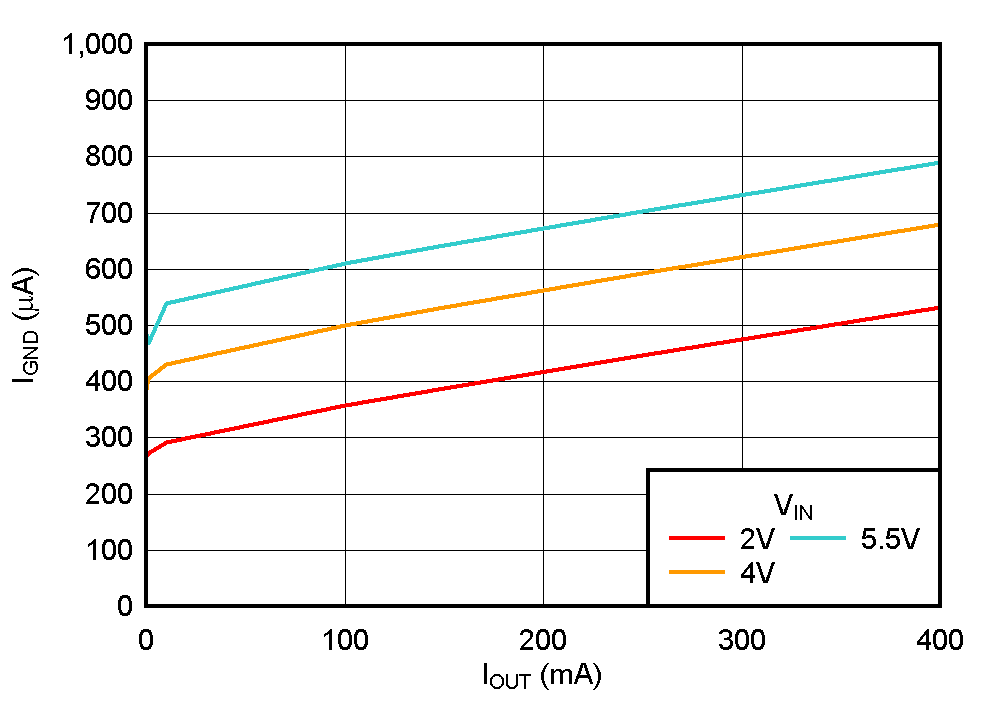

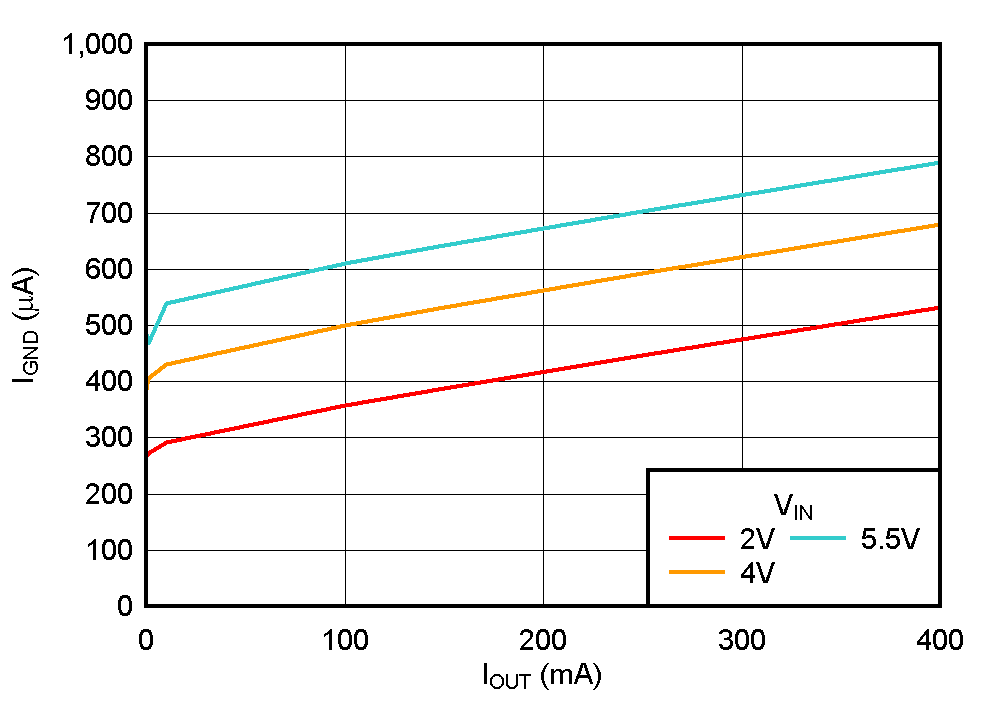

Figure 5-9 Output Voltage Accuracy Histogram Figure 5-11 Ground Pin Current vs Output Current

Figure 5-11 Ground Pin Current vs Output Current Figure 5-13 Ground Pin Current vs Temperature

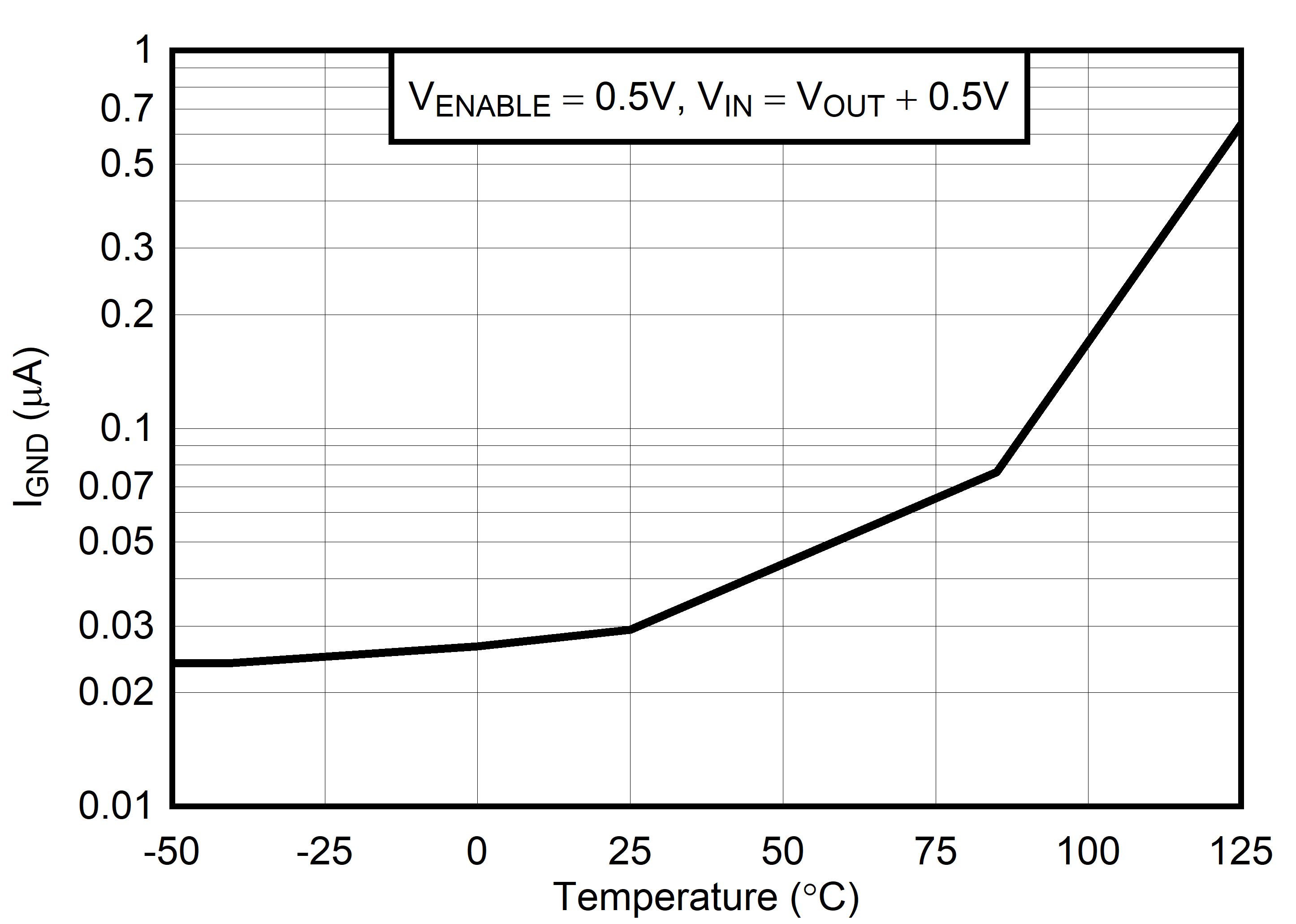

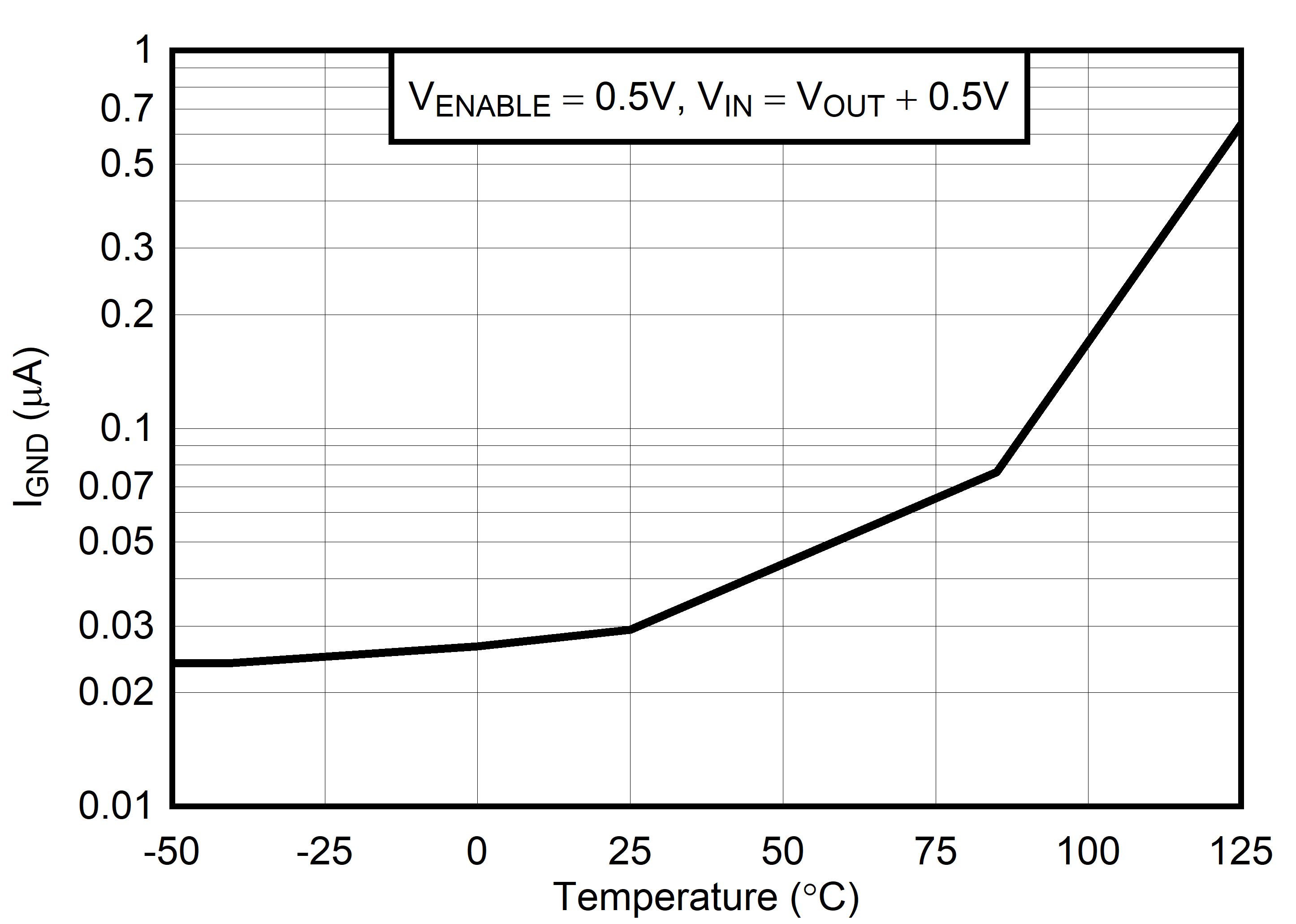

Figure 5-13 Ground Pin Current vs Temperature Figure 5-15 Ground Pin Current In Shutdown vs Temperature

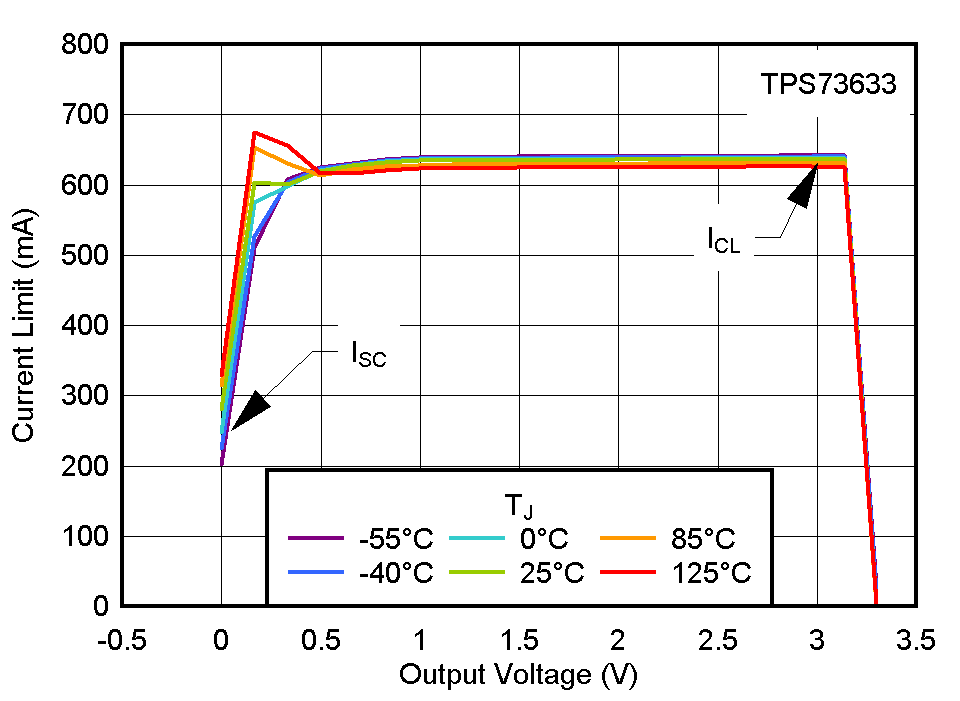

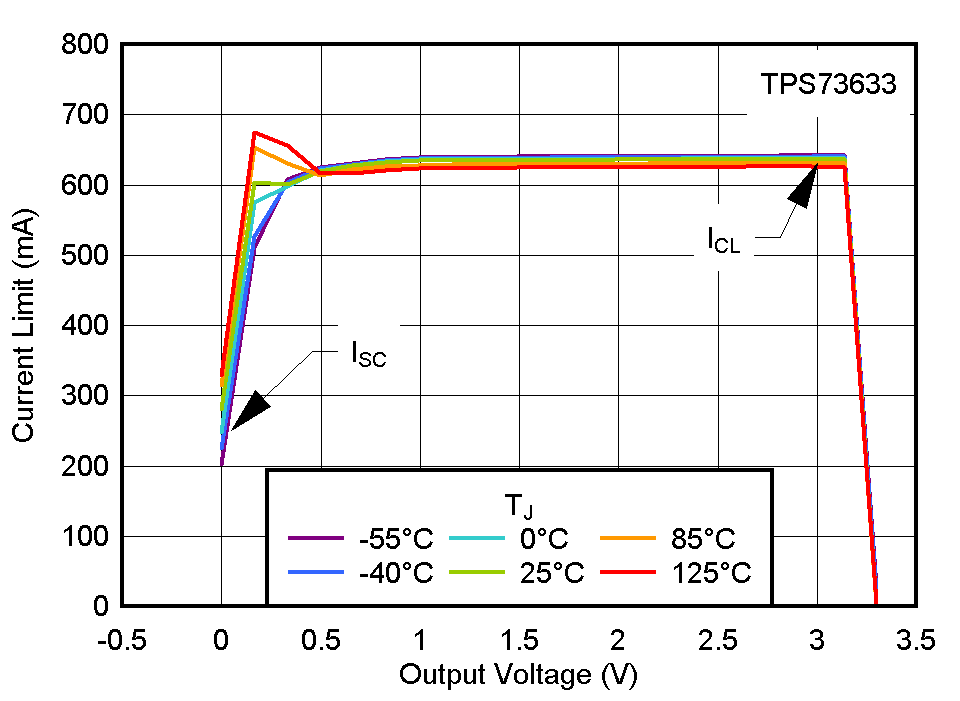

Figure 5-15 Ground Pin Current In Shutdown vs Temperature Figure 5-17 Current Limit vs VOUT (Foldback)

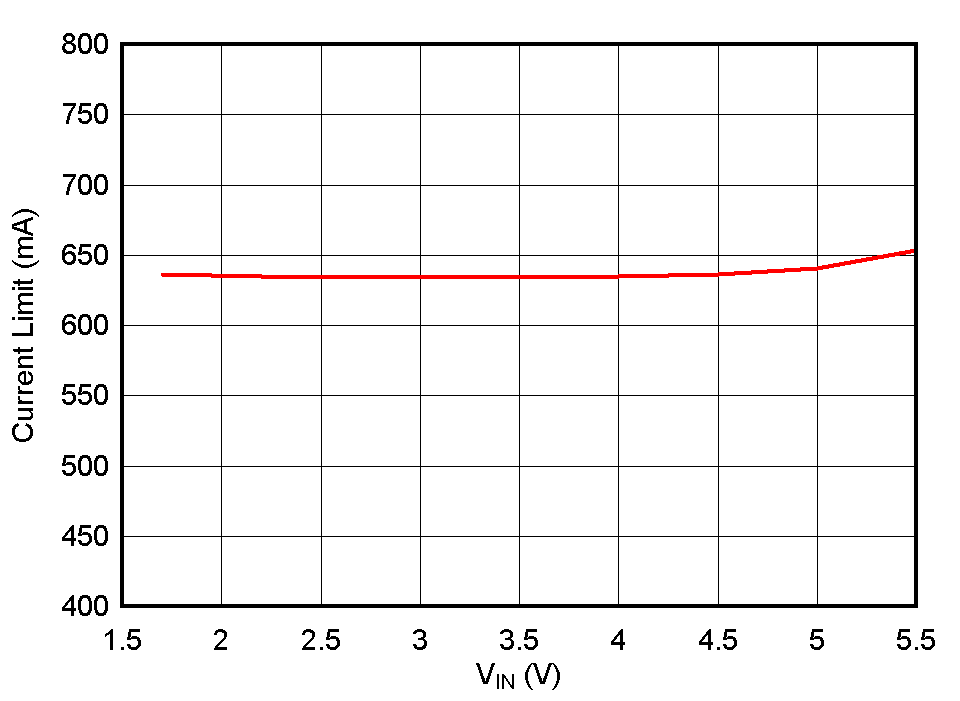

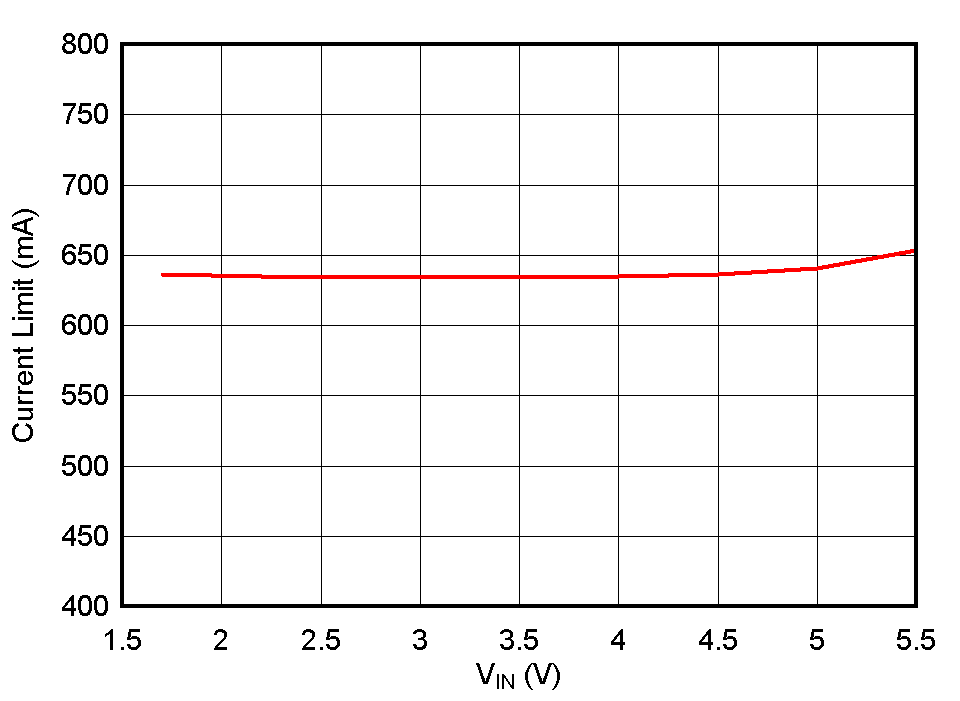

Figure 5-17 Current Limit vs VOUT (Foldback) Figure 5-19 Current Limit vs VIN

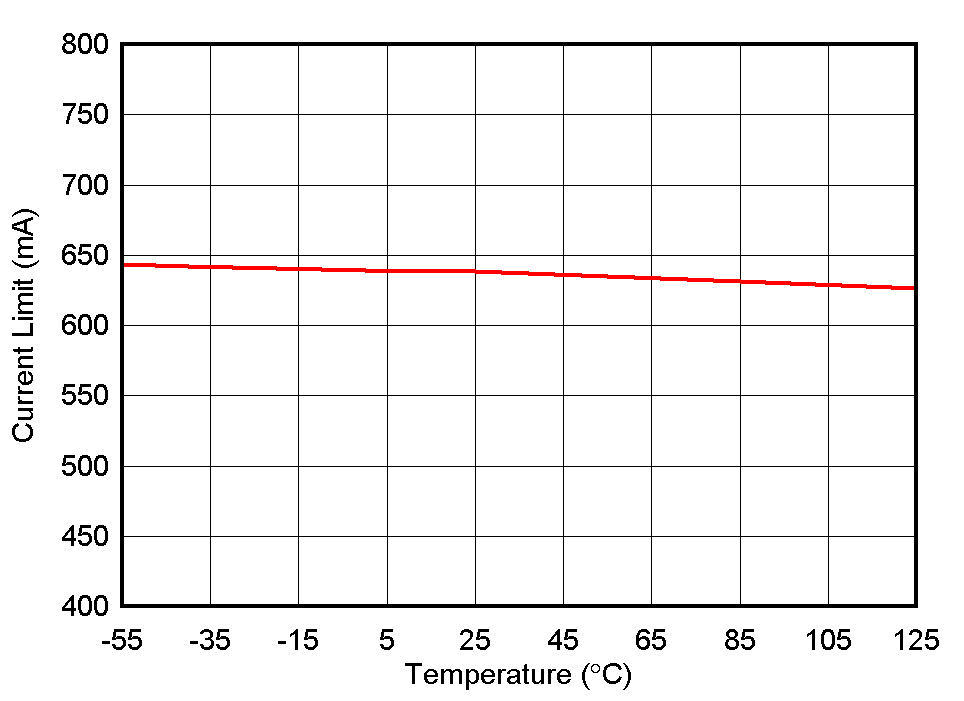

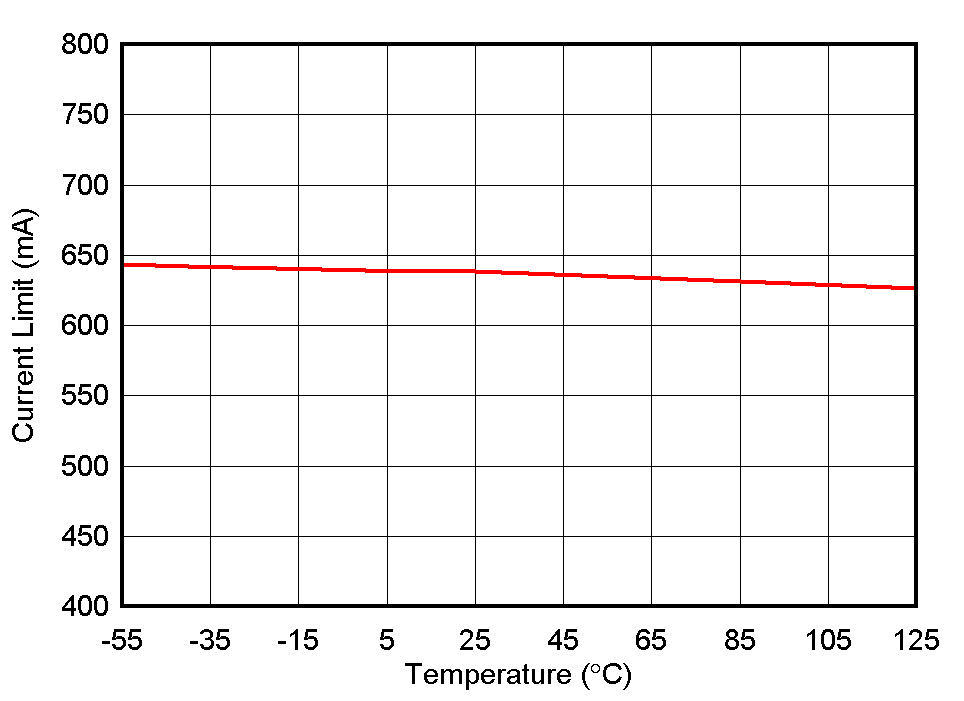

Figure 5-19 Current Limit vs VIN Figure 5-21 Current Limit vs Temperature

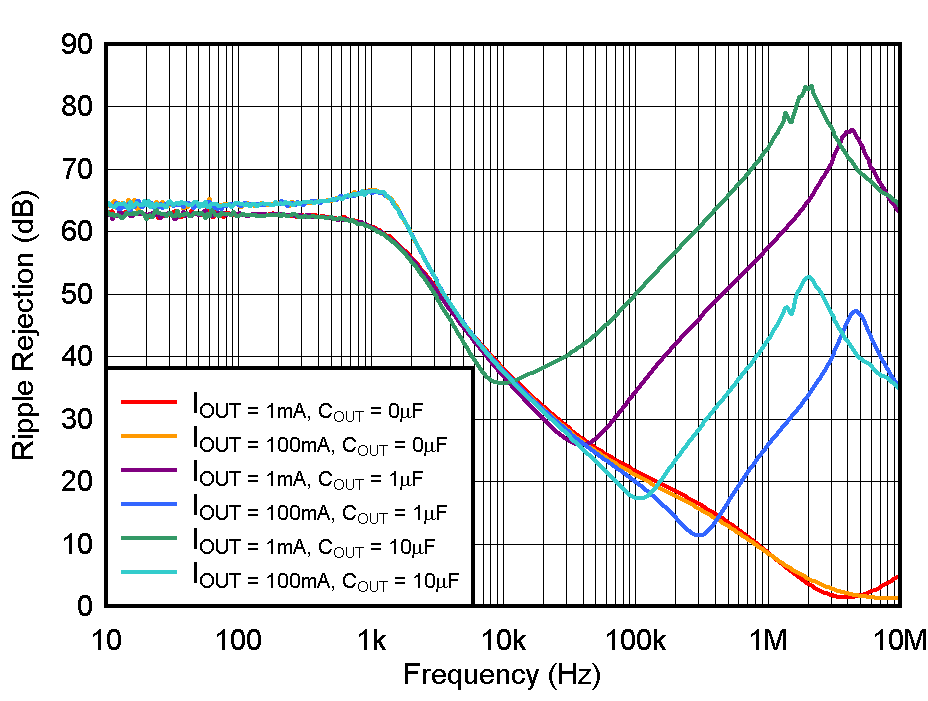

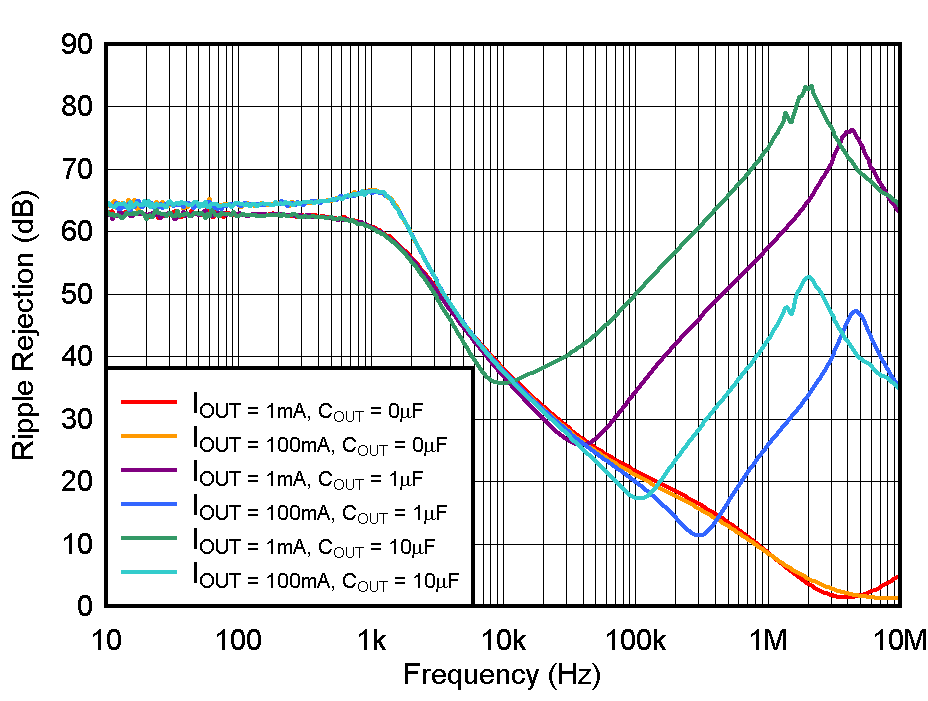

Figure 5-21 Current Limit vs Temperature Figure 5-23 PSRR

(Ripple Rejection) vs Frequency

Figure 5-23 PSRR

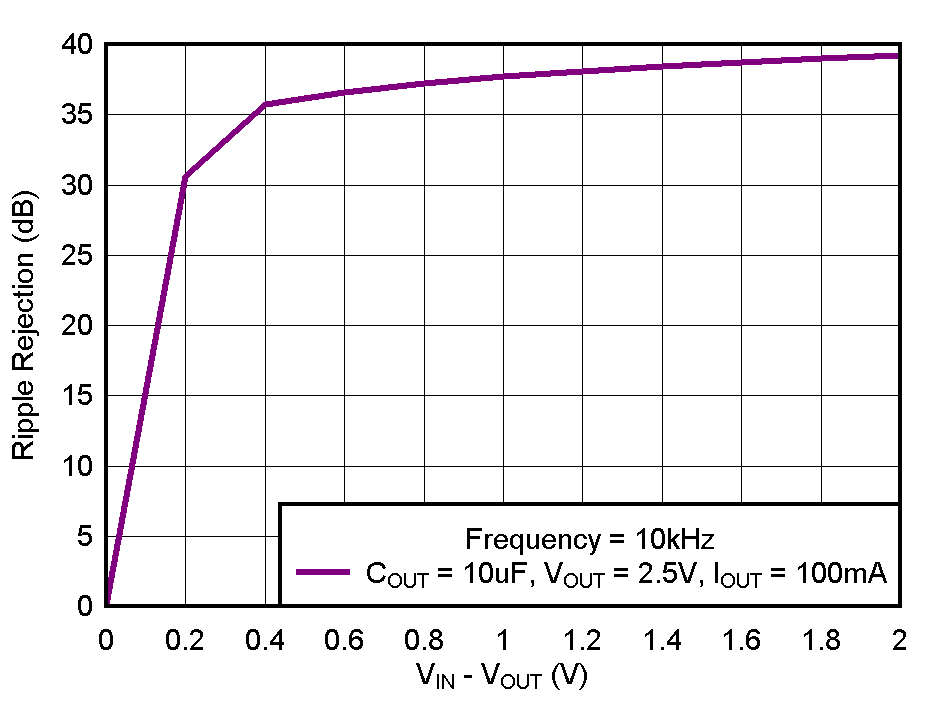

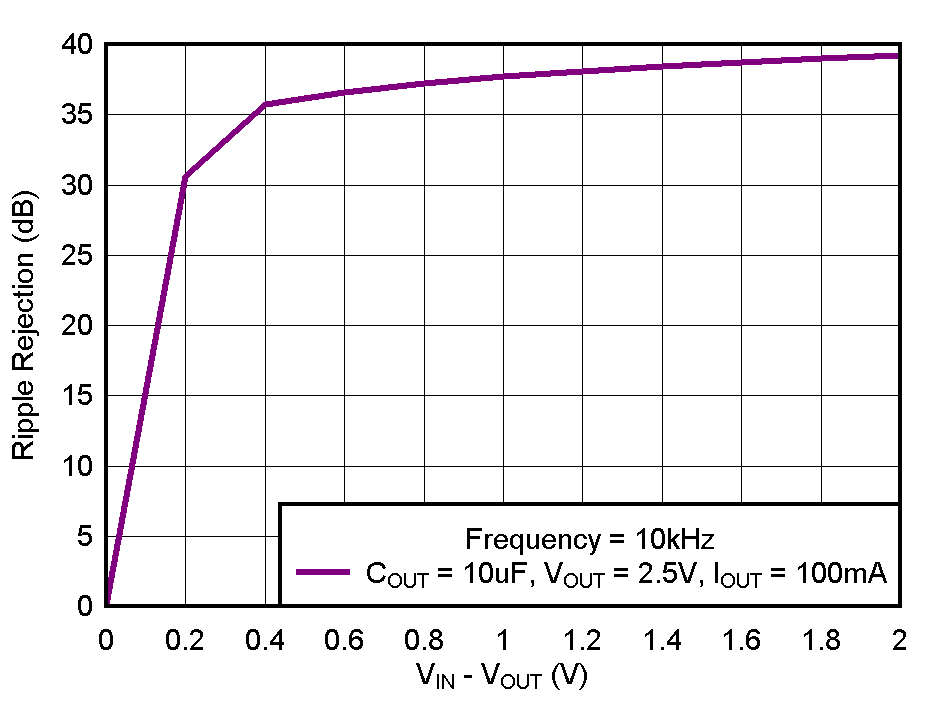

(Ripple Rejection) vs Frequency Figure 5-25 PSRR

(Ripple Rejection) vs VIN – VOUT

Figure 5-25 PSRR

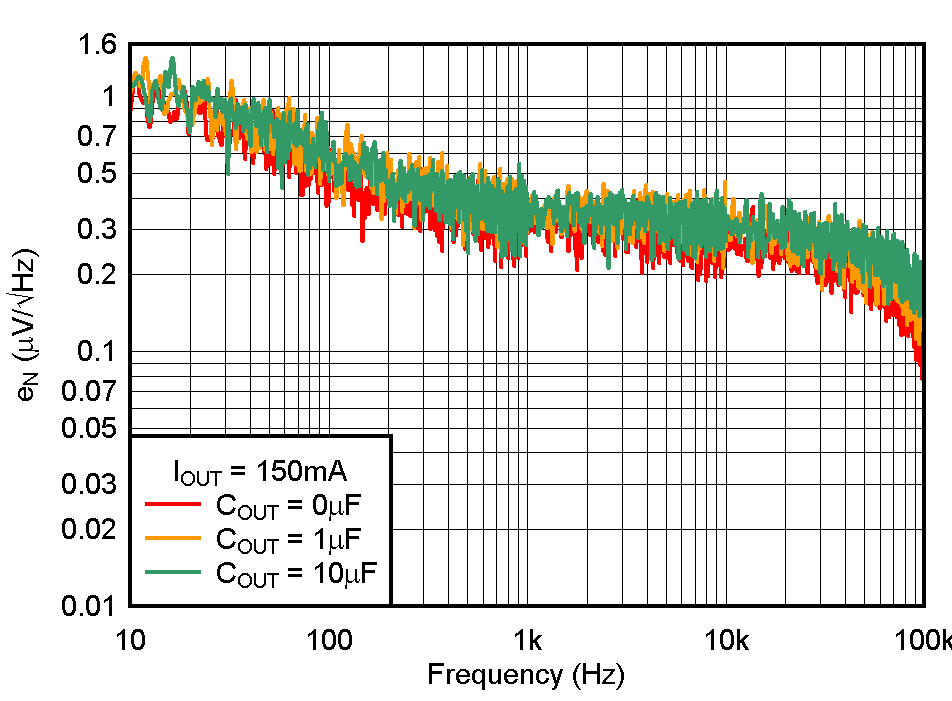

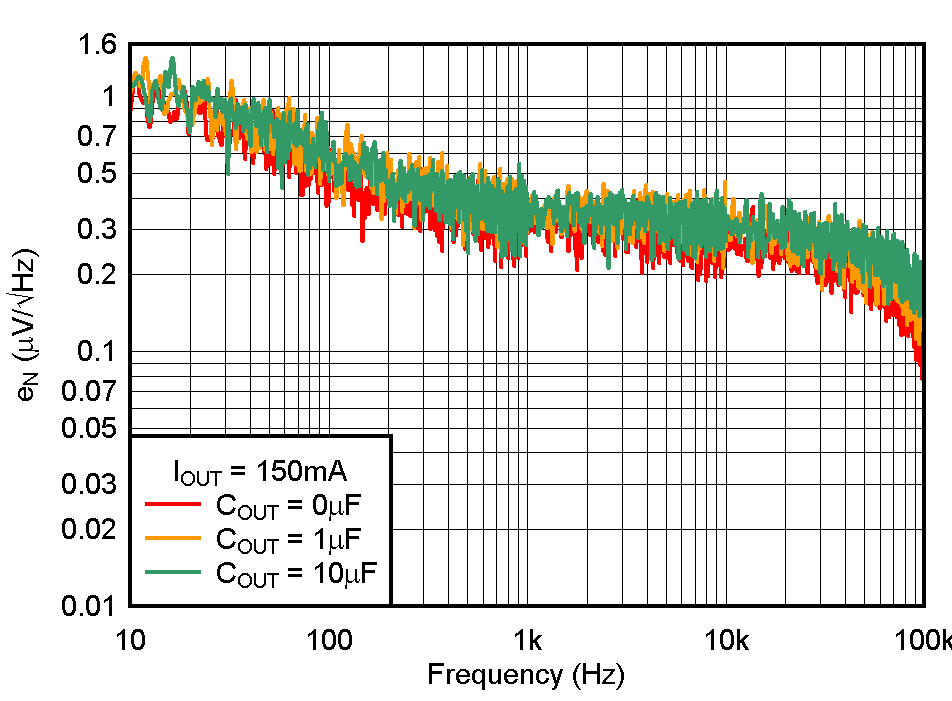

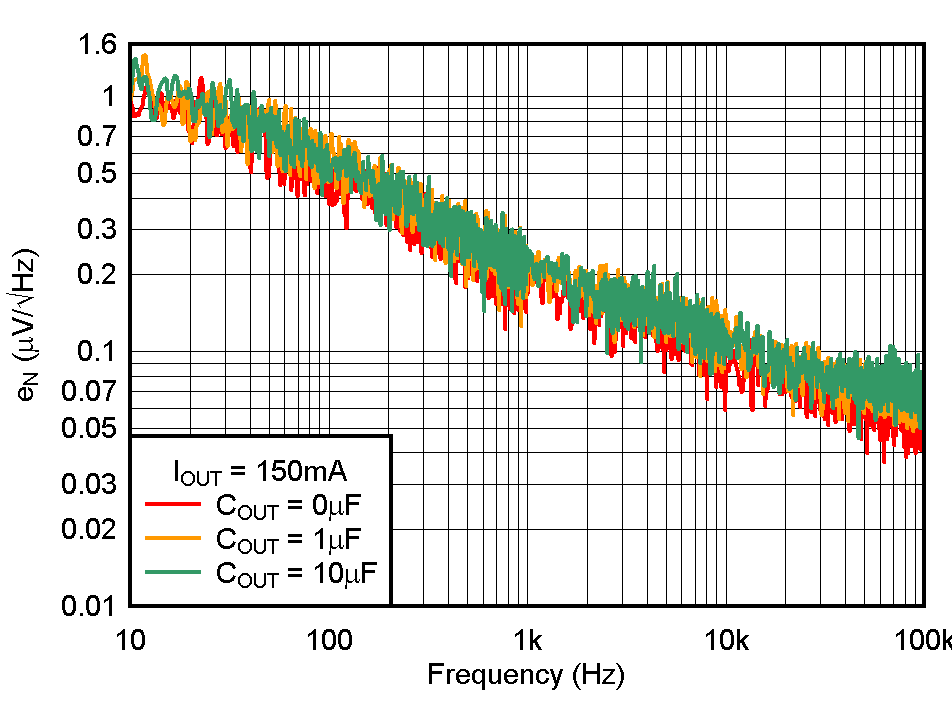

(Ripple Rejection) vs VIN – VOUT Figure 5-27 Noise

Spectral Density CNR = 0 μF

Figure 5-27 Noise

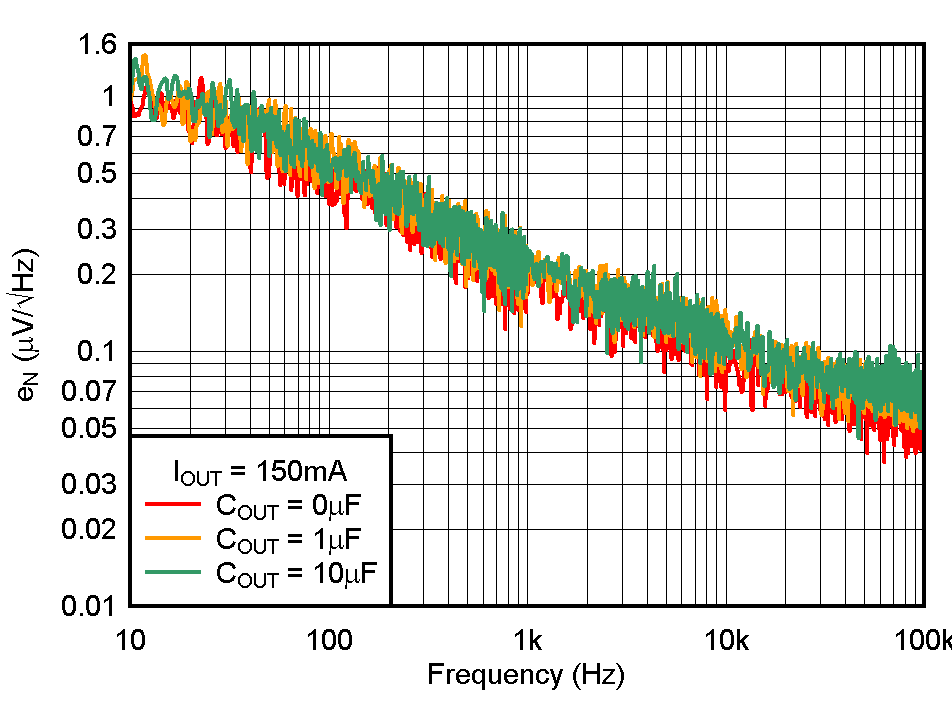

Spectral Density CNR = 0 μF Figure 5-29 Noise

Spectral Density CNR = 0.01 μF

Figure 5-29 Noise

Spectral Density CNR = 0.01 μF Figure 5-31 RMS

Noise Voltage vs COUT

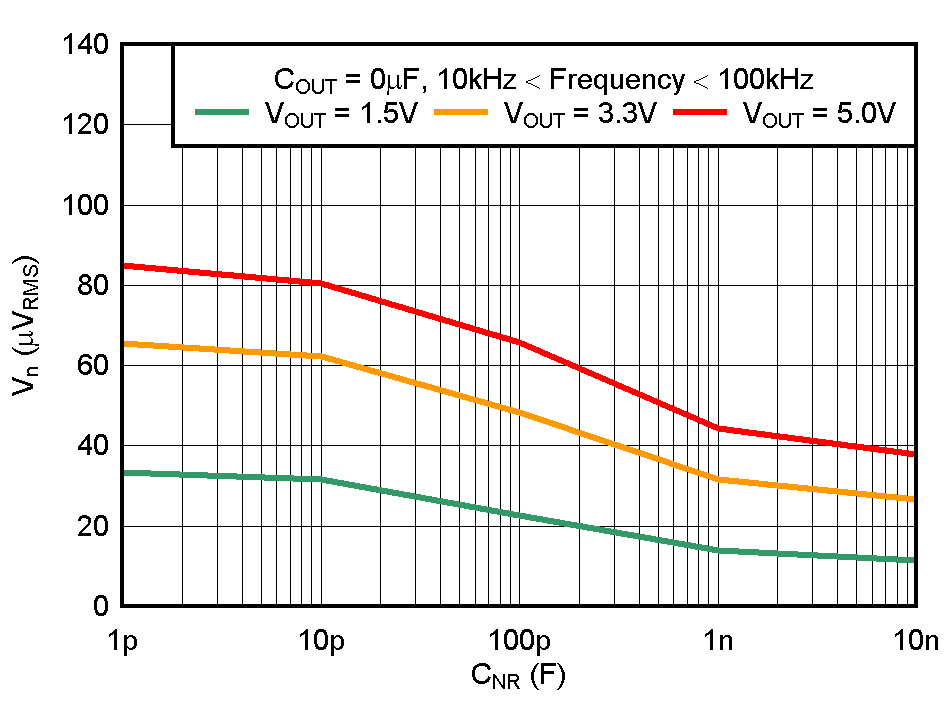

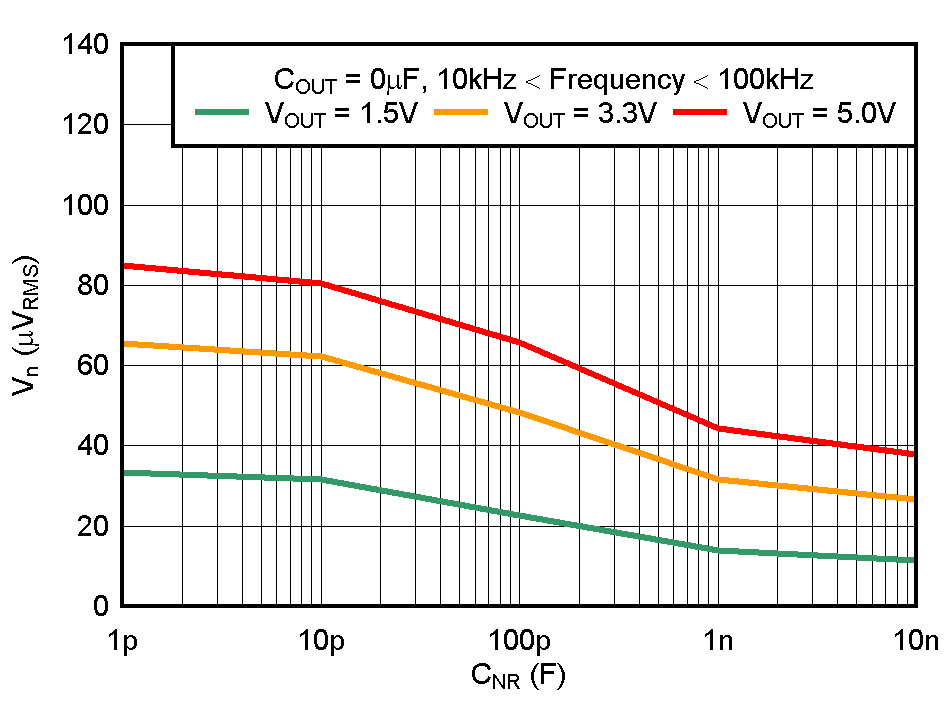

Figure 5-31 RMS

Noise Voltage vs COUT Figure 5-33 RMS

Noise Voltage vs CNR

Figure 5-33 RMS

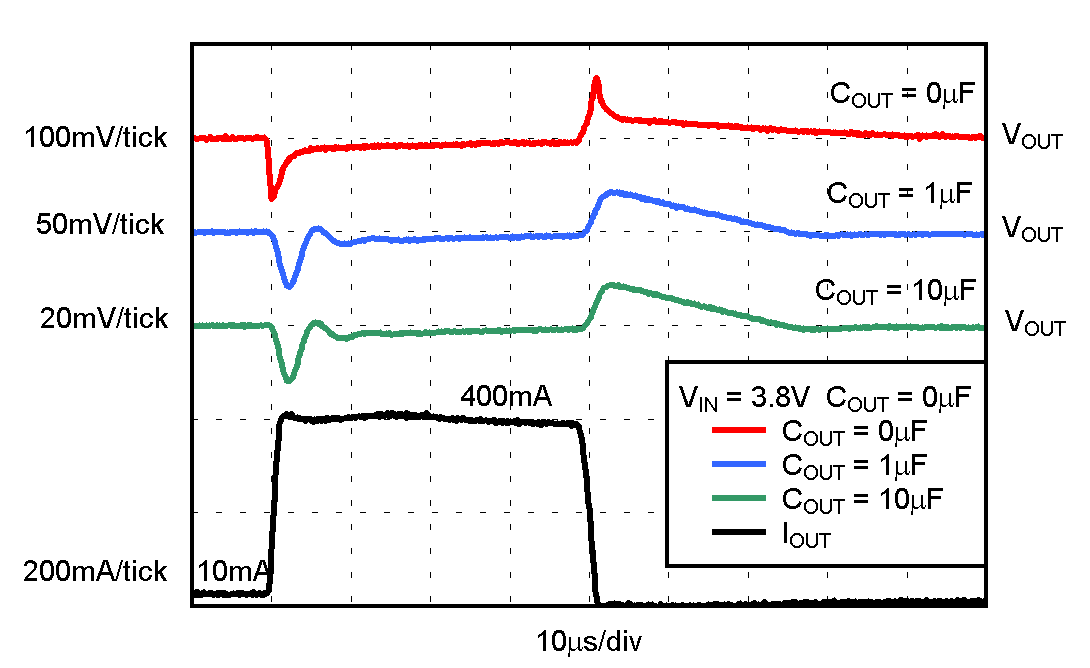

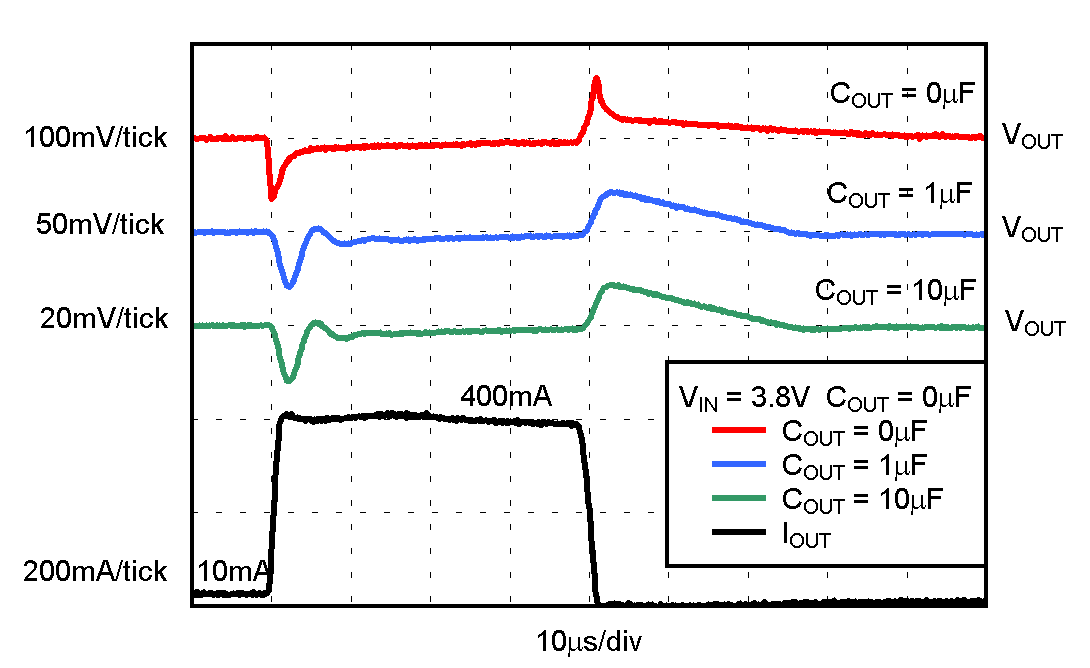

Noise Voltage vs CNR Figure 5-35 TPS73633 Load Transient Response

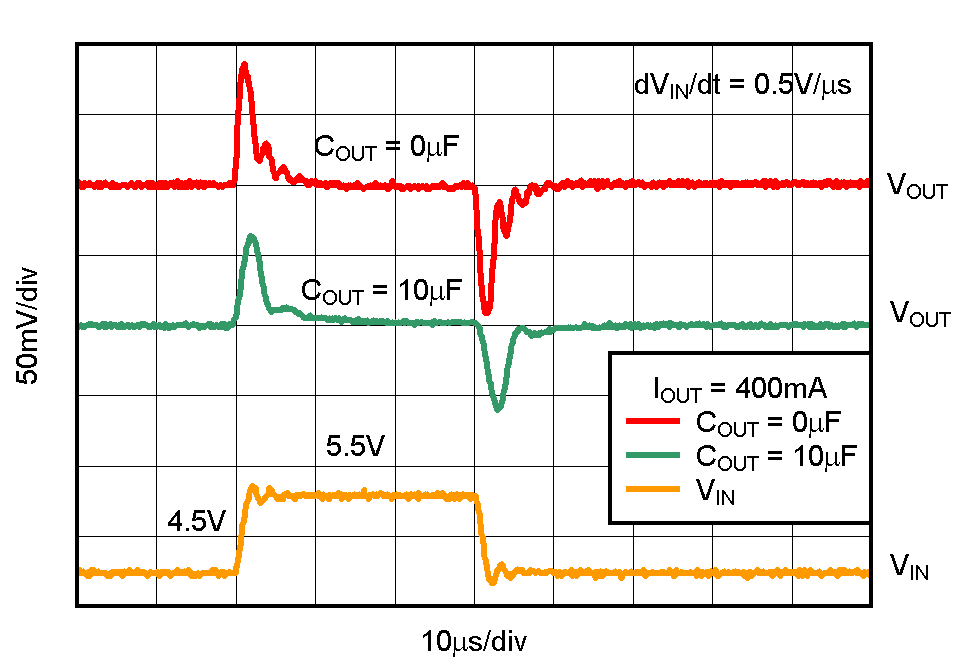

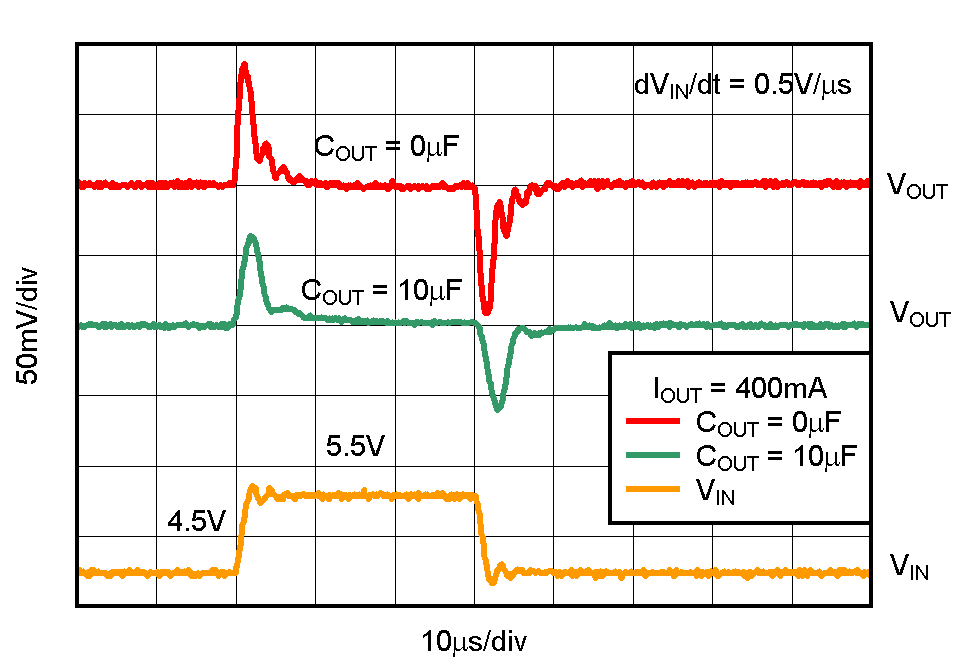

Figure 5-35 TPS73633 Load Transient Response Figure 5-37 TPS73633 Line Transient Response

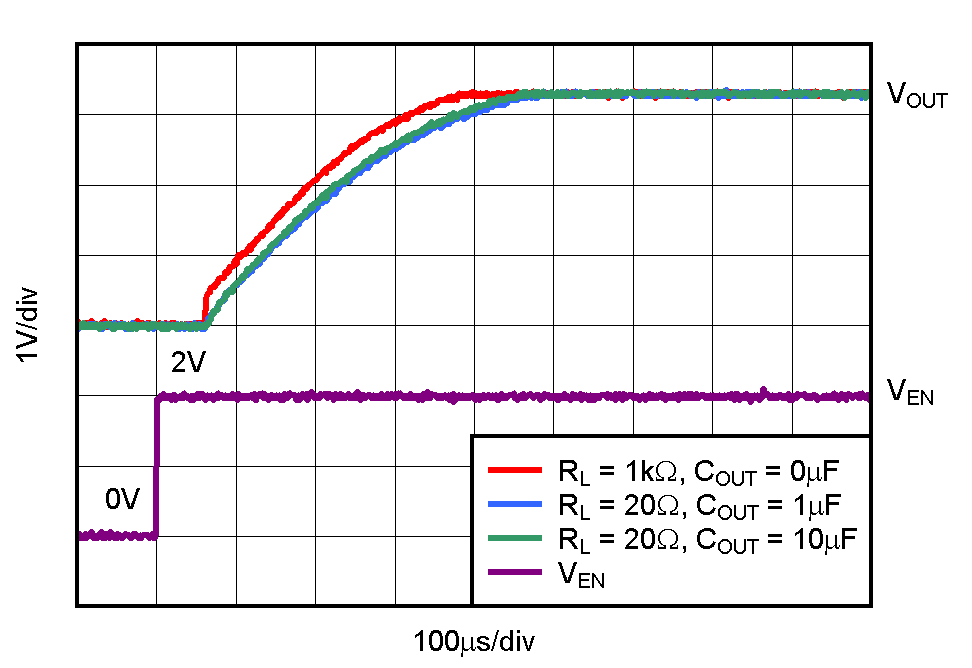

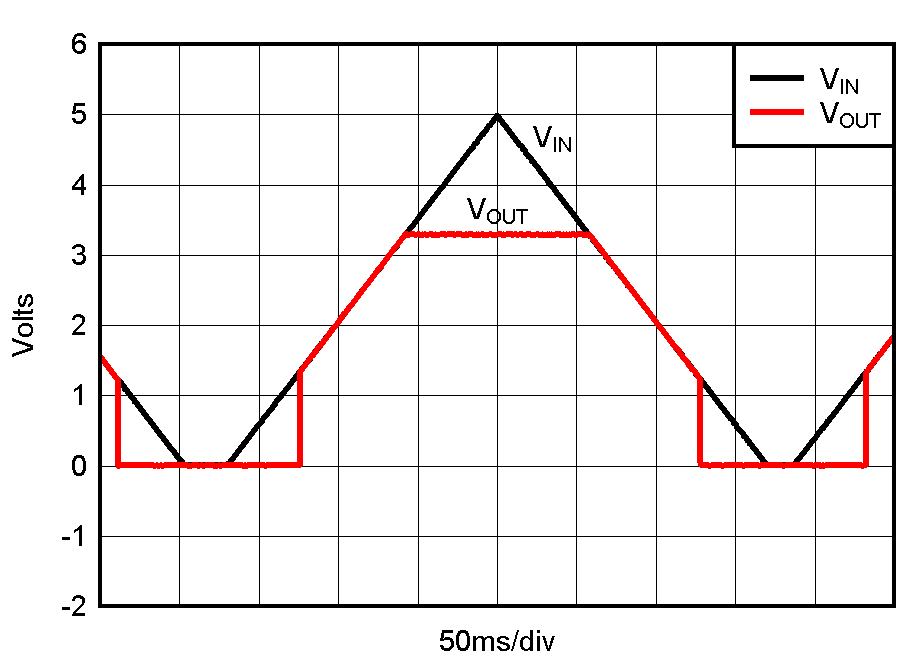

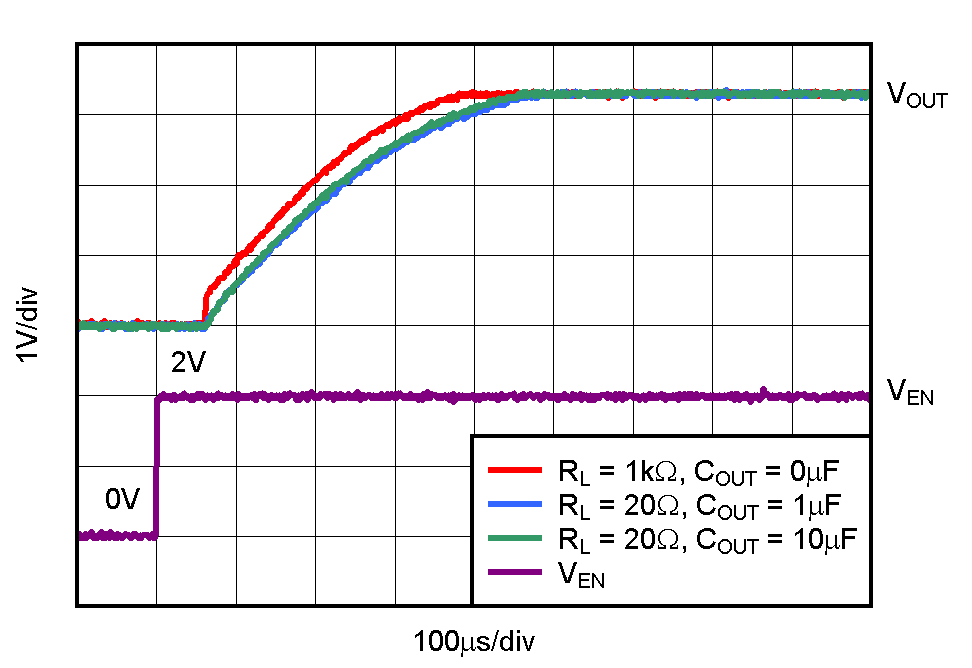

Figure 5-37 TPS73633 Line Transient Response Figure 5-39 TPS73633 Turn-On Response

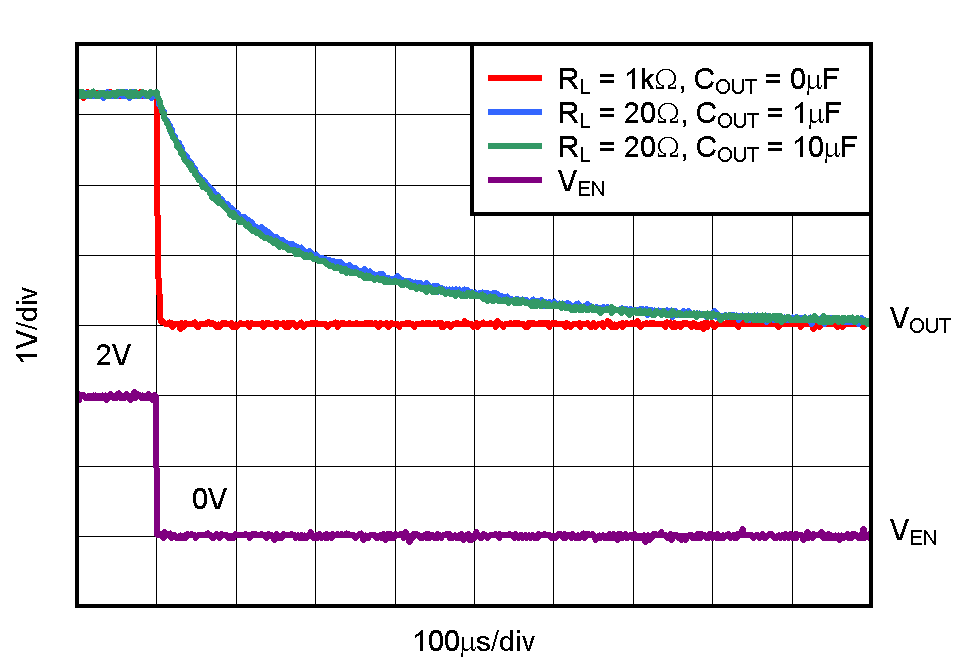

Figure 5-39 TPS73633 Turn-On Response Figure 5-41 TPS73633 Turn-Off Response

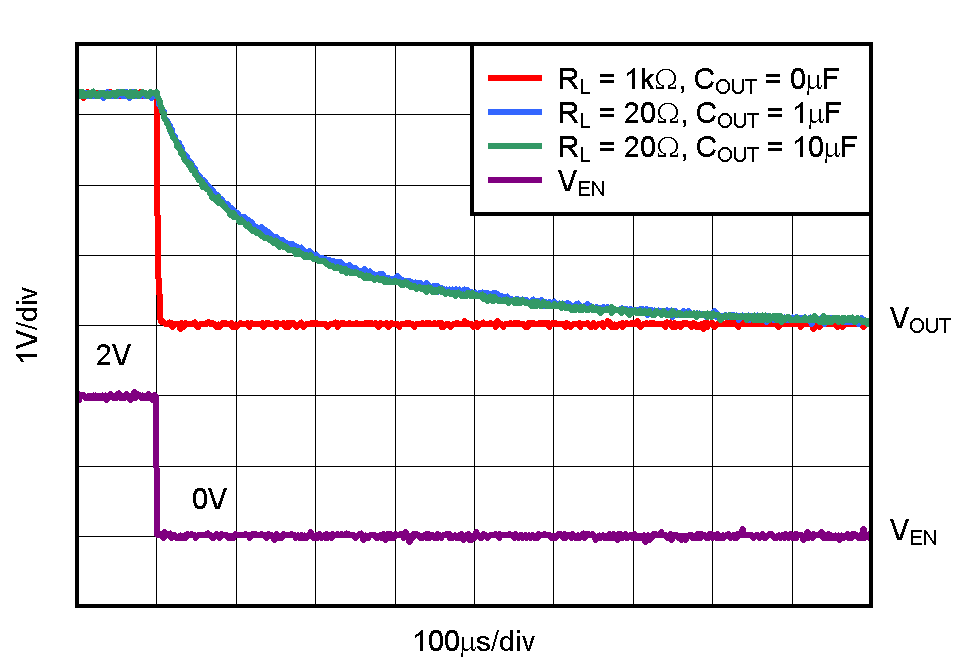

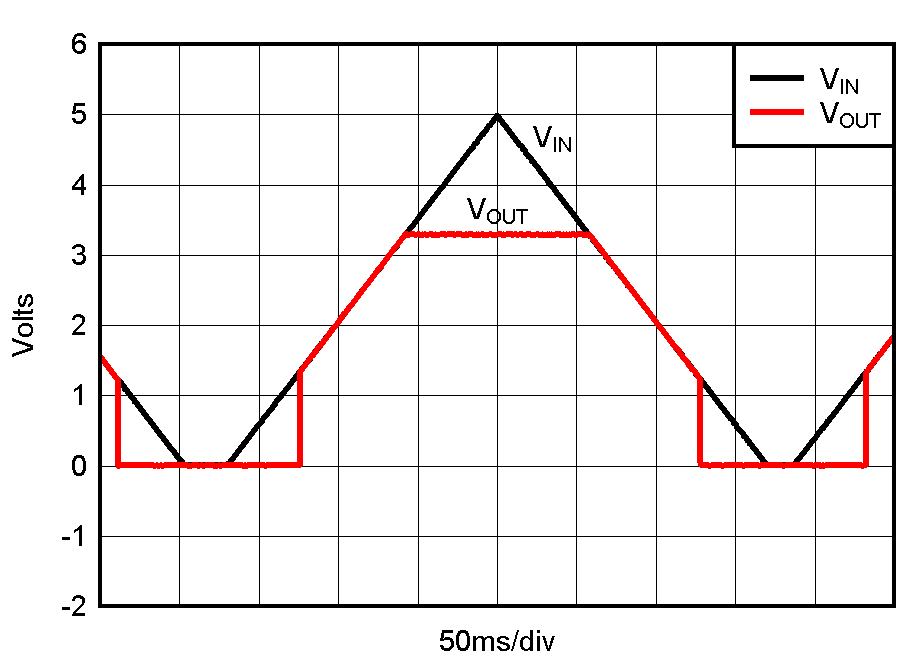

Figure 5-41 TPS73633 Turn-Off Response Figure 5-43 TPS73633 Power-Up, Power-Down

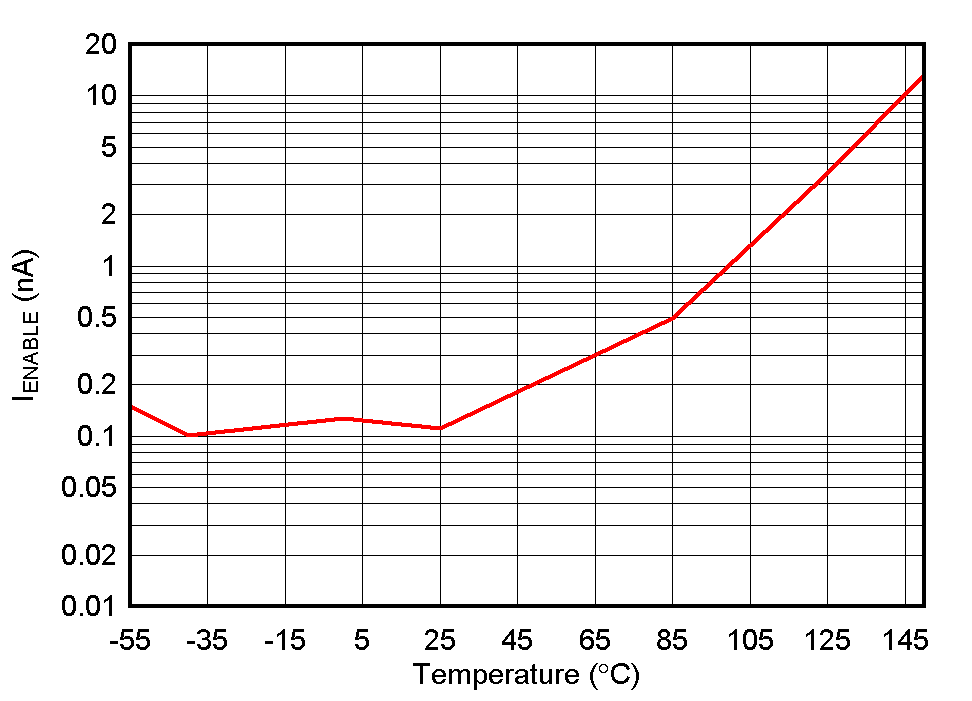

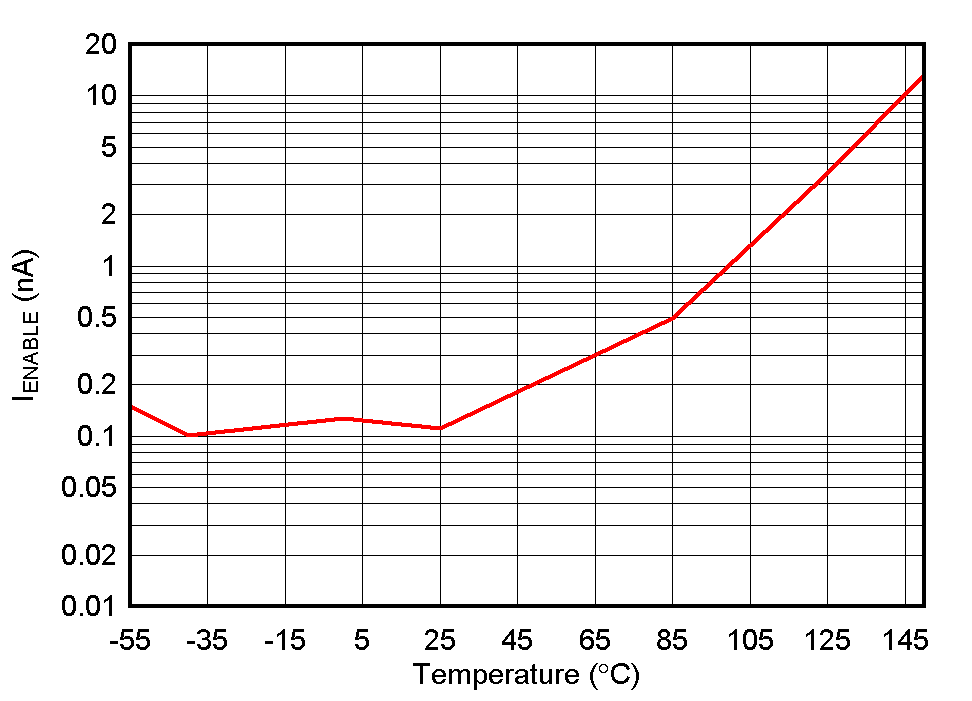

Figure 5-43 TPS73633 Power-Up, Power-Down Figure 5-45 IENABLE vs Temperature

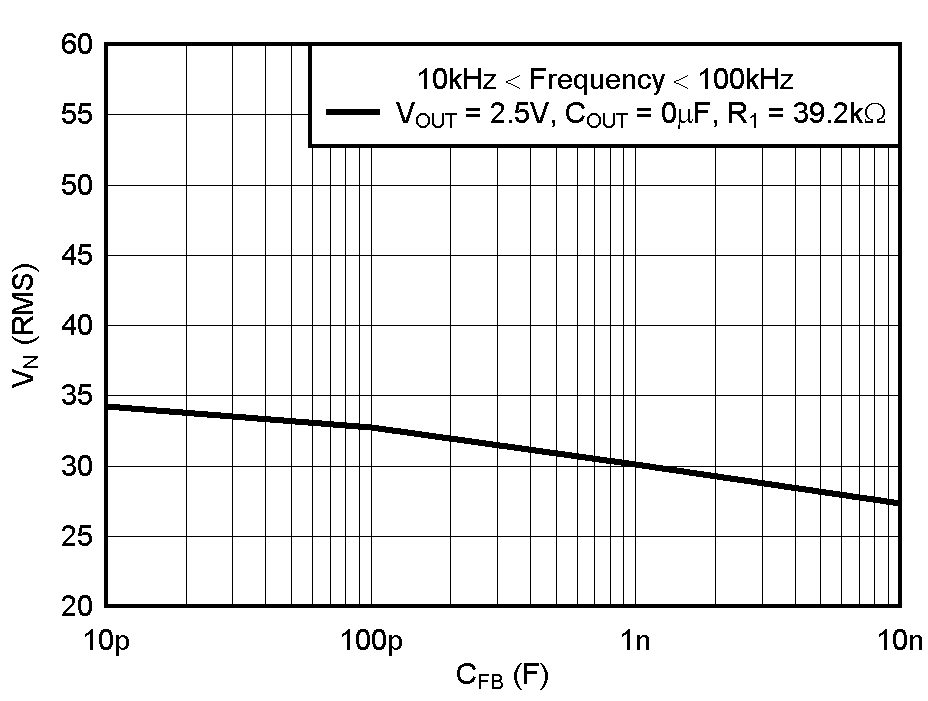

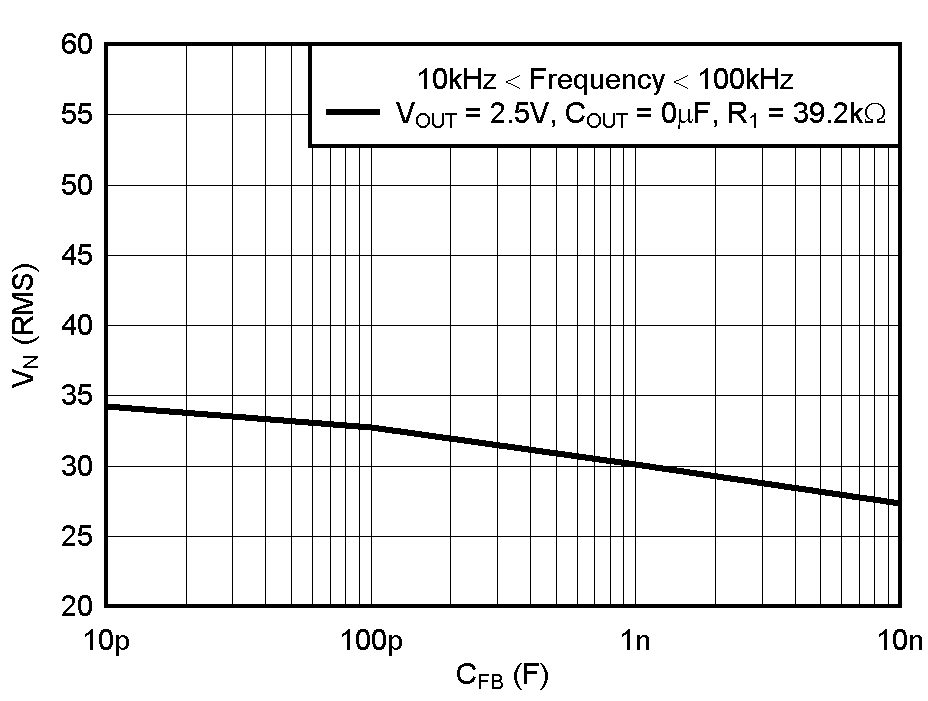

Figure 5-45 IENABLE vs Temperature Figure 5-47 TPS73601 RMS Noise Voltage vs CFB

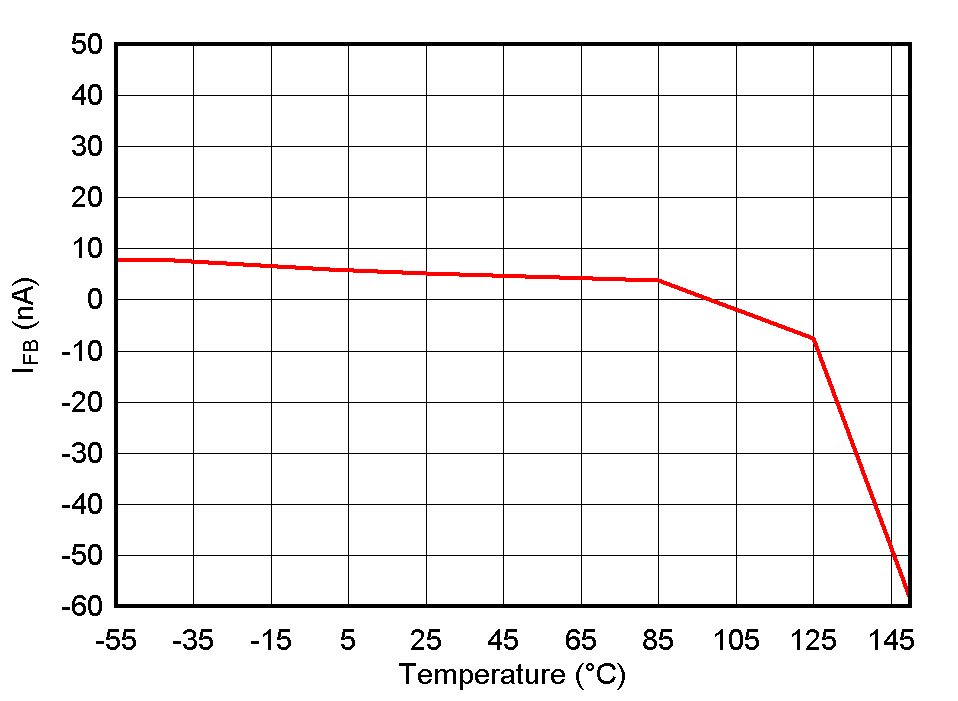

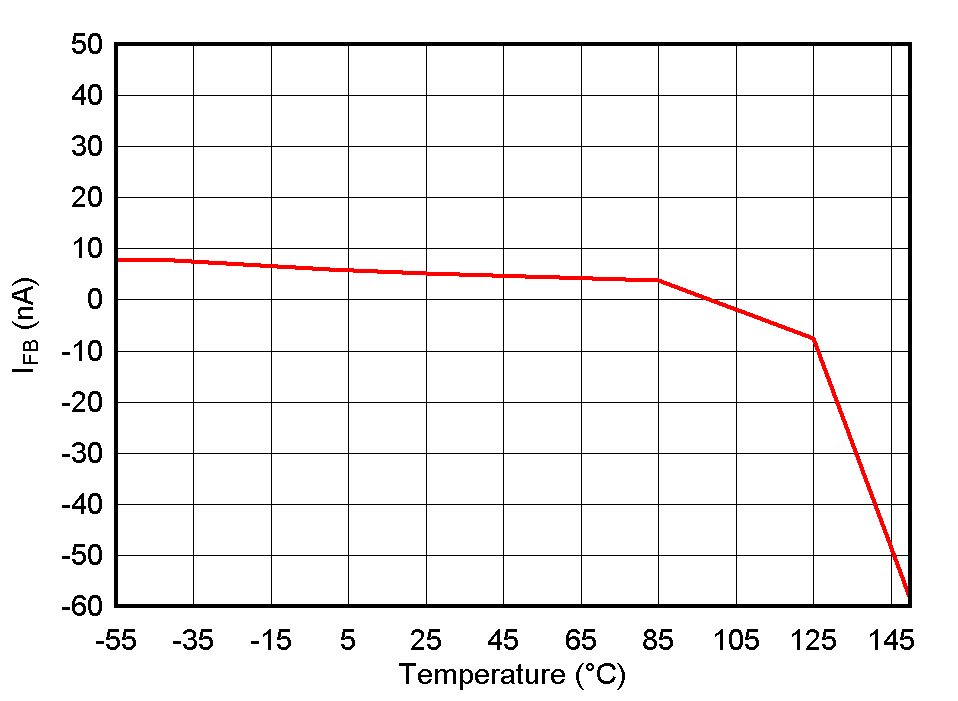

Figure 5-47 TPS73601 RMS Noise Voltage vs CFB Figure 5-49 TPS73601 IFB vs Temperature

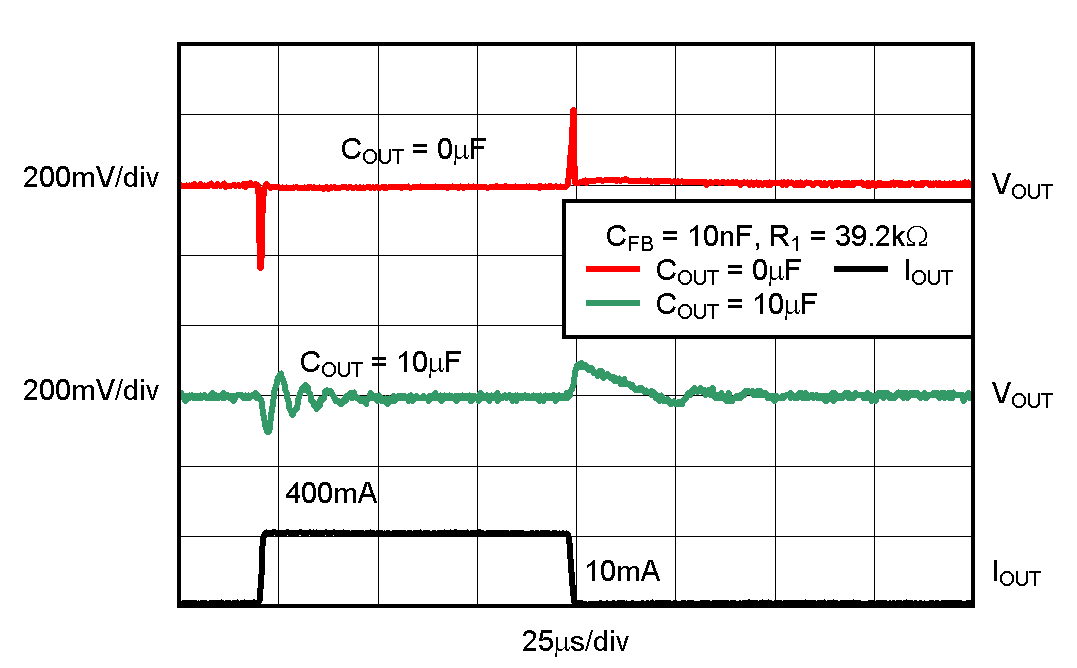

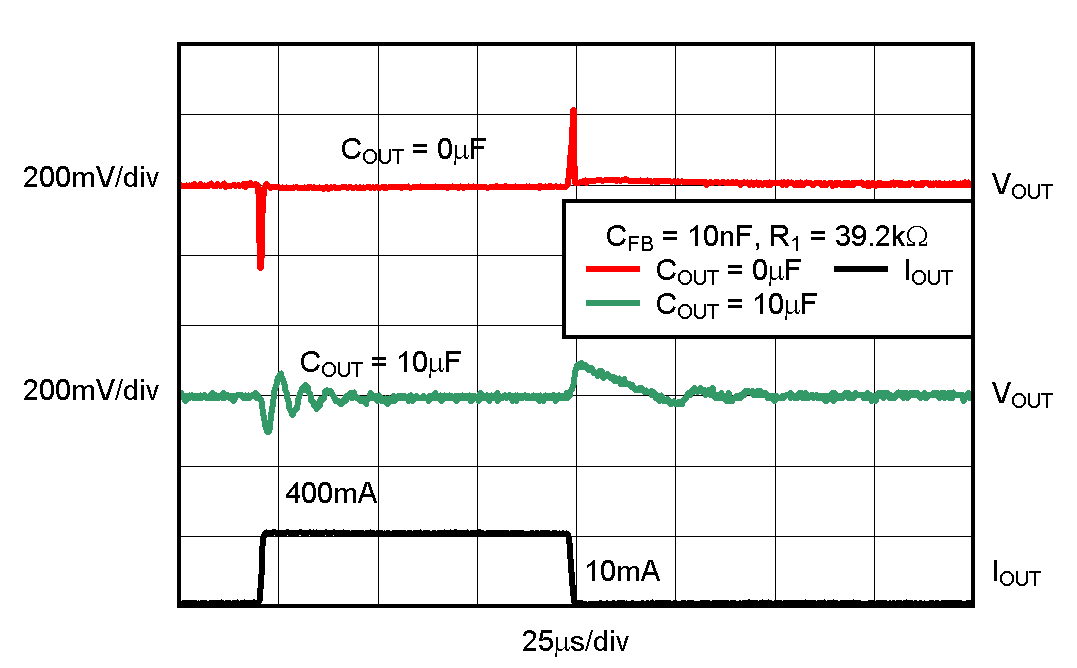

Figure 5-49 TPS73601 IFB vs Temperature Figure 5-51 TPS73601 Load Transient, Adjustable Version

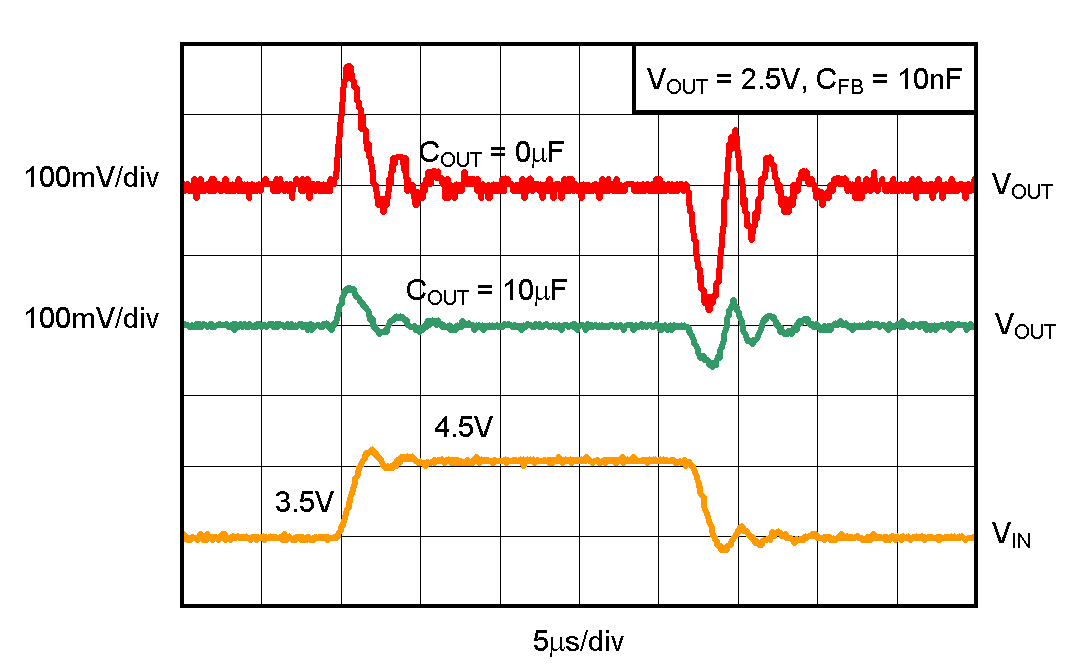

Figure 5-51 TPS73601 Load Transient, Adjustable Version Figure 5-53 TPS73601 Line Transient, Adjustable Version

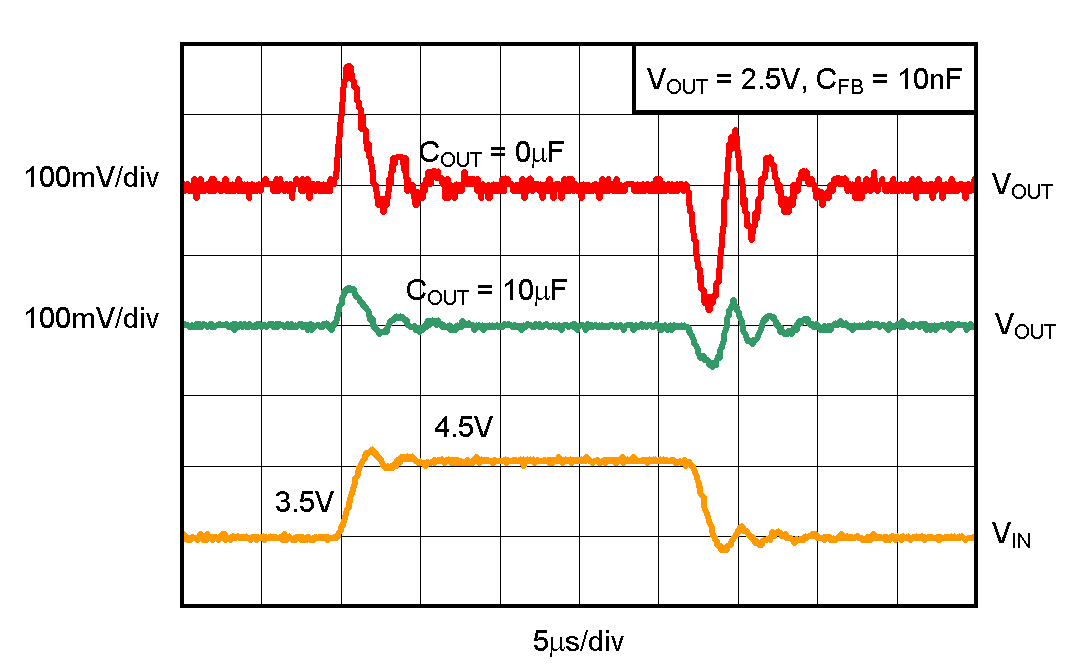

Figure 5-53 TPS73601 Line Transient, Adjustable Version Figure 5-2 Load

Regulation

Figure 5-2 Load

Regulation Figure 5-4 Line

Regulation

Figure 5-4 Line

Regulation Figure 5-6 Dropout Voltage vs Output Current

Figure 5-6 Dropout Voltage vs Output Current Figure 5-8 Dropout Voltage vs Temperature

Figure 5-8 Dropout Voltage vs Temperature Figure 5-10 Output Voltage Drift Histogram

Figure 5-10 Output Voltage Drift Histogram Figure 5-12 Ground Pin Current vs Output Current

Figure 5-12 Ground Pin Current vs Output Current Figure 5-14 Ground Pin Current vs Temperature

Figure 5-14 Ground Pin Current vs Temperature Figure 5-16 Ground Pin Current in

Shutdown vs Temperature

Figure 5-16 Ground Pin Current in

Shutdown vs Temperature Figure 5-18 Current Limit vs VOUT (Foldback)

Figure 5-18 Current Limit vs VOUT (Foldback) Figure 5-20 Current Limit vs VIN

Figure 5-20 Current Limit vs VIN Figure 5-22 Current Limit vs Temperature

Figure 5-22 Current Limit vs Temperature Figure 5-24 PSRR

(Ripple Rejection) vs Frequency

Figure 5-24 PSRR

(Ripple Rejection) vs Frequency Figure 5-26 PSRR

(Ripple Rejection) vs VIN – VOUT

Figure 5-26 PSRR

(Ripple Rejection) vs VIN – VOUT Figure 5-28 Noise

Spectral Density CNR = 0 μF

Figure 5-28 Noise

Spectral Density CNR = 0 μF Figure 5-30 Noise

Spectral Density CNR = 0.01 μF

Figure 5-30 Noise

Spectral Density CNR = 0.01 μF Figure 5-32 RMS

Noise Voltage vs COUT

Figure 5-32 RMS

Noise Voltage vs COUT Figure 5-34 RMS

Noise Voltage vs CNR

Figure 5-34 RMS

Noise Voltage vs CNR Figure 5-36 TPS73633 Load Transient Response

Figure 5-36 TPS73633 Load Transient Response Figure 5-38 TPS73633 Line Transient Response

Figure 5-38 TPS73633 Line Transient Response Figure 5-40 TPS73633 Turn-On Response

Figure 5-40 TPS73633 Turn-On Response Figure 5-42 TPS73633 Turn-Off Response

Figure 5-42 TPS73633 Turn-Off Response Figure 5-44 TPS73633 Power-Up, Power-Down

Figure 5-44 TPS73633 Power-Up, Power-Down Figure 5-46 IENABLE vs Temperature

Figure 5-46 IENABLE vs Temperature Figure 5-48 TPS73601 RMS Noise Voltage vs CFB

Figure 5-48 TPS73601 RMS Noise Voltage vs CFB Figure 5-50 TPS73601 IFB vs Temperature

Figure 5-50 TPS73601 IFB vs Temperature Figure 5-52 TPS73601 Load Transient, Adjustable Version

Figure 5-52 TPS73601 Load Transient, Adjustable Version Figure 5-54 TPS73601 Line Transient, Adjustable Version

Figure 5-54 TPS73601 Line Transient, Adjustable Version