SCDA051 June 2024 TMUXS7614D

4.1 Address Mode

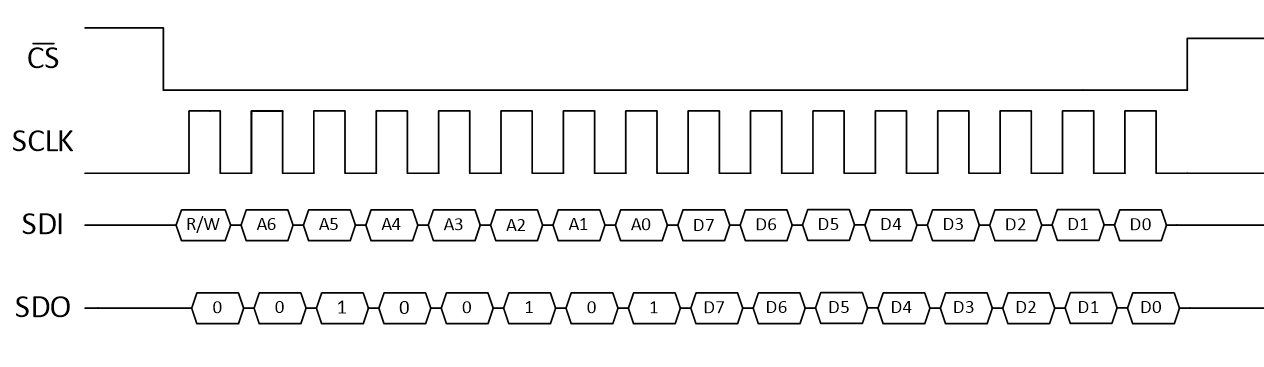

The SPI signal communication is defaulted to address mode. In that mode the registers of the mux are accessed by a 16-bit SPI command bounded by the chip select line (/CS). Other than address mode the device can operate in burst and daisy chain modes. The SPI pins are SDI, SDO, SCLK, and /CS. To send a SPI signal, CS has to be held low while the data is being captured on the SDI line when SCLK is on the rising edge. The data is sent out on the SDO line on the falling edge of SCLK. The SPI signal lanes are shown in Figure 4-1.

Figure 4-1 SPI Address Mode

Signal

Figure 4-1 SPI Address Mode

SignalThe first bit on the SDI line indicates whenever the bit is a read or write command. If the bit is 1, it is a read. If the bit is 0 then it is a write. The next seven bits are correlated to the target register address. The remaining eight bits are the data bits. The data bits contain the data being sent on the SPI signal during a write command. In a read command, the last eight bits are ignored. During the clock cycles, the SDO line sends out the data contained in the target address register. The data stored in the target register is sent out in the last eight bits on the SDO line during SCLK falling edges when the SPI reads. The SPI command can extend to a 24-bit command if the user enables CRC error detection.