SCDU026 July 2021

- Trademarks

- 1 Introduction

- 2 General Texas Instruments High Voltage Evaluation Module (TI HV EVM) User Safety Guidelines

- 3 Information About Cautions and Warnings

- 4 Features

- 5 TMUX-24PW-EVM Header Connections and Test Points

- 6 TMUX-24PW-EVM Setup

- 7 Layout

- 8 Schematics

- 9 Bill of Materials

- 10Revision History

5 TMUX-24PW-EVM Header Connections and Test Points

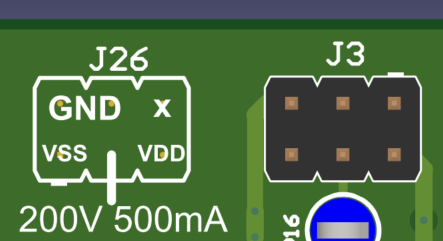

There are 24 headers located around the board with designators J1 through J24. These 3-by-2 headers serve as connections to power planes and to signals of the DUT (U1). Each pin of the DUT has similar header and test point configuration. At four different locations around the board, a legend shows the connections of the pins of the nearby five headers. Figure 5-1 shows a representation of the header associated with pin 3 of U1.

Figure 5-1 Header J3 for U1.3

Figure 5-1 Header J3 for U1.3The silkscreen legend represents the connections of the pins of J3. Figure 5-2 shows the pin numbers of this header from this same perspective.

Figure 5-2 Pinout of Headers

Figure 5-2 Pinout of HeadersTable 5-1 also shows the connections.

| Header pin number | Connection |

|---|---|

| 1 | No connection |

| 2 | VDD |

| 3 | GND |

| 4 | U1 |

| 5 | GND |

| 6 | VSS |

For all headers J1 through J24, the connections are the same, but are rotated by a multiple of 90° according to their position on the board. A legend is included for each rotation.

In addition to headers, multiple test points are located around the board. Black test points (TP2 and TP4-TP11) are connected to GND, the red test point (TP1) is connected to VDD, and the green test point (TP3) is connected to VSS. The remaining blue test points (TP12-TP59) are connected along the signal paths of the pins of U1.

Figure 5-3 Test Point Colors

Figure 5-3 Test Point ColorsTable 5-2 shows the test point connections.

| Designator | Connection |

|---|---|

| TP1 | VDD |

| TP2 | GND |

| TP3 | VSS |

| TP4 | GND |

| TP5 | GND |

| TP6 | GND |

| TP7 | GND |

| TP8 | GND |

| TP9 | GND |

| TP10 | GND |

| TP11 | GND |

| TP12 | J1.4 |

| TP13 | U1.1 |

| TP14 | J2.4 |

| TP15 | U1.2 |

| TP16 | J3.4 |

| TP17 | U1.3 |

| TP18 | J4.4 |

| TP19 | U1.4 |

| TP20 | J5.4 |

| TP21 | U1.5 |

| TP22 | J6.4 |

| TP23 | U1.6 |

| TP24 | J7.4 |

| TP25 | U1.7 |

| TP26 | J8.4 |

| TP27 | U1.8 |

| TP28 | J9.4 |

| TP29 | U1.9 |

| TP30 | J10.4 |

| TP31 | U1.10 |

| TP32 | J11.4 |

| TP33 | U1.11 |

| TP34 | J12.4 |

| TP35 | U1.12 |

| TP36 | J13.4 |

| TP37 | U1.13 |

| TP38 | J14.4 |

| TP39 | U1.14 |

| TP40 | J15.4 |

| TP41 | U1.15 |

| TP42 | J16.4 |

| TP43 | U1.16 |

| TP44 | J17.4 |

| TP45 | U1.17 |

| TP46 | J18.4 |

| TP47 | U1.18 |

| TP48 | J19.4 |

| TP49 | U1.19 |

| TP50 | J20.4 |

| TP51 | U1.20 |

| TP52 | J21.4 |

| TP53 | U1.21 |

| TP54 | J22.4 |

| TP55 | U1.22 |

| TP56 | J23.4 |

| TP57 | U1.23 |

| TP58 | J24.4 |

| TP59 | U1.24 |

Terminal block J25 is the power input for the board. Three power rails (VSS, GND, and VDD) are labeled on the board’s silkscreen layer, indicating the identities of the input pins of the header. Connect the power supply rails at this terminal block to power the board.