SCEA117 July 2022 SN74HCS164 , SN74HCS164-Q1 , SN74HCS165 , SN74HCS165-Q1 , SN74HCS595 , SN74HCS595-Q1

3.2 System Design

A hierarchical design is being used to more easily show this relatively large-scale system design. See Figure 3-1 for the top-level system block diagram. The LED Panel boards are labelled numerically in the order that the data is propagating through the system. The clock propagates in the reverse order, arriving at board six first, then travelling back to board five and so on. The order of the clock arrival is indicated by arrows in the block diagram.

Each LED panel board contains 12 shift registers, split into two banks of six for the clock signals. See Figure 3-2 for an illustration of how these are connected. The incoming clock signals are first buffered by B1 and B2, each of which drives six total CMOS inputs. This equates to approximately 35 pF of total load capacitance. The trace capacitance also needs to be estimated, which is approximately 22 pF.1 This gives a total capacitive load of 57 pF, which is a bit higher than the load at which the datasheet specifications are measured, but not so much that it would be considered an area of concern.2

| Time (ns) | Event |

|---|---|

| 0.0 | Clock edge (CLK) is generated |

| 3.3 | CLK arrives at LED Panel 6, triggering input buffer B1 |

| 13.2 | CLK is generated at the output of buffer B1 |

| 13.3 | CLK arrives at input of buffer B2 |

| 15.2 | CLK has reached all 6 of the shift registers U7 to U12, loading all SER inputs |

| 23.2 | CLK is generated at the output of buffer B2 |

| 23.3 | CLK arrives at the input of buffer B3 |

| 25.0 | Shifted values appear at QH' outputs for registers U7 to U12 |

| 25.2 | CLK has reached all 6 of the shift registers U1 to U6, loading all SER inputs |

| 33.2 | CLK is generated to send to the next board |

| 35.0 | Shifted values appear at QH' outputs for registers U1 to U6 |

It takes approximately 21.7 ns from the time a clock signal is received at a given set of shift registers to the time the shifted data is available to be read by the following board in the chain. This value gives a good idea of the maximum operating frequency, as calculated in Equation 2.

| Time (ns) | Event |

|---|---|

| 0.0 | Serial clock edge (CLK) is generated Serial data edge (DATA) is generated |

| 3.3 | CLK arrives at LED Panel 6, triggering input buffer

B1 DATA arrives at LED Panel 1, now waiting to be loaded into U1 |

| 33.2 | CLK is generated from B3 to send to LED Panel 5 |

| 36.5 | CLK arrives at LED Panel 5, triggering input buffer B1 |

| 66.4 | CLK is generated from B3 to send to LED Panel 4 |

| 69.7 | CLK arrives at LED Panel 4, triggering input buffer B1 |

| 99.6 | CLK is generated from B3 to send to LED Panel 3 |

| 102.9 | CLK arrives at LED Panel 3, triggering input buffer B1 |

| 132.8 | CLK is generated from B3 to send to LED Panel 2 |

| 136.1 | CLK arrives at LED Panel 2, triggering input buffer B1 |

| 166.0 | CLK is generated from B3 to send to LED Panel 1 |

| 169.3 | CLK arrives at LED Panel 1, triggering input buffer B1 |

| 191.2 | CLK arrives at the last set of shift registers (U1 to U6), loading DATA into SER |

In theory, this system of shift registers could be driven at 46 MHz without any issues, however our system has a maximum operating speed of 1 MHz (from the system requirements), and our desired refresh rate won’t require such a high speed. Additionally, operating beyond 5 MHz (200 ns per clock pulse) would complicate loading of data as the serial data signal would have to be delayed based on the total time it takes the clock to propagate through the system to reach the first set of shift registers (U1 to U6) on LED Panel 1.

To load all 576 registers in under 33.3 ms, the clock speed must be at least 17.3 kHz ( ). This works out very well for our system, as we can load in data much faster than this and have RCLK control the output timing precisely.

The clock speed of 100 kHz is selected for SRCLK, loading all 576 registers in approximately 5.76 ms, which allows plenty of time for additional processing, if necessary, and RCLK can be separately timed to send the loaded data to the outputs every 33.3 ms. This speed also allows time for data to be set for each clock pulse without concern for matching propagation delays. In other words, the clock will completely propagate through the system in under 200 ns, as shown in Table 3-2, while the period of the clock is 10 μs, providing over 9.8 μs of buffer time to set the serial data input value. Table 3-2 shows the data arriving at the same time as the clock is generated, which provides a setup time of 187.9 ns – far more than is necessary for correct operation of the device. According to the datasheet, only 71 ns is necessary for operation at 3.3 V.3

The last area of concern is reading the configuration data in from the SN74HCS165 parallel-in shift register. Figure 3-3 shows the selected configuration for the serial-in shift register to reduce the total number of pins required at the controller. RCLK and SRCLK are shared with the SH/LD and CLK pins, respectively.

Each switch includes a simple RC debounce circuit with values of 22 kΩ and 1 μF for each respective component. The slow edge produced by this debounce circuit would normally need to be put through signal conditioning prior to reaching a standard CMOS input, however the SN74HCS165 includes Schmitt-trigger inputs that support slow signals, so no additional circuitry is required.

In this configuration, the switch states can either be read in during the write operation of the other shift registers, or it can be read in separately. For the sake of this imagined system, the switch states will be read in at the same time that the first eight outputs bits are being written to the parallel-out shift registers.

By keeping RCLK in the normally high state, the data in the SN74HCS165 can be loaded every time RCLK is pulsed, and the data can be read in with the first eight clock pulses of SRCLK. Although this is a very effective and efficient use of GPIO pins, there is one drawback to this configuration. The software required to read in and write out data simultaneously is slightly more complex than that required to do these tasks separately. In some systems, it may be beneficial to perform these tasks separately. See Section 2.5 and Section 3.3 for details regarding the software required for this system.

Since each board is separated by 50-cm long transmission lines, source-terminating resistors are used to prevent reflections from causing issues. The output of the LVC logic family buffers used is expected to provide approximately 15 ohms of source impedance. A perfect match is not possible or necessary4, so the common value of 100 ohms is selected to match this to the 120 ohm characteristic impedance transmission lines.

- The calculator at https://technick.net/tools/impedance-calculator/microstrip/ was used to estimate the capacitance using the following values: W = 0.000203 m, H = 0.00025 m, T = 0.0000348 m, Er = 4.2

- All capacitors will cause a large transient output current initially, which will taper off after a short time. Since the device is characterized with a particular load, that value can definitely be used safely, however there is an unspecified value that can cause damage. It is recommended to add a series resistor to limit current and avoid damage if the capacitive load is too large. For a good rule of thumb, don’t go past 150% of the maximum load in the switching characteristics table without adding a series limiting resistor. For most devices, this means 75 pF is the maximum direct capacitive load.

- Timing requirement for 3.3-V supply is estimated using linear interpolation from the existing 2-V and 4.5-V supply data.

- The output of a CMOS device is not a constant value of resistance. It can vary with temperature, process, supply voltage, and output voltage.

Each 595 Block contains eight LEDs as shown in Figure 3-4, each with an individually selected resistor to limit the current through that LED to the appropriate value. For example, with a 2.2-V forward voltage, a resistor value of 732 Ω is selected to get 1.5 mA of current.

The eight LEDs for each SN74HCS595 device will draw less than 16 mA total, which is safely below the total maximum current for the device (70 mA). Shift registers can be used to control LEDs that require more current, however additional LED driver circuitry may be necessary if more than 8.75 mA per channel (70 mA total) is required.

Each LED board is small enough that the delays are negligible between the shift registers on that board.

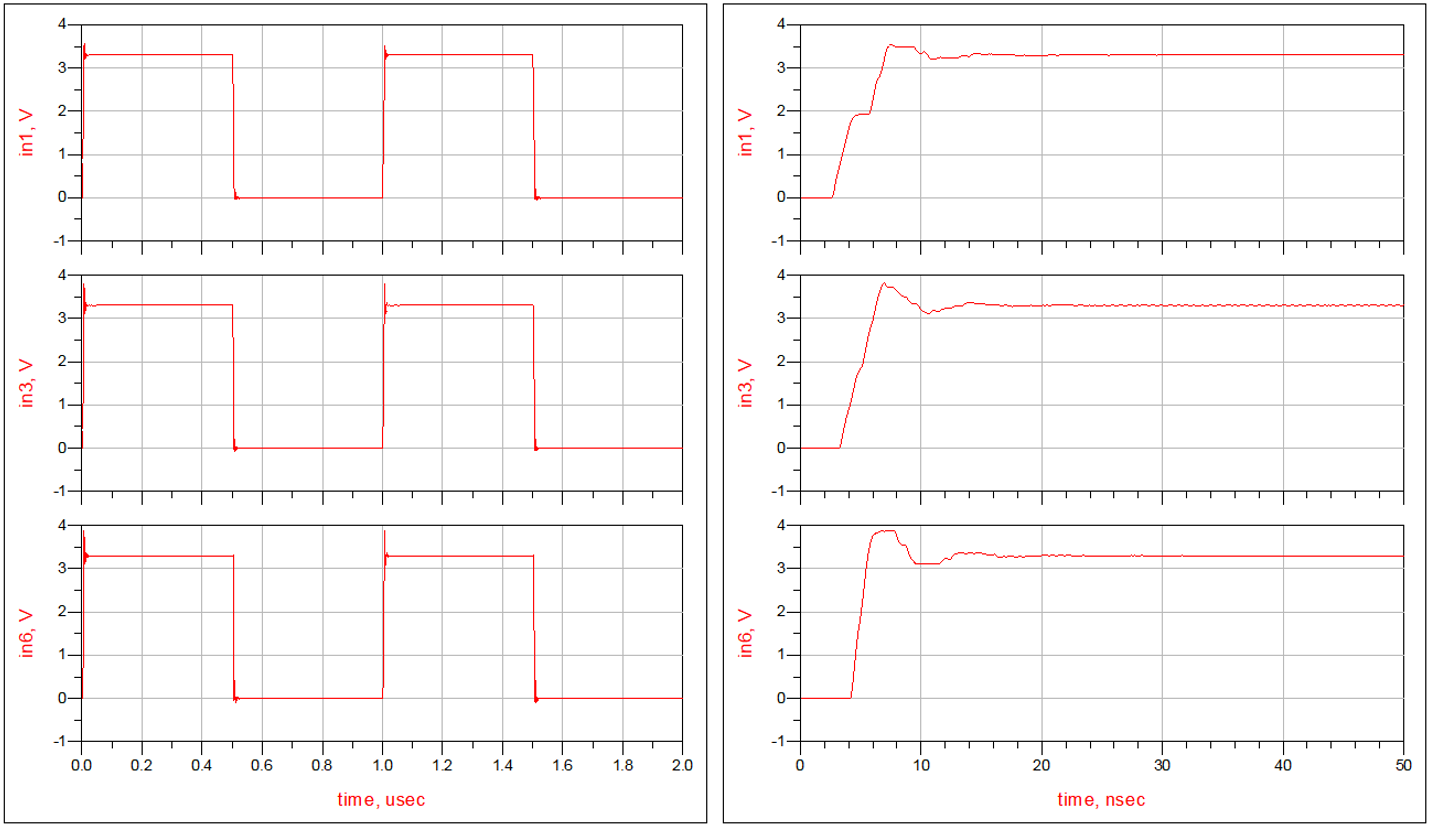

Figure 3-5 (left) Simulated Clock

Waveforms Received by the First, Third, and Sixth Shift Registers. (right)

Zoomed in Versions of the Same Three Waveforms to More Clearly Show the Rising

Edges.

Figure 3-5 (left) Simulated Clock

Waveforms Received by the First, Third, and Sixth Shift Registers. (right)

Zoomed in Versions of the Same Three Waveforms to More Clearly Show the Rising

Edges.Figure 3-2 shows how the signals are routed on the LED boards.

Figure 3-5 shows the expected signal integrity at each clock input. Due to the short traces involved, there is little distortion or delay and the devices would be expected to operate normally.