SCEU027B November 2023 – October 2024 TPLD1201

PRODUCTION DATA

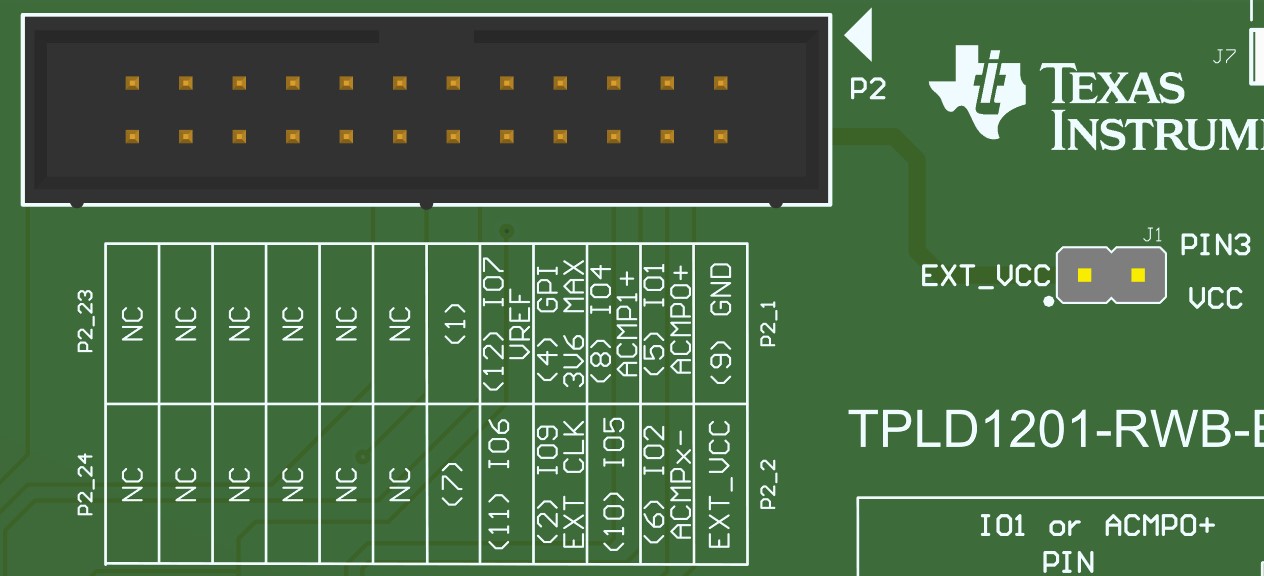

2.1.3 External Connection Header Block

The P2 header block is intended to be used to interface the TPLD1201-RWB-EVM with an external system. Using the guide printed on the EVM silkscreen, the TPLD pins can be interfaced with an external system to allow for prototyping and testing in customer systems. When supplying power to the TPLD using the P2 header block, SW3 needs to be in the OFF position and a shunt placed on J1, connecting the external VCC supply from P2 (VCC_EXT) to the VCC net of the EVM. TI recommends not connecting the board to an external system and to the TPLD-PROGRAM at the same time to avoid the risk of damage to the TPLD-PROGRAM and the external system.

Figure 2-1 P2 and J1 Headers

Figure 2-1 P2 and J1 Headers