SCLA075 August 2024 TPLD1201 , TPLD1201-Q1 , TPLD1202 , TPLD1202-Q1

1

What is a Window Comparator?

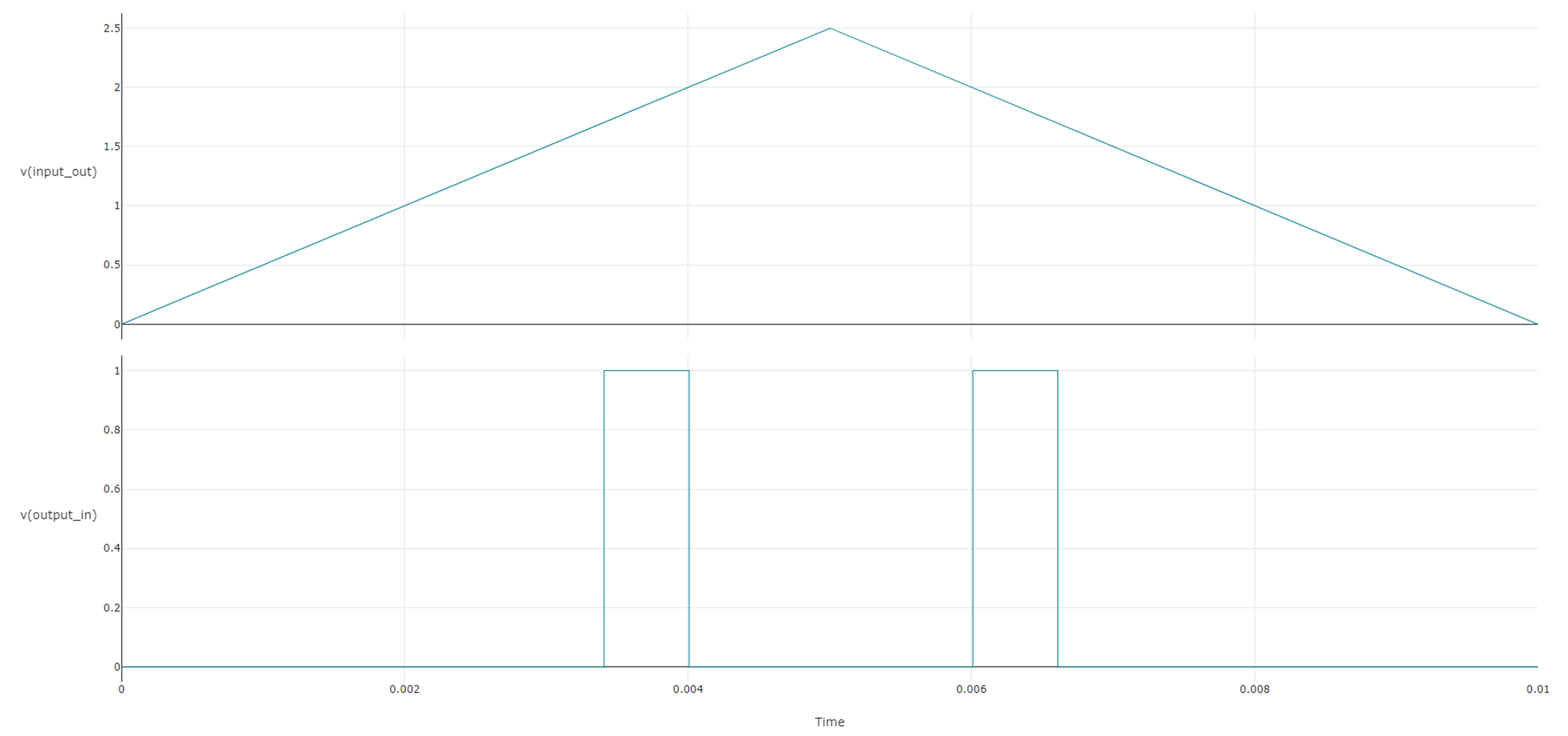

Window comparators trigger when the input voltage is within a range of voltages, as opposed to above or below a single voltage. An example of the behavior of a window comparator is shown in Figure 1. When the input voltage is above 1.7V and below 2V, the window comparator outputs high, and otherwise, it outputs low.

Figure 1 Behavior of a Window Comparator in InterConnect Studio (ICS)

Figure 1 Behavior of a Window Comparator in InterConnect Studio (ICS)Window comparators are used in a wide array of applications, including temperature sensing and signal processing. They are often used in conjunction with logical elements to manage the output signal. Using TI Programmable Logic Devices (TPLD) , the window comparator and signal handling elements can be combined into a single chip solution, reducing the board space requirements and simplifying the BOM of the system.

How to Configure a Window Comparator in TPLD

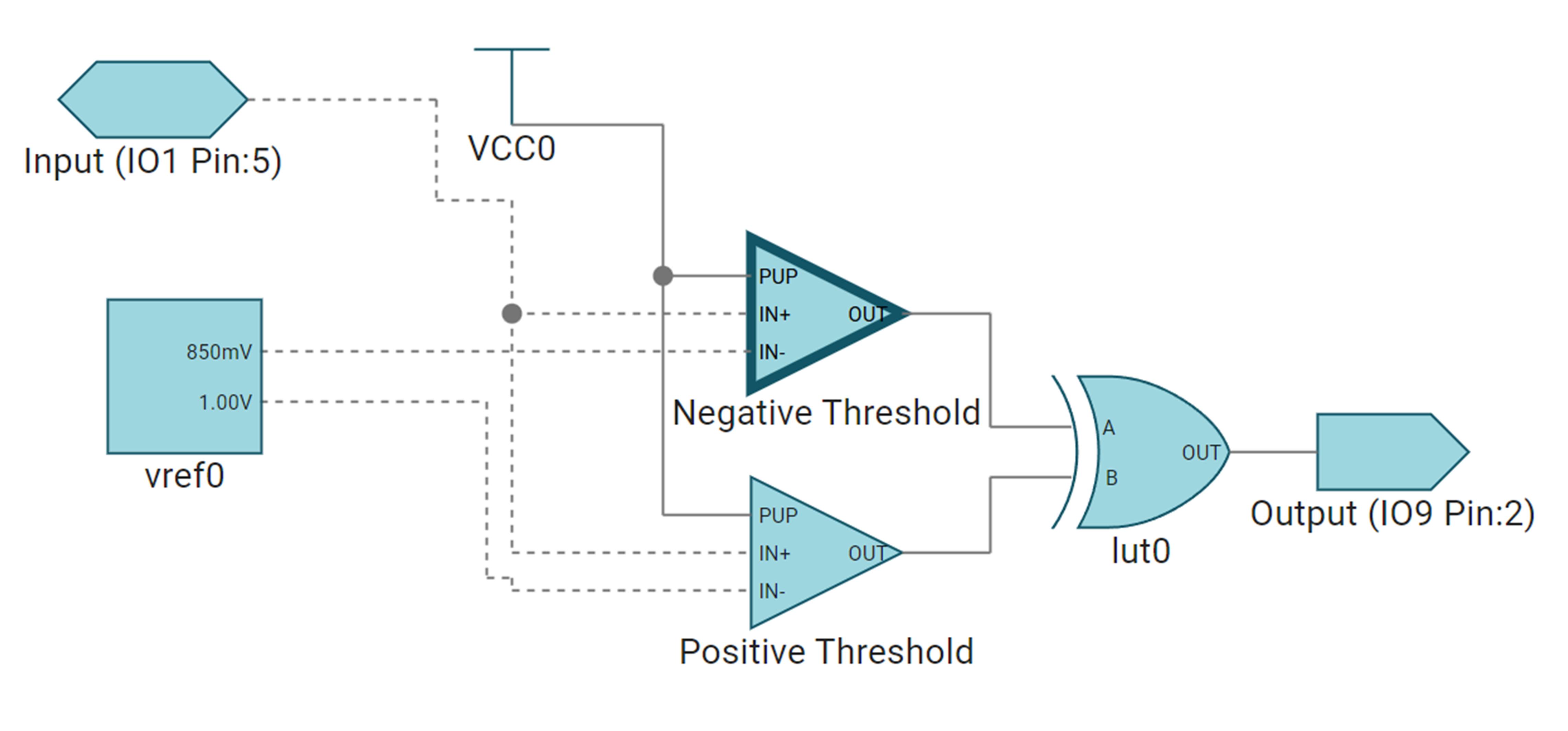

Most devices within the TPLD portfolio, such as the TPLD1201 and the TPLD1202, have integrated analog comparators along with their logical elements. Using InterConnect Studio (ICS), the analog comparators can be configured to behave as a window comparator, as shown in Figure 2.

Figure 2 Window Comparator using Internal Voltage References in ICS

Figure 2 Window Comparator using Internal Voltage References in ICSIn the configuration shown in Figure 2, the outputs of two analog comparators measuring the same voltage are combined using an XOR gate. The output of the gate triggers only when one, but not both, of the analog comparators is above its voltage reference. The negative threshold of the window comparator is set as the lower reference voltage and the positive threshold of the window comparator is set as the higher reference voltage. Figure 1 shows the behavior of this configuration.

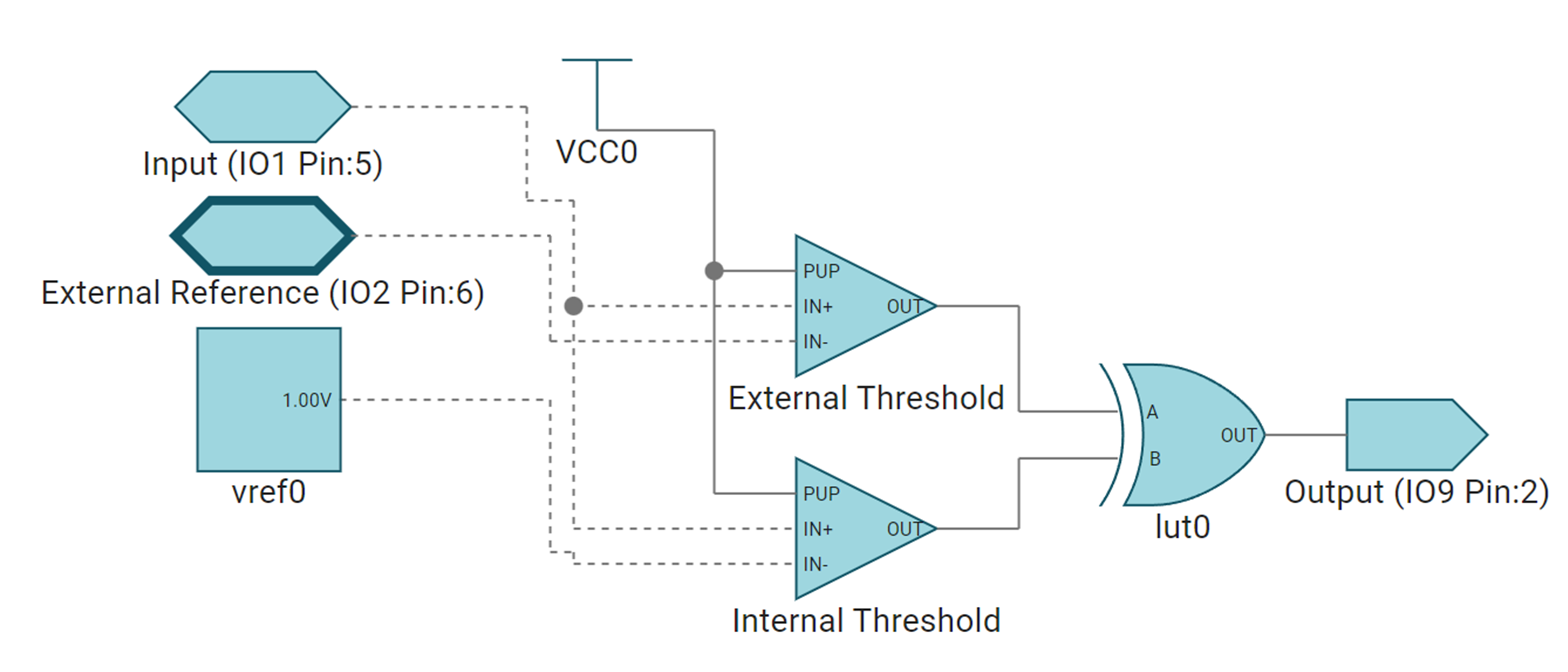

In this design, both reference voltages are provided by the TPLD’s internal voltage references. If necessary, one of the reference voltages can instead be set as an external voltage by changing the negative threshold of one of the analog comparators to be an external pin instead of the internal voltage reference, as shown in Figure 3.

Figure 3 Window Comparator using an External Voltage Reference in ICS

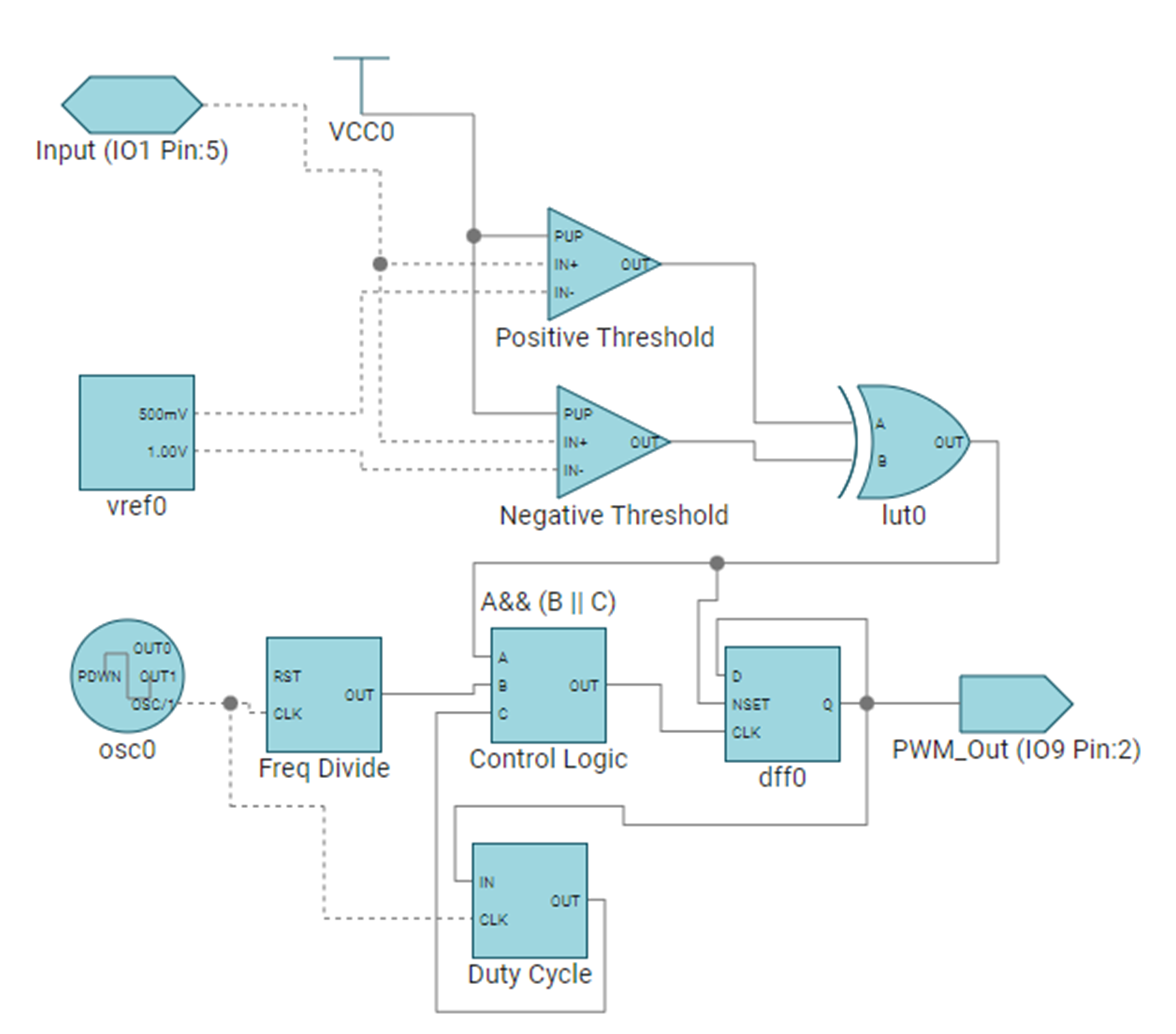

Figure 3 Window Comparator using an External Voltage Reference in ICSOnce the window comparator is configured, the output of the lookup table can be used with the other elements in the TPLD to create an integrated solution. Figure 4 shows an example where a window comparator is used to provide the enable signal to a 1kHz PWM signal with a 25% duty cycle when the input voltage is between 0.5V and 2V.

Figure 4 Integrated Window Comparator

and PWM Generator

Figure 4 Integrated Window Comparator

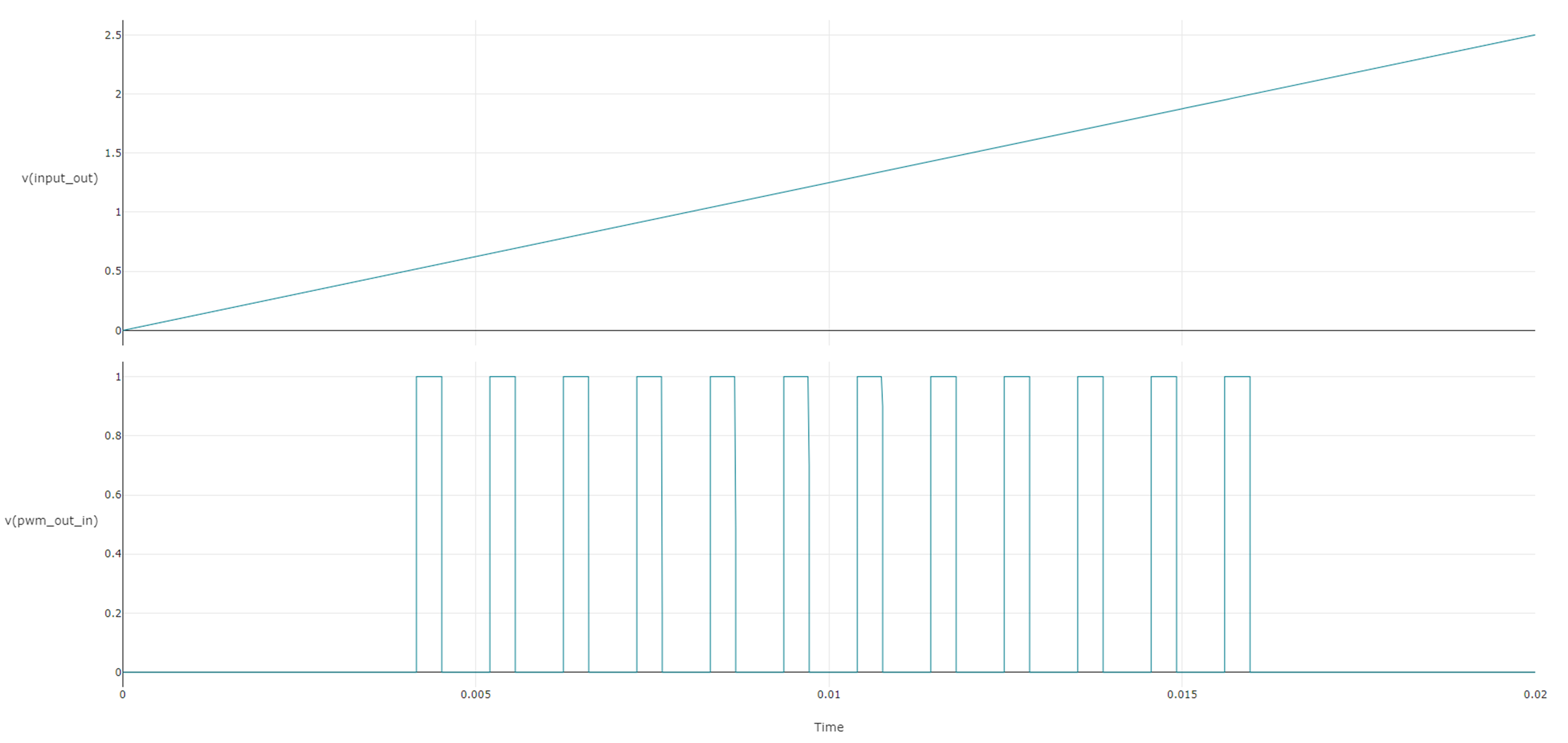

and PWM GeneratorFigure 5 shows the output simulation of this example configuration generated by ICS.

Figure 5 Integrated Window Comparator

and PWM Generator ICS Simulation

Figure 5 Integrated Window Comparator

and PWM Generator ICS SimulationDesign Considerations

TPLD1201 and TPLD1202 do not support input voltages above VCC.

This design outputs a high signal when the input voltage is within the window comparator’s limits. For a design that outputs a low signal when the input voltage is within the limits, switch the XOR gate for an XNOR gate.

The blocks present in TPLD allow for the design and configuration of many complex systems combining digital and analog signals. For more information on TPLD, visit the TPLD1201 product page or ask our engineers a question on the TI E2E™ Logic Support Forum.