SCLS099I December 1982 – September 2024 SN54HC112 , SN74HC112

PRODUCTION DATA

3 Description

The SNx4HC112 devices contain two independent J-K negative-edge-triggered flip-flops. A low level at the preset (PRE) or clear (CLR) inputs sets or resets the outputs, regardless of the levels of the other inputs. When PRE and CLR are inactive (high), data at the J and K inputs meeting the setup time requirements are transferred to the outputs on the negative-going edge of the clock (CLK) pulse. Clock triggering occurs at a voltage level and is not directly related to the fall time of the CLK pulse. Following the hold-time interval, data at the J and K inputs may be changed without affecting the levels at the outputs. These versatile flip-flops perform as toggle flip-flops by tying J and K high.

| PART NUMBER | PACKAGE(1) | PACKAGE SIZE(2) | BODY SIZE (NOM)(3) |

|---|---|---|---|

| SNx4HC112 | J (CDIP, 16) | 19.56mm × 6.92mm | 19.56mm × 6.92mm |

| D (SOIC, 16) | 9.9mm × 6mm | 9.9mm × 3.9mm | |

| N (PDIP, 16) | 19.3mm × 9.4mm | 19.3mm × 6.35mm | |

| FK (LCCC, 20) | 8.89mm × 8.89mm | 8.89mm × 8.89mm | |

| W (CFP, 16) | 10.3mm × 6.73mm | 10.3mm × 6.73mm |

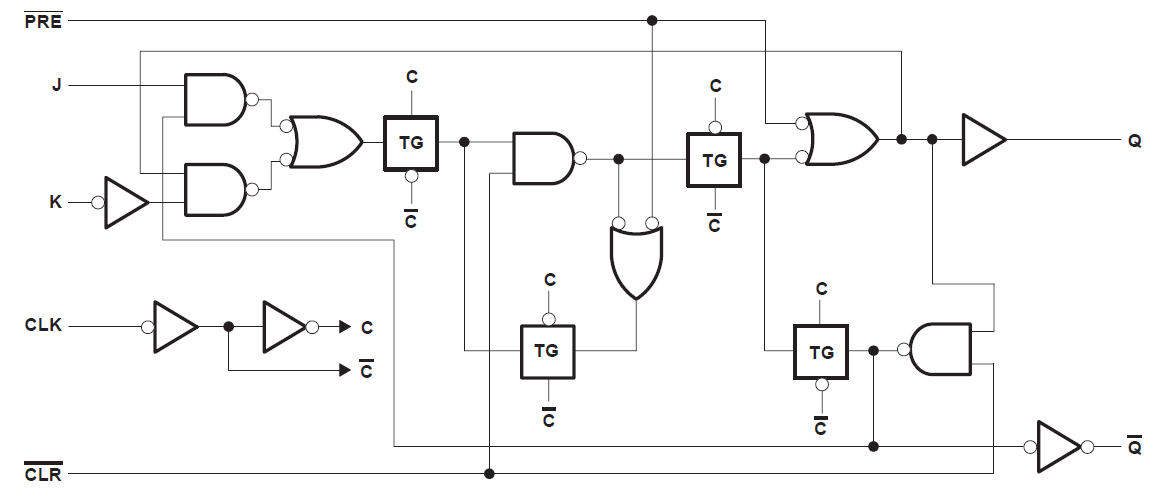

Functional Block

Diagram

Functional Block

Diagram