SLAAED8 October 2024 TAC5111 , TAC5112 , TAC5211 , TAC5212 , TAC5412-Q1 , TAD5112 , TAD5212

3.6 Ultrasonic Activity Detection (UAD) ADSR Mode

Figure 3-4 Graphical Representation of UAD ADSR Envelope

Figure 3-4 Graphical Representation of UAD ADSR Envelope SG2 supports the Ultrasonic Activity Detection (UAD) feature using some ADSR parameters. Refer to this register map to configure UAD mode.

SG2 in this mode can be referred to as Ultrasonic Activity Generator (UAG). UAG is only available to SG2 CPM. All CPM calculations apply in this mode and the default sample rate is 96ksps meaning this mode collects samples at double the regular ADSR mode.

This mode employs all ADSR registers except the attack, release, and decay timer registers. Registers B0_P23_R104 (0x6C) to B0_P23_111 (0x6F) configure the UAG attack time and registers B0_P23_R104 (0x70) to B0_P23_111 (0x74) configure UAG release time. This mode has no decay time.

UAG attack and release time can be determined the same way. The following uses attack time to demonstrate how to retrieve register values:

Here RT is a the time constant in ms. This takes 5 times RT to acquire desired attack time and to reach 99% of 2Vrms, full-scale. For example, RT = 1ms means a desired time of 5ms. This equation also deducts the attack constant needed to retrieve register coefficient values. Use this formula to retrieve register values:

Where k is the attack constant.

The Ultrasonic Activity Detection (UAD) ADSR Mode highlights the UAG ADSR pulse waveform. Reference this UAG/ UAD example script for ultrasonic applications.

# Key: w a0 XX YY ==> write to I2C address 0xa0, to register 0xXX, data 0xYY

# # ==> comment delimiter

#

#The following list gives an example sequence of items that must be #executed in the time between powering the device up and reading data #from the device. Note that there are other valid sequences depending #on which features are used.

#See the corresponding EVM user guide for jumper settings and audio #connections.

#

# Line-Out Fully-Differential 2-channel : OUT1P_M- Ch1, OUT2P_M- Ch2.

# FSYNC = 48 kHz (Output Data Sample Rate), BCLK = 12.288 MHz (BCLK/FSYNC = 256)

#UAG/UAD Example Script

w a0 00 00 #locate page 0

w a0 01 01 #device reset

w a0 02 09 # come out of sleep mode with VREF and DREG up

w a0 00 17 #locate page 0x17

w a0 7c 14 f1 a6 c6 # 10kHz chirp start frequency

w a0 00 1c #locate page 0x1c

#restart timer

w a0 50 00 00 bb 80 #48k samples for 1s

#sustain timer

w a0 54 00 00 5d c0 #24000 samples at 500ms

#sustain level

w a0 64 40 00 00 00 #k=0.6

#uag attack

w a0 00 17 #locate page 0x17

#w a0 6c 7D 5C 65 34 #default

#uag release

#w a0 70 7D 5C 65 34 #default

w a0 00 01 #locate page 0x01

w a0 1f 00 #uag on ch1

w a0 20 00 #uag clk cfg

w a0 00 00 #locate page 0x00

w a0 76 08 #en out ch1

w a0 78 02 #en uag

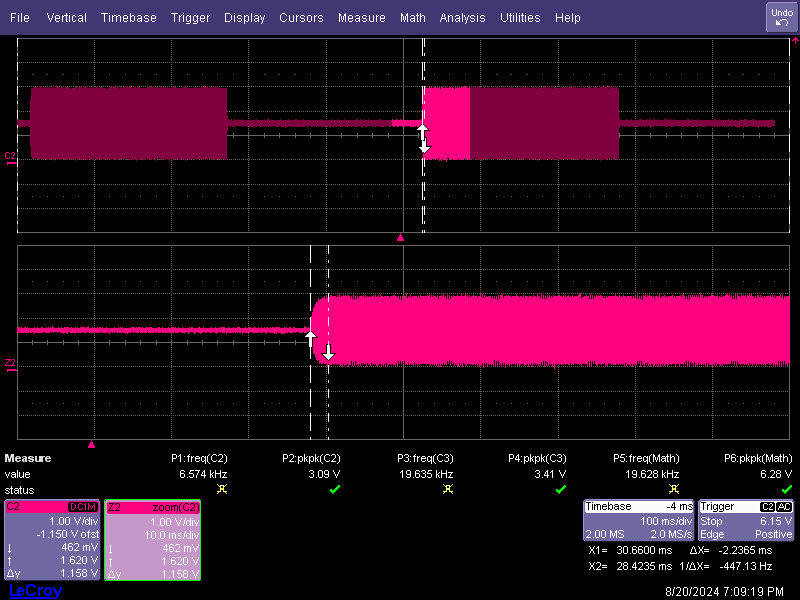

Figure 3-5 Ultrasonic Activity Detection Generator Scope Capture

Figure 3-5 Ultrasonic Activity Detection Generator Scope Capture|

Parameter |

Page Address |

Register Address |

Default Values |

|---|---|---|---|

|

Restart Timer |

0x1C |

0x50 |

100ms at 96Ksps |

|

Sustain Timer |

0x1C |

0x54 |

10ms at 96Ksps |

|

Sustain Level |

0x1C |

0x64 |

0dB |

|

Power delay |

0x17 |

0x74 |

9600 samples |

|

Attack Timer |

0x17 |

0x6C |

2.5ms at 96Ksps |

|

Release Timer |

0x17 |

0x70 |

2.5ms at 96Ksps |