SLAAED8 October 2024 TAC5111 , TAC5112 , TAC5211 , TAC5212 , TAC5412-Q1 , TAD5112 , TAD5212

4.3 Signal Generator 2 Frequency

Registers B0_P23_R124 (0x7C) to B0_P23_R127 (0x7F) configure SG2 Chirp Start Frequency. Registers B0_P24_R08 (0x08) to B0_P24_R11 (0x0B) configure SG2 Chirp Delta Frequency. Refer to Table 4-2.

Although amplitude and channel selection methods are the same for SG1 and SG2, both differ in frequency configuration. Chirp Start Frequency and Chirp Delta Frequency make up SG2 frequency parameters. These parameters are 32-bit I2C commands each and are not dependent on each other.

The chirp start frequency is the frequency in the first sample of one second of a sampled signal per an operating sampling rate. This is can be considered the beginning frequency.

The chirp delta frequency is the frequency rise per sample up until the last sample within a defined time period. Per each sample, the next frequency rise is added to the last frequency in the previous sample. This parameter forces frequency sweeps through the start frequency. This can also be configured to not create any sweeps.

Once these parameters are set, this applies to any output channels for SG2. Use these formulas to generate 32-bit I2C scripts to configure SG2 frequency.

where k is either the Chirp Start Frequency Constant or the Chirp Delta Frequency Constant. This formula applies to generating hex coefficients for both frequency parameters.

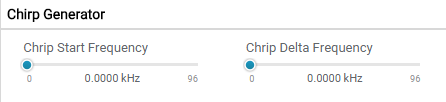

In PPC3, SG2 frequency is set using the Chirp Generator frequency scroll. Figure 4-2 is an image of SG2 GUI.

Figure 4-2 SG2 Frequency Configuration GUI

Figure 4-2 SG2 Frequency Configuration GUIPage | Register | Description | Reset Value |

|---|---|---|---|

0x17 | 0x7C | ASIOUT_BYT1[7:0] | 0x00 |

| 0x17 | 0x7D | ASIOUT_BYT2[7:0] | 0x00 |

| 0x17 | 0x7E | ASIOUT_BYT3[7:0] | 0x00 |

| 0x17 | 0x7F | ASIOUT_BYT4[7:0] | 0x00 |

Page | Register | Description | Reset Value |

|---|---|---|---|

0x18 | 0x08 | ASIOUT__BYT1[7:0] | 0x00 |

| 0x18 | 0x09 | ASIOUT_BYT2[7:0] | 0x00 |

| 0x18 | 0x0A | ASIOUT_BYT3[7:0] | 0x00 |

| 0x18 | 0x0B | ASIOUT_BYT4[7:0] | 0x00 |