SLAAEH2A December 2023 – June 2024 TAA5212 , TAC5111 , TAC5112 , TAC5211 , TAC5212 , TAD5112 , TAD5212

3.2 DAC Sampling Rate Conversion

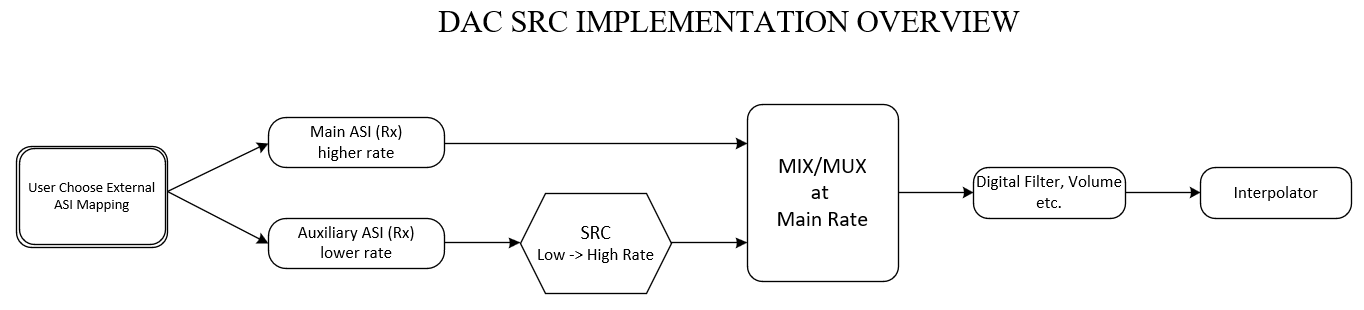

In DAC SRC flow, the received ASI bus can pass through the Sampling Rate Converter first as mixing or muxing can run at the main Fs rate. The default DAC flow is shown in Figure 3-2 where 2 ASI digital inputs running at different sampling rates are mixed/muxed before any digital filtering, volume control, interpolation and DAC drivers. Similar to the ADC SRC, user can choose Primary ASI or Secondary ASI for the two rates. Figure 3-2 shows main Fs as the higher rate (default mode).

Figure 3-2 TAx5x1x DAC SRC Overview - Default Mode

Figure 3-2 TAx5x1x DAC SRC Overview - Default ModeSimilar to ADC, the user needs to watch the levels when mixing 2 signals and the equation to set the mixing coefficients for DAC is given below where w represents the weight or scale of magnitude. For example w=0.5 represents half of the magnitude which translates into 'h2000 in the 16-bit DAC mixer coefficients. The default on some of the path coefficients are 'h4000 for the full scale magnitude of 1.

The DAC mixer coefficients are configured through register page address 0x11 register address 0x08 to 0x47 for main ASI (higher rate interface) and for auxiliary ASI (lower rate), it's configured through register page address 0x11 register address 0x48 to 0x57.

For Side Chain DAC mixer, the coefficients are configured through register page address 0x11 and register address from 0x58 to 0x77 using the same coefficient Equation 4.