SLASEN5 October 2017 MSP432E401Y

PRODUCTION DATA.

- 1Device Overview

- 2Revision History

- 3Device Characteristics

- 4Terminal Configuration and Functions

-

5Specifications

- 5.1 Absolute Maximum Ratings

- 5.2 ESD Ratings

- 5.3 Recommended Operating Conditions

- 5.4 Recommended DC Operating Conditions

- 5.5 Recommended GPIO Operating Characteristics

- 5.6 Recommended Fast GPIO Pad Operating Conditions

- 5.7 Recommended Slow GPIO Pad Operating Conditions

- 5.8 GPIO Current Restrictions

- 5.9 I/O Reliability

- 5.10 Current Consumption

- 5.11 Peripheral Current Consumption

- 5.12 LDO Regulator Characteristics

- 5.13 Power Dissipation

- 5.14 Thermal Resistance Characteristics, 128-Pin PDT (TQFP) Package

- 5.15

Timing and Switching Characteristics

- 5.15.1 Load Conditions

- 5.15.2 Power Supply Sequencing

- 5.15.3 Reset Timing

- 5.15.4

Clock Specifications

- 5.15.4.1 PLL Specifications

- 5.15.4.2 PIOSC Specifications

- 5.15.4.3 Low-Frequency Oscillator Specifications

- 5.15.4.4 Hibernation Low-Frequency Oscillator Specifications

- 5.15.4.5 Main Oscillator Specifications

- 5.15.4.6 Main Oscillator Specification WIth ADC

- 5.15.4.7 System Clock Characteristics With USB Operation

- 5.15.5 Sleep Modes

- 5.15.6 Hibernation Module

- 5.15.7 Flash Memory

- 5.15.8 EEPROM

- 5.15.9 Input/Output Pin Characteristics

- 5.15.10 External Peripheral Interface (EPI)

- 5.15.11 Analog-to-Digital Converter (ADC)

- 5.15.12 Synchronous Serial Interface (SSI)

- 5.15.13 Inter-Integrated Circuit (I2C) Interface

- 5.15.14 Ethernet Controller

- 5.15.15 Universal Serial Bus (USB) Controller

- 5.15.16 Analog Comparator

- 5.15.17 Pulse-Width Modulator (PWM)

- 5.15.18 Emulation and Debug

-

6Detailed Description

- 6.1 Overview

- 6.2 Functional Block Diagram

- 6.3 Arm Cortex-M4F Processor Core

- 6.4 On-Chip Memory

- 6.5

Peripherals

- 6.5.1 External Peripheral Interface (EPI)

- 6.5.2 Cyclical Redundancy Check (CRC)

- 6.5.3 Advanced Encryption Standard (AES) Accelerator

- 6.5.4 Data Encryption Standard (DES) Accelerator

- 6.5.5 Secure Hash Algorithm/Message Digest Algorithm (SHA/MD5) Accelerator

- 6.5.6 Serial Communications Peripherals

- 6.5.7 System Integration

- 6.5.8 Advanced Motion Control

- 6.5.9 Analog

- 6.5.10 JTAG and Arm Serial Wire Debug

- 6.5.11 Peripheral Memory Map

- 6.6 Identification

- 6.7 Boot Modes

- 7Applications, Implementation, and Layout

- 8Device and Documentation Support

- 9Mechanical, Packaging, and Orderable Information

5 Specifications

5.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1) (2)| MIN | MAX | UNIT | ||

|---|---|---|---|---|

| VDD | VDD supply voltage | 0 | 4 | V |

| VDDA | VDDA supply voltage | 0 | 4 | V |

| VBAT | VBAT battery supply voltage | 0 | 4 | V |

| VBATRMP | VBAT battery supply voltage ramp time | 0 | 0.7 | V/µs |

| VIN_GPIO | Input voltage (3) | –0.3 | 4 | V |

| IGPIOMAX | Maximum current per output pin | 64 | mA | |

| TS | Unpowered storage temperature range | –65 | 150 | °C |

| TJMAX | Maximum junction temperature | 125 | °C | |

5.2 ESD Ratings

over operating free-air temperature range (unless otherwise noted)| VALUE | UNIT | |||

|---|---|---|---|---|

| V(ESD) | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS‑001 (1) (3) | ±2000 | V |

| Charged-device model (CDM), per JEDEC specification JESD22‑C101 (2) | ±500 | |||

- The Ethernet EN0RXIN, EN0TXON, EN0RXIP, and EN0TXOP pins to each other.

- The GPIO pins PM4, PM5, PM6, and PM7 to other pins.

5.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)| MIN | MAX | UNIT | |||

|---|---|---|---|---|---|

| TA | Ambient operating temperature range | Extended temperature | –40 | 105 | °C |

| TJ | Junction operating temperature range | Extended temperature | –40 | 125 | °C |

5.4 Recommended DC Operating Conditions

over operating free-air temperature (unless otherwise noted)| MIN | NOM | MAX | UNIT | ||

|---|---|---|---|---|---|

| VDD | VDD supply voltage | 2.97 | 3.3 | 3.63 | V |

| VDDA | VDDA supply voltage (1) | 2.97 | 3.3 | 3.63 | V |

| VDDC | VDDC supply voltage, run mode | 1.14 | 1.2 | 1.32 | V |

| VDDCDS | VDDC supply voltage, deep-sleep mode | 0.85 | 0.95 | V |

5.5 Recommended GPIO Operating Characteristics

The following sections describe the recommended GPIO operating characteristics for the device.

Two types of pads are provided on the device:

- Fast GPIO pads: These pads provide variable, programmable drive strength and optimized voltage output levels.

- Slow GPIO pads: These pads provide 2-mA drive strength and are designed to be sensitive to voltage inputs. The PJ1 GPIOs port pins are slow GPIO pads. All other GPIOs have a fast GPIO pad type.

NOTE

Port pins PL6 and PL7 operate as fast GPIO pads, but have 4-mA drive capability only. GPIO register controls for drive strength, slew rate and open drain have no effect on these pins. The registers which have no effect are as follows: GPIODR2R, GPIODR4R, GPIODR8R, GPIODR12R, GPIOSLR, and GPIOODR.

NOTE

Port pins PM[7:4] operate as fast GPIO pads but support only 2-, 4-, 6-, and 8-mA drive capability. 10- and 12-mA drive are not supported. All standard GPIO register controls, except for the GPIODR12R register, apply to these port pins.

5.6 Recommended Fast GPIO Pad Operating Conditions

over operating free-air temperature range (unless otherwise noted)| MIN | NOM | MAX | UNIT | |||

|---|---|---|---|---|---|---|

| VIH | Fast GPIO high-level input voltage | 0.65 × VDD | 4 | V | ||

| IIH | Fast GPIO high-level input current | 300 | nA | |||

| VIL | Fast GPIO low-level input voltage | 0 | 0.35 × VDD | V | ||

| IIL | Fast GPIO low-level input current (2) | –200 | nA | |||

| VHYS | Fast GPIO input hysteresis | 0.49 | V | |||

| VOH | Fast GPIO high-level output voltage | 2.4 | V | |||

| VOL | Fast GPIO low-level output voltage | 0.40 | V | |||

| IOH | Fast GPIO high-level source current, VOH = 2.4 V (1) | 2-mA drive | 2.0 | mA | ||

| 4-mA drive | 4.0 | |||||

| 8-mA drive | 8.0 | |||||

| 10-mA drive | 10.0 | |||||

| 12-mA drive | 12.0 | |||||

| IOL | Fast GPIO low-level sink current, VOL = 0.4 V (1) | 2-mA drive | 2.0 | mA | ||

| 4-mA drive | 4.0 | |||||

| 8-mA drive | 8.0 | |||||

| 10-mA drive | 10.0 | |||||

| 12-mA drive | 12.0 | |||||

| 12-mA drive overdriven to 18 mA | 18.0 | |||||

5.7 Recommended Slow GPIO Pad Operating Conditions

over operating free-air temperature range (unless otherwise noted)| MIN | NOM | MAX | UNIT | |||

|---|---|---|---|---|---|---|

| VIH | Slow GPIO high-level input voltage | 0.65 × VDD | 4 | V | ||

| IIH | Slow GPIO high-level input current | 4.1 | nA | |||

| VIL | Slow GPIO low-level input voltage | 0 | 0.35 × VDD | V | ||

| IIL | Slow GPIO low-level input current (2) | –1 | nA | |||

| VHYS | Slow GPIO input hysteresis | 0.49 | V | |||

| VOH | Slow GPIO high-level output voltage | 2.4 | V | |||

| VOL | Slow GPIO low-level output voltage | 0.4 | V | |||

| IOH | Slow GPIO high-level source current, VOH = 2.4 V, 2-mA drive | 2.0 | mA | |||

| IOL | Slow GPIO low-level sink current, VOL = 0.4 V (1), 2-mA drive | 2.0 | mA | |||

5.8 GPIO Current Restrictions

over operating free-air temperature range (unless otherwise noted) (1)| MIN | NOM | MAX | UNIT | ||

|---|---|---|---|---|---|

| IMAXL | Cumulative maximum GPIO current per side, left | 112 | mA | ||

| IMAXB | Cumulative maximum GPIO current per side, bottom (2) | 97.6 | mA | ||

| IMAXR | Cumulative maximum GPIO current per side, right (2) | 112 | mA | ||

| IMAXT | Cumulative maximum GPIO current per side, top (2) | 80 | mA |

Table 5-1 Maximum GPIO Package Side Assignments

| SIDE | GPIOs |

|---|---|

| Left | PC[4-7], PD[0-3], PQ[0-3], PE[0-3], PK[0-3], PN[4-5], PH[0-3] |

| Bottom | PA[0-7], PF[0-4],PG[0-1], PK[4-7] |

| Right | PM[0-7], PL[0-7], PB[0-3] |

| Top | PC[0-3], PQ[4], PP[0-5], PN[0-5], PJ[0-1], PB[4-5], PE[4-5], PD[4-7] |

5.9 I/O Reliability

For typical continuous drive applications, I/O pins configured in the range from 2 mA to 12 mA and operating at –40°C to 85°C meet the standard 10-year lifetime reliability. If a continuous current sink of 18 mA is required, then operation is limited to 0 to 75°C to meet the standard 10-year reliability.

At 105°C, I/O pins configured for continuous drive meet the standard 2.5-year lifetime reliability.

In typical switching applications (40% switch rate) operating at –40°C to 85°C, all I/O configurations except 2 mA meet the standard 10-year lifetime reliability with 50-pF loading. By limiting the capacitive loading to 20 pF for an I/O configured to 2 mA, the 10-year lifetime reliability can be met at –40°C to 85°C.

In typical switching applications (40% switch rate) operating at 105°C, all I/O configurations except 2 mA meet the standard 2.5-year lifetime reliability. By reducing the capacitive loading to 20 pF with a typical switching rate at 105°C, a 2-mA I/O configuration meets a 2.5-year lifetime reliability.

5.10 Current Consumption

over operating free-air temperature (unless otherwise noted) (1)| PARAMETER | TEST CONDITIONS | SYSTEM CLOCK | TYP | MAX | UNIT | ||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| FREQ | CLOCK SOURCE | –40°C | 25°C | 85°C | 105°C | 85°C | 105°C (2) | ||||

| IDD_RUN | Run mode (flash loop) | VDD = 3.3 V, VDDA = 3.3 V, Peripherals = All on including MAC and PHY |

120 MHz | MOSC with PLL | 96.4 | 105.3 | 107.2 | 108.7 | 129.9 | 140.0 | mA |

| 60 MHz | MOSC with PLL | 67.4 | 76.6 | 78.6 | 79.9 | 100.3 | 112.5 | ||||

| 16 MHz | PIOSC | 11.9 | 24.4 | 25.5 | 26.7 | 45.0 | 56.4 | ||||

| 1 MHz | PIOSC | 5.75 | 10.9 | 12.1 | 13.3 | 31.3 | 42.6 | ||||

| VDD = 3.3 V, VDDA = 3.3 V, Peripherals = All on including MAC but not PHY |

120 MHz | MOSC with PLL | 69.9 | 77.8 | 79.6 | 80.8 | 98.8 | 108.4 | |||

| 60 MHz | MOSC with PLL | 40.9 | 49.2 | 50.9 | 52.1 | 69.2 | 80.8 | ||||

| 16 MHz | PIOSC | 11.3 | 23.6 | 25.0 | 26.2 | 43.1 | 54.3 | ||||

| 1 MHz | PIOSC | 5.10 | 10.1 | 11.5 | 12.7 | 29.3 | 40.5 | ||||

| VDD = 3.3 V, VDDA = 3.3 V, Peripherals = All on except MAC and PHY |

120 MHz | MOSC with PLL | 68.1 | 76.0 | 77.6 | 78.6 | 96.6 | 106.0 | |||

| 60 MHz | MOSC with PLL | 40.0 | 48.2 | 49.8 | 50.8 | 67.9 | 79.2 | ||||

| 16 MHz | PIOSC | 11.1 | 23.3 | 24.6 | 25.6 | 42.5 | 53.3 | ||||

| 1 MHz | PIOSC | 5.07 | 10.1 | 11.3 | 12.3 | 29.0 | 39.8 | ||||

| VDD = 3.3 V, VDDA = 3.3 V, Peripherals = All off |

120 MHz | MOSC with PLL | 35.2 | 39.1 | 40.4 | 41.5 | 55.8 | 65.3 | |||

| 60 MHz | MOSC with PLL | 23.2 | 29.4 | 30.7 | 31.7 | 45.8 | 55.5 | ||||

| 16 MHz | PIOSC | 7.38 | 17.9 | 19.0 | 20.0 | 34.5 | 44.1 | ||||

| 1 MHz | PIOSC | 4.12 | 9.13 | 10.3 | 11.4 | 25.7 | 35.5 | ||||

| Run mode (SRAM loop) | VDD = 3.3 V, VDDA = 3.3 V, Peripherals = All on including MAC and PHY |

120 MHz | MOSC with PLL | 93.8 | 103.6 | 111.6 | 113.2 | 133.4 | 144.6 | ||

| 60 MHz | MOSC with PLL | 66.9 | 76.7 | 78.7 | 80.0 | 100.0 | 111.9 | ||||

| 16 MHz | PIOSC | 12.6 | 19.0 | 20.1 | 21.3 | 39.1 | 50.3 | ||||

| 1 MHz | PIOSC | 5.73 | 10.6 | 11.7 | 12.8 | 30.9 | 42.2 | ||||

| VDD = 3.3 V, VDDA = 3.3 V, Peripherals = All on including MAC but not PHY |

120 MHz | MOSC with PLL | 67.2 | 76.1 | 84.0 | 85.4 | 102.3 | 113.0 | |||

| 60 MHz | MOSC with PLL | 40.3 | 49.2 | 50.9 | 52.2 | 68.9 | 80.2 | ||||

| 16 MHz | PIOSC | 11.9 | 18.2 | 19.6 | 20.8 | 37.2 | 48.2 | ||||

| 1 MHz | PIOSC | 5.08 | 9.79 | 11.2 | 12.3 | 28.9 | 40.1 | ||||

| VDD = 3.3 V, VDDA = 3.3 V, Peripherals =All on except MAC and PHY |

120 MHz | MOSC with PLL | 65.4 | 74.3 | 82.0 | 83.2 | 100.1 | 110.6 | |||

| 60 MHz | MOSC with PLL | 39.4 | 48.2 | 49.8 | 50.9 | 67.6 | 78.6 | ||||

| 16 MHz | PIOSC | 11.7 | 17.9 | 19.2 | 20.2 | 36.6 | 47.2 | ||||

| 1 MHz | PIOSC | 5.05 | 9.75 | 11.0 | 11.9 | 28.6 | 39.4 | ||||

| VDD = 3.3 V, VDDA = 3.3 V, Peripherals = All off |

120 MHz | MOSC with PLL | 35.4 | 43.3 | 44.7 | 45.8 | 59.8 | 69.0 | |||

| 60 MHz | MOSC with PLL | 23.4 | 29.4 | 30.7 | 31.7 | 45.5 | 54.9 | ||||

| 16 MHz | PIOSC | 7.08 | 12.4 | 13.6 | 14.6 | 28.7 | 38.0 | ||||

| 1 MHz | PIOSC | 4.60 | 8.78 | 10.0 | 11.0 | 25.3 | 34.9 | ||||

| IDD_SLEEP | Sleep mode (FLASHPM = 0x0) | VDD = 3.3 V, VDDA = 3.3 V, Peripherals = All on including MAC and PHY, LDO = 1.2 V |

120 MHz | MOSC with PLL | 82.8 | 94.8 | 96.8 | 98.1 | 117.9 | 129.1 | mA |

| 60 MHz | MOSC with PLL | 60.8 | 69.2 | 71.2 | 72.3 | 91.8 | 102.9 | ||||

| 16 MHz | PIOSC | 11.2 | 16.8 | 18.1 | 19.1 | 35.4 | 45.9 | ||||

| 1 MHz | PIOSC (3) | 5.10 | 10.3 | 11.5 | 12.6 | 28.9 | 39.6 | ||||

| VDD = 3.3 V, VDDA = 3.3 V, Peripherals = All on including MAC but not PHY, LDO = 1.2 V |

120 MHz | MOSC with PLL | 56.2 | 67.4 | 69.1 | 70.3 | 87.1 | 97.8 | |||

| 60 MHz | MOSC with PLL | 34.4 | 41.9 | 43.4 | 44.5 | 60.7 | 71.6 | ||||

| 16 MHz | PIOSC (3) | 10.6 | 16.2 | 17.5 | 18.5 | 34.5 | 45.1 | ||||

| 1 MHz | PIOSC (3) | 4.47 | 9.60 | 10.9 | 12.0 | 28.0 | 38.7 | ||||

| VDD = 3.3 V, VDDA = 3.3 V, Peripherals = All on except MAC and PHY, LDO = 1.2 V |

120 MHz | MOSC with PLL | 54.4 | 65.6 | 67.1 | 68.1 | 84.9 | 95.4 | |||

| 60 MHz | MOSC with PLL | 33.5 | 40.9 | 42.3 | 43.2 | 59.4 | 70.0 | ||||

| 16 MHz | PIOSC (3) | 10.4 | 15.9 | 17.1 | 17.9 | 33.9 | 44.1 | ||||

| 1 MHz | PIOSC (3) | 4.44 | 9.56 | 10.7 | 11.6 | 27.7 | 38.0 | ||||

| VDD = 3.3 V, VDDA = 3.3 V, Peripherals = All off, LDO = 1.2 V |

120 MHz | MOSC with PLL | 22.0 | 28.6 | 29.8 | 30.7 | 44.1 | 53.1 | |||

| 60 MHz | MOSC with PLL | 16.3 | 22.0 | 23.2 | 24.1 | 37.5 | 46.6 | ||||

| 16 MHz | PIOSC (3) | 5.37 | 10.4 | 11.5 | 12.4 | 26.1 | 35.1 | ||||

| 1 MHz | PIOSC (3) | 4.37 | 8.60 | 9.71 | 10.6 | 24.6 | 33.9 | ||||

| Sleep mode (FLASHPM = 0x2) | VDD = 3.3 V, VDDA = 3.3 V, Peripherals = All on including MAC and PHY, LDO = 1.2 V |

120 MHz | MOSC with PLL | 86.5 | 89.0 | 91.2 | 92.5 | 112.1 | 123.5 | ||

| 60 MHz | MOSC with PLL | 61.6 | 63.4 | 65.6 | 66.7 | 86.0 | 97.2 | ||||

| 16 MHz | PIOSC (3) | 10.4 | 11.1 | 12.4 | 13.5 | 29.8 | 40.4 | ||||

| 1 MHz | PIOSC (3) | 4.45 | 4.49 | 5.83 | 6.98 | 23.4 | 34.2 | ||||

| VDD = 3.3 V, VDDA = 3.3 V, Peripherals = All on including MAC but not PHY, LDO = 1.2 V |

120 MHz | MOSC with PLL | 59.9 | 61.7 | 63.4 | 64.7 | 81.3 | 92.1 | |||

| 60 MHz | MOSC with PLL | 35.1 | 36.1 | 37.8 | 38.9 | 54.9 | 66.0 | ||||

| 16 MHz | PIOSC (3) | 9.75 | 10.4 | 11.8 | 12.9 | 28.9 | 39.6 | ||||

| 1 MHz | PIOSC (3) | 3.82 | 3.82 | 5.25 | 6.38 | 22.5 | 33.4 | ||||

| VDD = 3.3 V, VDDA = 3.3 V, Peripherals = All on except MAC and PHY, LDO = 1.2 V |

120 MHz | MOSC with PLL | 58.1 | 59.9 | 61.4 | 62.5 | 79.1 | 89.7 | |||

| 60 MHz | MOSC with PLL | 34.2 | 35.1 | 36.7 | 37.6 | 53.6 | 64.4 | ||||

| 16 MHz | PIOSC (3) | 9.50 | 10.1 | 11.4 | 12.3 | 28.3 | 38.6 | ||||

| 1 MHz | PIOSC (3) | 3.79 | 3.78 | 5.06 | 5.96 | 22.2 | 32.7 | ||||

| VDD = 3.3 V, VDDA = 3.3 V, Peripherals = All off, LDO = 1.2 V |

120 MHz | MOSC with PLL | 22.0 | 22.8 | 24.1 | 25.1 | 38.2 | 47.4 | |||

| 60 MHz | MOSC with PLL | 15.7 | 16.2 | 17.5 | 18.5 | 31.7 | 40.9 | ||||

| 16 MHz | PIOSC (3) | 4.50 | 4.60 | 5.80 | 6.80 | 20.5 | 29.8 | ||||

| 1 MHz | PIOSC (3) | 3.00 | 2.80 | 4.10 | 5.20 | 19.1 | 28.7 | ||||

| IDD_DEEPSLEEP | Deep-sleep mode (FLASHPM = 0x2) | VDD = 3.3 V, VDDA = 3.3 V, Peripherals = All on, LDO = 1.2 V |

16 MHz | PIOSC | 9.74 | 9.78 | 10.8 | 11.6 | 24.1 | 32.1 | mA |

| 30 kHz | LFIOSC | 2.60 | 2.83 | 3.83 | 4.60 | 17.1 | 25.3 | ||||

| VDD = 3.3 V, VDDA = 3.3 V, Peripherals = All off, LDO = 1.2 V |

16 MHz | PIOSC | 4.53 | 4.05 | 4.88 | 5.53 | 15.9 | 22.7 | |||

| 30 kHz | LFIOSC | 0.614 | 0.762 | 1.69 | 2.46 | 13.3 | 20.7 | ||||

| VDD = 3.3 V, VDDA = 3.3 V, Peripherals = All on, LDO = 0.9 V |

16 MHz | PIOSC | 5.21 | 7.33 | 7.97 | 8.48 | 15.3 | 20.1 | |||

| 30 kHz | LFIOSC | 2.02 | 2.16 | 2.79 | 3.29 | 10.0 | 14.9 | ||||

| VDD = 3.3 V, VDDA = 3.3 V, Peripherals = All off, LDO = 0.9 V (4) |

16 MHz | PIOSC | 1.08 | 3.10 | 3.61 | 4.01 | 9.50 | 13.4 | |||

| 30 kHz | LFIOSC | 0.367 | 0.454 | 0.954 | 1.36 | 6.86 | 10.8 | ||||

| IDDA_RUN, IDDA_SLEEP | All run modes | VDD = 3.3 V, VDDA = 3.3 V, Peripherals = All on |

120 MHz | MOSC with PLL | 2.61 | 2.66 | 2.68 | 2.66 | 3.03 | 3.35 | mA |

| 60 MHz | MOSC with PLL | 2.61 | 2.66 | 2.68 | 2.66 | 3.04 | 3.10 | ||||

| 16 MHz | PIOSC | 2.45 | 2.49 | 2.50 | 2.48 | 2.85 | 2.95 | ||||

| 1 MHz | PIOSC | 2.45 | 2.48 | 2.50 | 2.48 | 2.84 | 2.90 | ||||

| All sleep modes | VDD = 3.3 V, VDDA = 3.3 V, Peripherals = All off |

120 MHz | MOSC with PLL | 0.227 | 0.229 | 0.270 | 0.250 | 0.559 | 0.650 | ||

| 60 MHz | MOSC with PLL | 0.229 | 0.232 | 0.267 | 0.250 | 0.579 | 0.600 | ||||

| 16 MHz | PIOSC | 0.228 | 0.229 | 0.265 | 0.251 | 0.545 | 0.575 | ||||

| 1 MHz | PIOSC | 0.227 | 0.227 | 0.267 | 0.247 | 0.549 | 0.555 | ||||

| IDDA_DEEPSLEEP | Deep-sleep mode (FLASHPM = 0x2) | VDD = 3.3 V, VDDA = 3.3 V, Peripherals = All on, LDO = 1.2 V |

16 MHz | PIOSC | 2.45 | 2.48 | 2.50 | 2.48 | 2.84 | 2.90 | mA |

| 30 kHz | LFIOSC | 2.45 | 2.48 | 2.50 | 2.48 | 2.85 | 2.90 | ||||

| VDD = 3.3 V, VDDA = 3.3 V, Peripherals = All off, LDO = 1.2 V |

16 MHz | PIOSC | 0.226 | 0.227 | 0.265 | 0.249 | 0.558 | 0.635 | |||

| 30 kHz | LFIOSC | 0.228 | 0.227 | 0.272 | 0.247 | 0.558 | 0.600 | ||||

| VDD = 3.3 V, VDDA = 3.3 V, Peripherals = All on, LDO = 0.9 V (4) |

16 MHz | PIOSC | 2.14 | 2.42 | 2.44 | 2.42 | 2.78 | 2.88 | |||

| 30 kHz | LFIOSC | 2.44 | 2.42 | 2.44 | 2.42 | 2.86 | 2.88 | ||||

| VDD = 3.3 V, VDDA = 3.3 V, Peripherals = All off, LDO = 0.9 V (4) |

16 MHz | PIOSC | 0.216 | 0.166 | 0.209 | 0.193 | 0.563 | 0.580 | |||

| 30 kHz | LFIOSC | 0.223 | 0.167 | 0.209 | 0.189 | 0.508 | 0.580 | ||||

| IHIB_NORTC | Hibernate mode (external wake, RTC disabled) | VBAT = 3.0 V VDD = 0 V, VDDA = 0 V, System clock = OFF, Hibernate module = 32.768 kHz |

1.04 | 1.20 | 1.44 | 1.69 | 1.62 | 2.14 | µA | ||

| IHIB_RTC | Hibernate mode (RTC enabled) | VBAT = 3.0 V, VDD = 0 V, VDDA = 0 V, System clock = OFF, Hibernate module = 32.768 kHz |

1.12 | 1.29 | 1.54 | 1.82 | 1.75 | 2.33 | µA | ||

| IHIB_VDD3ON | Hibernate mode (VDD3ON mode, tamper enabled) | VBAT = 3.0 V, VDD = 3.3 V, VDDA = 3.3 V, System clock = OFF, Hibernate module = 32.768 kHz |

6.78 | 7.99 | 17.0 | 22.1 | 31.0 | 46.2 | µA | ||

| Hibernate mode (VDD3ON mode, tamper disabled) | VBAT = 3.0 V, VDD = 3.3 V, VDDA = 3.3 V, System clock = OFF, Hibernate module = 32.768 kHz |

5.42 | 6.39 | 15.4 | 17.8 | 28.9 | 32.0 | ||||

5.11 Peripheral Current Consumption

over operating free-air temperature (unless otherwise noted)| PARAMETER | TEST CONDITIONS | SYSTEM CLOCK | TYP | UNIT | |

|---|---|---|---|---|---|

| IDDUSB | USB (including USB PHY) run mode current | VDD = 3.3 V, VDDA = 3.3 V |

120 MHz (MOSC with PLL) | 4.0 | mA |

| IDDEMAC | Ethernet MAC run mode current | VDD = 3.3 V, VDDA = 3.3 V |

120 MHz (MOSC with PLL) | 1.9 | mA |

| IDDEMACPHY | Ethernet MAC and PHY run mode current | VDD = 3.3 V, VDDA = 3.3 V |

120 MHz (MOSC with PLL) | 30 | mA |

5.12 LDO Regulator Characteristics

over operating free-air temperature (unless otherwise noted)| PARAMETER | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|

| CLDO | External filter capacitor size for internal power supply(1) | 2.5 | 4.0 | µF | |

| ESR | Filter capacitor equivalent series resistance | 0 | 100 | mΩ | |

| ESL | Filter capacitor equivalent series inductance | 0.5 | nH | ||

| VLDO | LDO output voltage, run mode | 1.13 | 1.2 | 1.27 | V |

| IINRUSH | Inrush current | 50 | 250 | mA | |

5.13 Power Dissipation

over operating free-air temperature (unless otherwise noted) (1) (2)| PARAMETER | TA | TJ | MIN | MAX | UNIT | |

|---|---|---|---|---|---|---|

| PDE | Extended temperature device power dissipation | 105°C (extended temperature part) | 125°C (extended temperature part) | 452 | mW | |

5.14 Thermal Resistance Characteristics, 128-Pin PDT (TQFP) Package

over operating free-air temperature range (unless otherwise noted)| THERMAL METRIC | VALUE | UNIT | |

|---|---|---|---|

| θJA | Thermal resistance (junction to ambient) (1) | 44.2 | °C/W |

| θJB | Thermal resistance (junction to board) (1) | 22.4 | °C/W |

| θJC | Thermal resistance (junction to case) (1) | 6.8 | °C/W |

| ΨJT | Thermal metric (junction to top of package) | 0.2 | °C/W |

| ΨJB | Thermal metric (junction to board) | 22.1 | °C/W |

| TJ | Junction temperature formula | TC + (P × ΨJT) (2)

TPCB + (P × ΨJB) (3) TA + (P × θJA) (4) TB + (P × θJB) (5) (6) |

°C |

5.15 Timing and Switching Characteristics

5.15.1 Load Conditions

Table 5-2 shows the load conditions used for timing measurements, and Table 5-2 lists the load values for the specified signals.

Figure 5-1 Load Conditions

Figure 5-1 Load Conditions

Table 5-2 Load Conditions

| SIGNALS | LOAD VALUE (CL) |

|---|---|

| EPI0S[35:0] SDRAM interface | 30 pF |

| EPI0S[35:0] general-purpose interface | |

| EPI0S[35:0] host-bus interface | |

| EPI0S[35:0] PSRAM interface | 40 pF |

| All other digital I/O signals | 50 pF |

5.15.2 Power Supply Sequencing

To ensure proper operation, power on VDDA before VDD if sourced from different supplies, or connect VDDA to the same supply as VDD. No restriction exists for powering off.

5.15.2.1 Power and Brownout

Table 5-3 Power and Brownout Levels

over operating free-air temperature (unless otherwise noted)| NO. | PARAMETER | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| P1 | tVDDA_RISE | Analog supply voltage (VDDA) rise time | ∞ | µs | ||

| P2 | tVDD_RISE | I/O supply voltage (VDD) rise time | ∞ | µs | ||

| P3 | tVDDC_RISE | Core supply voltage (VDDC) rise time | 10 | 150 | µs | |

| P4 | VPOR | Power-on reset threshold (rising edge) | 1.98 | 2.35 | 2.72 | V |

| Power-on reset threshold (falling edge) | 1.84 | 2.20 | 2.56 | |||

| Power-on reset hysteresis | 0.06 | 0.15 | 0.24 | |||

| P5 | VDDA_POK | VDDA power-OK threshold (rising edge) | 2.67 | 2.82 | 2.97 | V |

| P6 | VDDA_BOR0 | VDDA brownout reset threshold | 2.71 | 2.80 | 2.89 | V |

| P7 | VDD_POK | VDD power-OK threshold (rising edge) | 2.65 | 2.80 | 2.90 | V |

| VDD power-OK threshold (falling edge) | 2.67 | 2.76 | 2.85 | |||

| P8 | VDD_BOR0 | VDD brownout reset threshold | 2.77 | 2.86 | 2.95 | V |

| P9 | VDDC_POK | VDDC power-OK threshold (rising edge) | 0.85 | 0.95 | 1.10 | V |

| VDDC power-OK threshold (falling edge) | 0.71 | 0.80 | 0.85 | |||

5.15.2.1.1 VDDA Levels

The VDDA supply has three monitors:

- Power-on reset (POR)

- Power-OK (POK)

- Brownout reset (BOR)

The POR monitor is used to keep the analog circuitry in reset until the VDDA supply reaches the correct range for the analog circuitry to begin operating. The POK monitor is used to keep the digital circuitry in reset until the VDDA power supply is at an acceptable operational level. The digital reset is only released when the Power-On Reset has deasserted and the Power-OK monitor for each supply indicates that power levels are in operational ranges. The BOR monitor is used to generate a reset to the device or assert an interrupt if the VDDA supply drops below its operational range.

NOTE

VDDA BOR and VDD BOR events are a combined BOR to the system logic, such that if either BOR event occurs, the following bits are affected:

- The BORRIS bit in the Raw Interrupt Status (RIS) register, System Control offset 0x050

- The BORMIS bit in the Masked Interrupt Status and Clear (MISC) register, System Control offset 0x058. This bit is set only if the BORIM bit in the Interrupt Mask Control (IMC) register has been set.

- The BOR bit in the Reset Cause (RESC) register, System Control offset 0x05C. This bit is set only if either of the BOR events have been configured to initiate a reset.

In addition, the following bits control both BOR events:

- The BORIM bit in the Interrupt Mask Control (IMC) register, System Control offset 0x054

- The VDDA_UBOR0 and VDD_UBOR0 bits in the Power-Temperature Cause (PWRTC) register

See the System Control chapter of the MSP432E4 SimpleLink™ Microcontrollers Technical Reference Manual for more information on how to configure these registers.

Figure 5-2 shows the relationship between VDDA, POK, POR, and a BOR event.

Figure 5-2 Power and Brownout Assertions vs VDDA Levels

Figure 5-2 Power and Brownout Assertions vs VDDA Levels

5.15.2.1.2 VDD Levels

The VDD supply has two monitors:

- Power-OK (POK)

- Brownout reset (BOR)

The POK monitor is used to keep the digital circuitry in reset until the VDD power supply reaches an acceptable operational level. The digital reset is only released when the POR has deasserted and the POK monitor for each supply indicates that power levels are in operational ranges. The BOR monitor is used to generate a reset to the device or assert an interrupt if the VDD supply drops below its operational range.

NOTE

VDDA BOR and VDD BOR events are a combined BOR to the system logic, such that if either BOR event occurs, the following bits are affected:

- The BORRIS bit in the Raw Interrupt Status (RIS) register, System Control offset 0x050

- The BORMIS bit in the Masked Interrupt Status and Clear (MISC) register, System Control offset 0x058. This bit is set only if the BORIM bit in the Interrupt Mask Control (IMC) register has been set.

- The BOR bit in the Reset Cause (RESC) register, System Control offset 0x05C. This bit is set only if either of the BOR events have been configured to initiate a reset.

In addition, the following bits control both BOR events:

- The BORIM bit in the Interrupt Mask Control (IMC) register, System Control offset 0x054

- The VDDA_UBOR0 and VDD_UBOR0 bits in the Power-Temperature Cause (PWRTC) register

See the System Control chapter of the MSP432E4 SimpleLink™ Microcontrollers Technical Reference Manual for more information on how to configure these registers.

Figure 5-3 shows the relationship between VDD, POK, POR, and a BOR event.

Figure 5-3 Power and Brownout Assertions vs VDD Levels

Figure 5-3 Power and Brownout Assertions vs VDD Levels

5.15.2.1.3 VDDC Levels

The VDDC supply has one monitor, the Power-OK (POK). The POK monitor is used to keep the digital circuitry in reset until the VDDC power supply reaches an acceptable operational level. The digital reset is only released when the power-on reset has deasserted and the POK monitor for each supply indicates that power levels are in operational ranges. Figure 5-4 shows the relationship between POK and VDDC.

Figure 5-4 POK Assertion vs VDDC

Figure 5-4 POK Assertion vs VDDC

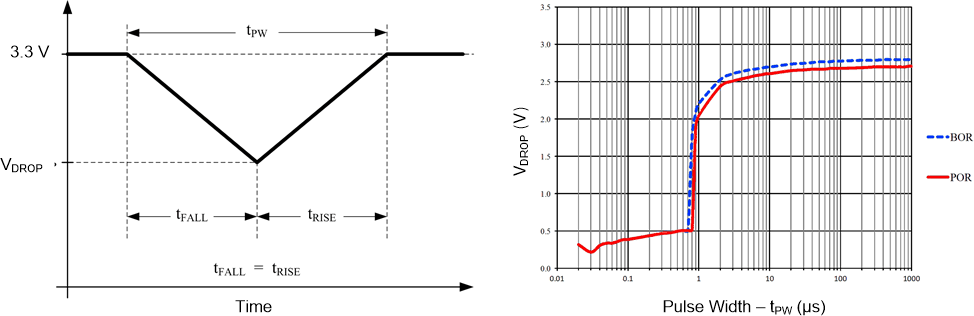

5.15.2.1.4 VDD Glitch Response

Figure 5-5 shows the response of the BOR and the POR circuit to glitches on the VDD supply.

Figure 5-5 POR-BOR VDD Glitch Response

Figure 5-5 POR-BOR VDD Glitch Response

5.15.2.1.5 VDD Droop Response

Figure 5-6 shows the response of the BOR and the POR monitors to a drop on the VDD supply.

Figure 5-6 POR-BOR VDD Droop Response

Figure 5-6 POR-BOR VDD Droop Response

5.15.3 Reset Timing

Table 5-4 lists the reset characteristics.

Table 5-4 Reset Characteristics

over operating free-air temperature (unless otherwise noted)| NO. | PARAMETER | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| R1 | tDPORDLY | Digital POR to internal reset assertion delay (see Figure 5-7) | 0.44 | 126 | µs | |

| R2 | tIRTOUT (1) (2) | Standard internal reset time | 14 | 16 | ms | |

| Internal reset time with recovery code repair (program or erase)(3) | 24.4 | 6400(7) | ||||

| R3 | tBOR0DLY (1) | BOR0 to internal reset assertion delay (6) (see Figure 5-8) | 0.44 | 125 | µs | |

| R4 | tRSTMIN | Minimum RST pulse duration | 0.25(4) or 100(5) | µs | ||

| R5 | tIRHWDLY | RST to internal reset assertion delay (see Figure 5-9) | 0.85 | µs | ||

| R6 | tIRSWR (1) | Internal reset time-out after software-initiated system reset (see Figure 5-10) | 2.44 | µs | ||

| R7 | tIRWDR (1) | Internal reset time-out after watchdog reset (see Figure 5-11) | 2.44 | µs | ||

| R8 | tIRMFR (1) | Internal reset time-out after MOSC failure reset (see Figure 5-12) | 2.44 | µs | ||

Figure 5-7 Digital Power-On Reset Timing

Figure 5-7 Digital Power-On Reset Timing

The digital power-on reset is released only when the analog power-on reset has deasserted and the Power-OK monitor for each supply indicates that power levels are in operational ranges.

Figure 5-8 Brownout Reset Timing

Figure 5-8 Brownout Reset Timing

Figure 5-9 External Reset Timing (RST)

Figure 5-9 External Reset Timing (RST)

Figure 5-10 Software Reset Timing

Figure 5-10 Software Reset Timing

Figure 5-11 Watchdog Reset Timing

Figure 5-11 Watchdog Reset Timing

Figure 5-12 MOSC Failure Reset Timing

Figure 5-12 MOSC Failure Reset Timing

5.15.4 Clock Specifications

The following sections provide specifications on the various clock sources and mode.

5.15.4.1 PLL Specifications

Table 5-5 lists the PLL characteristics.

NOTE

If the integrated Ethernet PHY is used, fREF_XTAL and fREF_EXT must be 25 MHz.

Table 5-5 Phase Locked Loop (PLL) Characteristics

over operating free-air temperature (unless otherwise noted)| PARAMETER | MIN | MAX | UNIT | ||

|---|---|---|---|---|---|

| fREF_XTAL | Crystal reference | 5 | 25 | MHz | |

| fREF_EXT | External clock reference | 5 | 25 | MHz | |

| fPLLR | PLL VCO frequency at 1.2 V(2) | 100 | 480 | MHz | |

| fPLLS | PLL VCO frequency at 0.9 V(1) | 100 | 480 | MHz | |

| tREADY | PLL lock time | Enabling the PLL, when PLL is transitioning from power down to power up | 512 × (reference clock period) | µs | |

| When the PLL VCO frequency is changed (PLL is already enabled) | 128 × (reference clock period) | ||||

| Changing the OSCSRC between MOSC and PIOSC | 128 × (reference clock period) | ||||

5.15.4.1.1 PLL Configuration

The PLL is disabled by default during power-on reset and is enabled later by software if required. Software specifies the output divisor to set the system clock frequency and enables the PLL to drive the output. The PLL is controlled using the PLLFREQ0, PLLFREQ1, and PLLSTAT registers. Changes made to these registers do not become active until after the NEWFREQ bit in the RSCLKCFG register is enabled. The clock source for the main PLL is selected by configuring the PLLSRC field in the Run and Sleep Clock Configuration (RSCLKCFG) register. The PLL allows for the generation of system clock frequencies in excess of the reference clock provided. The reference clocks for the PLL are the PIOSC and the MOSC.

The PLL is controlled by two registers, PLLFREQ0 and PLLFREQ1. The PLL VCO frequency (fVCO) is determined through Equation 1.

where

- fIN = fXTAL / (Q+1)(N+1) or fPIOSC / (Q+1)(N+1)

- MDIV = MINT + (MFRAC / 1024)

The Q and N values are programmed in the PLLFREQ1 register. To reduce jitter, program MFRAC to 0x0.

When the PLL is active, the system clock frequency (SysClk) is calculated using Equation 2.

The PLL system divisor factor (PSYSDIV) must be set as 1. Table 5-6 lists examples of the system clock frequency.

Table 5-6 Examples of System Clock Frequencies

| fVCO (MHz) | Q | PSYSDIV + 1 | System Clock (SYSCLK) Frequency (MHz) |

|---|---|---|---|

| 480 | 2 | 2 | 120 |

| 480 | 3 | 2 | 80 |

| 480 | 4 | 2 | 60 |

| 480 | 5 | 2 | 48 |

| 320 | 2 | 2 | 80 |

| 320 | 3 | 2 | 53 |

| 320 | 4 | 2 | 40 |

If the main oscillator provides the clock reference to the PLL, the translation provided by hardware and used to program the PLL is available for software in the PLL Frequency n (PLLFREQn) registers. The internal translation provides a translation within ±1% of the targeted PLL VCO frequency. Table 5-7 shows the actual PLL frequency and error for a given crystal choice.

Table 5-7 provides examples of the programming expected for the PLLFREQ0 and PLLFREQ1 registers. The CRYSTAL FREQUENCY column specifies the input crystal frequency and the PLL FREQUENCY column displays the PLL frequency given the values of MINT and N, when Q = 0.

Table 5-7 Actual PLL Frequency(1)

| CRYSTAL FREQUENCY (MHz) | MINT | N | REFERENCE FREQUENCY (MHz)(2) | PLL FREQUENCY (MHz) | |

|---|---|---|---|---|---|

| DECIMAL VALUE | HEXADECIMAL VALUE | ||||

| 5 | 64 | 0x40 | 0x0 | 5 | 320 |

| 6 | 160 | 0x35 | 0x2 | 2 | 320 |

| 8 | 40 | 0x28 | 0x0 | 8 | 320 |

| 10 | 32 | 0x20 | 0x0 | 10 | 320 |

| 12 | 80 | 0x50 | 0x2 | 4 | 320 |

| 16 | 20 | 0x14 | 0x0 | 16 | 320 |

| 18 | 160 | 0xA0 | 0x8 | 2 | 320 |

| 20 | 16 | 0x10 | 0x0 | 20 | 320 |

| 24 | 40 | 0x28 | 0x2 | 8 | 320 |

| 25 | 64 | 0x40 | 0x4 | 5 | 320 |

| 5 | 96 | 0x60 | 0x0 | 5 | 480 |

| 6 | 80 | 0x50 | 0x0 | 6 | 480 |

| 8 | 60 | 0x3C | 0x0 | 8 | 480 |

| 10 | 48 | 0x30 | 0x0 | 10 | 480 |

| 12 | 40 | 0x28 | 0x0 | 12 | 480 |

| 16 | 30 | 0x1E | 0x0 | 16 | 480 |

| 18 | 80 | 0x50 | 0x2 | 6 | 480 |

| 20 | 24 | 0x18 | 0x0 | 20 | 480 |

| 24 | 20 | 0x14 | 0x0 | 24 | 480 |

| 25 | 96 | 0x60 | 0x4 | 5 | 480 |

5.15.4.2 PIOSC Specifications

Table 5-8 lists the PIOSC characteristics.

Table 5-8 PIOSC Clock Characteristics

| PARAMETER | MIN | NOM | MAX | UNIT | |

|---|---|---|---|---|---|

| fPIOSC | Factory calibration, 0°C to 105°C: Internal 16-MHz precision oscillator frequency variance across voltage and temperature range when factory calibration is used |

±6% | |||

| Factory calibration, –40°C to <0°C | ±10% | ||||

| Recalibration: Internal 16-MHz precision oscillator frequency variance when recalibration is used at a specific temperature |

±1% | ||||

| tSTART | PIOSC start-up time(1) | 1 | µs | ||

5.15.4.3 Low-Frequency Oscillator Specifications

Table 5-9 lists the characteristics of the low-frequency oscillator.

Table 5-9 Low-Frequency Oscillator Characteristics

| PARAMETER | MIN | NOM | MAX | UNIT | |

|---|---|---|---|---|---|

| fLFIOSC | Internal low-frequency oscillator frequency | 10 | 33 | 75 | kHz |

5.15.4.4 Hibernation Low-Frequency Oscillator Specifications

Table 5-10 Hibernation External Oscillator (XOSC) Input Characteristics

| PARAMETER | MIN | NOM | MAX | UNIT | |

|---|---|---|---|---|---|

| fHIBXOSC (1) | Parallel resonance frequency | 32.768 | kHz | ||

| C1, C2 | External load capacitance on XOSC0, XOSC1 pins (2) | 12 | 24 | pF | |

| CPKG | Device package stray shunt capacitance (2) | 0.5 | pF | ||

| CPCB | PCB stray shunt capacitance (2) | 0.5 | pF | ||

| CSHUNT | Total shunt capacitance (2) | 4 | pF | ||

| ESR | Crystal effective series resistance, OSCDRV = 0 (3) | 50 | kΩ | ||

| Crystal effective series resistance, OSCDRV = 1 (3) | 75 | ||||

| DL | Oscillator output drive level | 0.25 | µW | ||

| tSTART | Oscillator start-up time, when using a crystal (5) | 600 | 1500 (4) | ms | |

| VIH | CMOS input high level, when using an external oscillator with VSupply > 3.3 V | 2.64 | V | ||

| CMOS input high level, when using an external oscillator with 1.8 V ≤ VSupply ≤ 3.3 V | 0.8 × VSupply | ||||

| VIL (6) | CMOS input low level, when using an external oscillator with 1.8 V ≤ VSupply ≤ 3.63 V | 0.2 × VSupply | V | ||

| VHYS (6) | CMOS input buffer hysteresis, when using an external oscillator with 1.8 V ≤ VSupply ≤ 3.63 V | 360 | 960 | 1390 | mV |

| DCHIBOSC_EXT | External single-ended (bypass) reference duty cycle | 30% | 70% | ||

Choose the load capacitors added on the board, C1 and C2, such that Equation 3 is satisfied (see Table 5-10 for typical values).

where

- CL = load capacitance specified by crystal manufacturer

- CSHUNT = CPKG + CPCB + C0 (total shunt capacitance seen across XOSC0 and XOSC1)

- CPKG, CPCB as measured across the XOSC0 and XOSC1 pins excluding the crystal

- Clear the OSCDRV bit in the Hibernation Control (HIBCTL) register for C1,2 ≤ 18 pF

- Set the OSCDRV bit for C1,2 > 18 pF

- C0 = Shunt capacitance of crystal specified by the crystal manufacturer

Table 5-11 lists the characteristics of the Hibernation module low-frequency oscillator.

Table 5-11 Hibernation Internal Low-Frequency Oscillator Clock Characteristics

| PARAMETER | MIN | NOM | MAX | UNIT | |

|---|---|---|---|---|---|

| fHIBLFIOSC | Internal low-frequency hibernation oscillator frequency | 10 | 33 | 90 | kHz |

5.15.4.5 Main Oscillator Specifications

Table 5-12 lists the required characteristics of the main oscillator input.

Table 5-12 Main Oscillator Input Characteristics

over operating free-air temperature (unless otherwise noted)(2)| PARAMETER | MIN | NOM | MAX | UNIT | ||

|---|---|---|---|---|---|---|

| fMOSC | Parallel resonance frequency | 4 (1) | 25 | MHz | ||

| fREF_XTAL_BYPASS | External clock reference (PLL in BYPASS mode) | 0 | 120 | MHz | ||

| C1, C2 | External load capacitance on OSC0, OSC1 pins (3) | 12 | 24 | pF | ||

| CPKG | Device package stray shunt capacitance (3) | 0.5 | pF | |||

| CPCB | PCB stray shunt capacitance (3) | 0.5 | pF | |||

| CSHUNT | Total shunt capacitance (3) | 4 | pF | |||

| ESR | Crystal effective series resistance | 4 MHz (4) (5) | 300 | Ω | ||

| 6 MHz (4) (5) | 200 | |||||

| 8 MHz (4) (5) | 130 | |||||

| 12 MHz (4) (5) | 120 | |||||

| 16 MHz (4) (5) | 100 | |||||

| 25 MHz (4) (5) | 50 | |||||

| DL | Oscillator output drive level(7) | OSCPWR | mW | |||

| TSTART | Oscillator start-up time, when using a crystal (6) | 18 | ms | |||

| VIH | CMOS input high level, when using an external oscillator | 0.65 × VDD | VDD | V | ||

| VIL | CMOS input low level, when using an external oscillator | GND | 0.35 × VDD | V | ||

| VHYS | CMOS input buffer hysteresis, when using an external oscillator | 150 | mV | |||

| DCOSC_EXT | External clock reference duty cycle | 45% | 55% | |||

The load capacitors added on the board, C1 and C2, should be chosen such that Equation 4 is satisfied (see Table 5-12 for typical values and Table 5-13 for detailed crystal parameter information).

where

- CL = load capacitance specified by crystal manufacturer

- CSHUNT = C0 + CPKG + CPCB (total shunt capacitance seen across OSC0 and OSC1 crystal inputs)

- CPKG, CPCB = Mutual capacitance as measured across the OSC0 and OSC1 pins excluding the crystal

- C0 = Shunt capacitance of crystal specified by the crystal manufacturer

Table 5-13 lists part numbers of crystals that have been simulated and confirmed to operate within the specifications in Table 5-12. Other crystals that have nearly identical crystal parameters can be expected to work as well.

In Table 5-13, the crystal parameters labeled C0, C1, and L1 are values that are obtained from the crystal manufacturer. These numbers are usually a result of testing a relevant batch of crystals on a network analyzer. The parameters labeled ESR, DL, and CL are maximum numbers usually available in the data sheet for a crystal.

Table 5-13 also includes three columns of Recommended Component Values. These values apply to system board components. C1 and C2 are the values in picofarads of the load capacitors that should be put on each leg of the crystal pins to ensure oscillation at the correct frequency. Rs is the value in kΩ of a resistor that is placed in series with the crystal between the OSC1 pin and the crystal pin. Rs dissipates some of the power so the Max Dl crystal parameter is not exceeded. Only use the recommended C1, C2, and Rs values with the associated crystal part. The values in the table were used in the simulation to ensure crystal start-up and to determine the worst-case drive level (WC DL). The value in the WC DL column should not be greater than the Max DL crystal parameter. The WC DL value can be used to determine if a crystal with similar parameter values but a lower Max DL value is acceptable.

Table 5-13 Crystal Parameters

| Manufacturer | Manufacturer Part Number | Holder | Package Size (mm × mm) | Frequency (MHz) | Crystal Specification (Tolerance / Stability) | Crystal Parameters | Recommended Component Values | WC DL (µW) | |||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Typical Values | Max Values | ||||||||||||||

| C0 (pF) | C1 (fF) | L1 (mH) | ESR (Ω) | Max DL (µW) | CL (pf) | C1 (pF) | C2 (pF) | Rs (kΩ) | |||||||

| NDK | NX8045GB-4.000M-STD-CJL-5 | NX8045GB | 8 × 4.5 | 4 | 30 / 50 ppm | 1.00 | 2.70 | 598.10 | 300 | 500 | 8 | 12 | 12 | 0 | 132 |

| FOX | FQ1045A-4 | 2-SMD | 10 × 4.5 | 4 | 30 / 30 ppm | 1.18 | 4.05 | 396.00 | 150 | 500 | 10 | 14 | 14 | 0 | 103 |

| NDK | NX8045GB-5.000M-STD-CSF-4 | NX8045GB | 8 × 4.5 | 5 | 30 / 50 ppm | 1.00 | 2.80 | 356.50 | 250 | 500 | 8 | 12 | 12 | 0 | 164 |

| NDK | NX8045GB-6.000M-STD-CSF-4 | NX8045GB | 8 × 4.5 | 6 | 30 / 50 ppm | 1.30 | 4.10 | 173.20 | 250 | 500 | 8 | 12 | 12 | 0 | 214 |

| FOX | FQ1045A-6 | 2-SMD | 10 × 4.5 | 6 | 30 / 30 ppm | 1.37 | 6.26 | 112.30 | 150 | 500 | 10 | 14 | 14 | 0 | 209 |

| NDK | NX8045GB-8.000M-STD-CSF-6 | NX8045GB | 8 × 4.5 | 8 | 30 / 50 ppm | 1.00 | 2.80 | 139.30 | 200 | 500 | 8 | 12 | 12 | 0 | 277 |

| FOX | FQ7050B-8 | 4-SMD | 7 × 5 | 8 | 30 / 30 ppm | 1.95 | 6.69 | 59.10 | 80 | 500 | 10 | 14 | 14 | 0 | 217 |

| ECS | ECS-80-16-28A-TR | HC49/US | 12.5 × 4.85 | 8 | 50 / 30 ppm | 1.82 | 4.90 | 85.70 | 80 | 500 | 16 | 24 | 24 | 0 | 298 |

| Abracon | AABMM-12.0000MHz-10-D-1-X-T | ABMM | 7.2 × 5.2 | 12 | 10 / 20 ppm | 2.37 | 8.85 | 20.5 | 50 | 500 | 10 | 12 | 12 | 2.0 (1) | 124 |

| NDK | NX3225GA-12.000MHZ-STD-CRG-2 | NX3225GA | 3.2 × 2.5 | 12 | 20 / 30 ppm | 0.70 | 2.20 | 81.00 | 100 | 200 | 8 | 12 | 12 | 2.5 | 147 |

| NDK | NX5032GA-12.000MHZ-LN-CD-1 | NX5032GA | 5 × 3.2 | 12 | 30 / 50 ppm | 0.93 | 3.12 | 56.40 | 120 | 500 | 8 | 12 | 12 | 0 | 362 |

| FOX | FQ5032B-12 | 4-SMD | 5 × 3.2 | 12 | 30 / 30 ppm | 1.16 | 4.16 | 42.30 | 80 | 500 | 10 | 14 | 14 | 0 | 370 |

| Abracon | AABMM-16.0000MHz-10-D-1-X-T | ABMM | 7.2 × 5.2 | 16 | 10 / 20 ppm | 3.00 | 11.00 | 9.30 | 50 | 500 | 10 | 12 | 12 | 2.0 (1) | 143 |

| Ecliptek | ECX-6595-16.000M | HC-49/UP | 13.3 × 4.85 | 16 | 15 / 30 ppm | 3.00 | 12.7 | 8.1 | 50 | 1000 | 10 | 12 | 12 | 2.0 (1) | 139 |

| NDK | NX3225GA-16.000MHZ-STD-CRG-2 | NX3225GA | 3.2 × 2.5 | 16 | 20 / 30 ppm | 1.00 | 2.90 | 33.90 | 80 | 200 | 8 | 12 | 12 | 2 | 188 |

| NDK | NX5032GA-16.000MHZ-LN-CD-1 | NX5032GA | 5 × 3.2 | 16 | 30 / 50 ppm | 1.02 | 3.82 | 25.90 | 120 (2) | 500 | 8 | 10 | 10 | 0 | 437 |

| ECS | ECS-160-9-42-CKM-TR | ECX-42 | 4 × 2.5 | 16 | 10 / 10 ppm | 1.47 | 3.90 | 25.84 | 60 | 300 | 9 | 12 | 12 | 0.5 | 289 |

| Abracon | AABMM-25.0000MHz-10-D-1-X-T | ABMM | 7.2 × 5.2 | 25 | 10 / 20 ppm | 3.00 | 11.00 | 3.70 | 50 | 500 | 10 | 12 | 12 | 2.0 (1) | 158 |

| Ecliptek | ECX-6593-25.000M | HC-49/UP | 13.3 × 4.85 | 25 | 15 / 30 ppm | 3.00 | 12.8 | 3.2 | 40 | 1000 | 10 | 12 | 12 | 1.5 (1) | 159 |

| NDK | NX3225GA-25.000MHZ-STD-CRG-2 | NX3225GA | 3.2 × 2.5 | 25 | 20 / 30 ppm | 1.10 | 4.70 | 8.70 | 50 | 200 | 8 | 12 | 12 | 2 | 181 |

| NDK | NX5032GA-25.000MHZ-LD-CD-1 | NX5032GA | 5 × 3.2 | 25 | 30 / 50 ppm | 1.3 | 5.1 | 7.1 | 70 | 500 | 8 | 10 | 10 | 1.0 (1) | 216 |

| 12 | 12 | 0.75 (3) | 269 | ||||||||||||

| AURIS | Q-25.000M-HC3225/4-F-30-30-E-12-TR | HC3225/4 | 3.2 × 2.5 | 25 | 30 / 30 ppm | 1.58 | 5.01 | 8.34 | 50 | 500 | 12 | 16 | 16 | 1 | 331 |

| FOX | FQ5032B-25 | 4-SMD | 5 × 3.2 | 25 | 30 / 30 ppm | 1.69 | 7.92 | 5.13 | 50 | 500 | 10 | 14 | 14 | 0.5 | 433 |

| TXC | 7A2570018 | NX5032GA | 5 × 3.2 | 25 | 20 / 25 ppm | 2.0 | 6.7 | 6.1 | 30 | 350 | 10 | 12 | 12 | 2.0 (3) | 124 |

5.15.4.6 Main Oscillator Specification WIth ADC

Table 5-14 lists the system clock characteristics with ADC operation.

Table 5-14 System Clock Characteristics With ADC Operation

| PARAMETER | MIN | NOM | MAX | UNIT | |

|---|---|---|---|---|---|

| fsysadc | System clock frequency when the ADC module is operating (when PLL is bypassed) | 16 | MHz | ||

5.15.4.7 System Clock Characteristics With USB Operation

Table 5-15 lists the system clock characteristics with USB operation.

Table 5-15 System Clock Characteristics With USB Operation

| PARAMETER | MIN | NOM | MAX | UNIT | |

|---|---|---|---|---|---|

| fsysusb | System clock frequency when the USB module is operating (MOSC must be the clock source, either with or without using the PLL) | 30 | MHz | ||

5.15.5 Sleep Modes

The following tables can be used to calculate the maximum wake time from sleep or deep sleep mode, depending on the specific application. Depending on the application configuration, each parameter, except for tFLASH, adds sequential latency to the wake time. Flash restoration happens in parallel to the other wake processes, and its wake time is normally absorbed by the other latencies. As an example, the wake time for a device in deep sleep mode with the PIOSC and PLL turned off and the flash and SRAM in low-power mode is calculated by Equation 5.

tFLASH does not contribute to this equation because the values of the other parameters are greater.

In sleep mode, the wake time due to a clock source is zero because the device uses the same clock configuration in run mode; thus, there is no latency involved with respect to the clocks.

Table 5-16 lists the wake-up times from sleep mode.

Table 5-16 Wake From Sleep Characteristics

over operating free-air temperature (unless otherwise noted)| NO. | PARAMETER | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| D1 | tPIOSC | Time to restore PIOSC as system clock in sleep mode | N/A | µs | ||

| D2 | tMOSC | Time to restore MOSC as system clock in sleep mode | N/A | µs | ||

| D3 | tPLL | Time to restore PLL as system clock in sleep mode | N/A | µs | ||

| D4 | tLDO | Time to restore LDO to 1.2 V in sleep mode | 39 | µs | ||

| D5 | tFLASH | Time to restore flash to active state from low-power state in sleep mode | 96 | µs | ||

| D6 | tSRAMLP | Time to restore SRAM to active state from low-power state in sleep mode | 15 | µs | ||

| D7 | tSRAMSTBY | Time to restore SRAM to active state from standby state in sleep mode | 15 | µs | ||

Table 5-16 lists the wake-up times from deep sleep mode.

Table 5-17 Wake From Deep Sleep Characteristics

over operating free-air temperature (unless otherwise noted)| NO. | PARAMETER | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| D8 | tPIOSCDS | Time to restore PIOSC as system clock in deep sleep mode | 14 | deep-sleep clock cycles | ||

| D9 | tMOSCDS | Time to restore MOSC as system clock in deep sleep mode | 18 | ms | ||

| D10 | tPLLDS | Time to restore PLL as system clock in deep sleep mode | 1 cycle of deep sleep clock + 512 cycles of PLL reference clock (1) | clock cycles | ||

| D11 | tLDODS | Time to restore LDO to 1.2 V in deep sleep mode | 39 | µs | ||

| D12 | tFLASHLPDS | Time to restore flash to active state from low-power state | 96 | µs | ||

| D13 | tSRAMLPDS | Time to restore SRAM to active state from low-power state | 15 | µs | ||

| D14 | tSRAMSTBYDS | Time to restore SRAM to active state from standby state | 15 | µs | ||

5.15.6 Hibernation Module

The Hibernation module requires special system implementation considerations because it is intended to power down all other sections of its host device. See the Hibernation Module chapter of the MSP432E4 SimpleLink™ Microcontrollers Technical Reference Manual.

Table 5-18 lists the required characteristics of the Hibernation module battery.

Table 5-18 Hibernation Module Battery Characteristics

over operating free-air temperature (unless otherwise noted)| PARAMETER | MIN | NOM | MAX | UNIT | ||

|---|---|---|---|---|---|---|

| VBAT | Battery supply voltage | 1.8 | 3.0 | 3.6 | V | |

| VBATRMP | VBAT battery supply voltage ramp time | 0 | 0.7 | V/µs | ||

| VLOWBAT | Low-battery detect voltage | VBATSEL = 0x0 | 1.8 | 1.9 | 2.0 | V |

| VBATSEL = 0x1 | 2.0 | 2.1 | 2.2 | |||

| VBATSEL = 0x2 | 2.2 | 2.3 | 2.4 | |||

| VBATSEL = 0x3 | 2.4 | 2.5 | 2.6 | |||

Table 5-19 lists the timing characteristics of the HIB module.

Table 5-19 Hibernation Module Characteristics

over operating free-air temperature (unless otherwise noted) (see Figure 5-13)| NO. | PARAMETER | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| H1 | tWAKE | WAKE assertion time | 100 | ns | ||

| H2 | tWAKE_TO_HIB | WAKE assert to HIB desassert (wake-up time) | 1 | HIB module clock period | ||

| H3 | tVDD_RAMP | VDD ramp to 3.0 V | See (1) | µs | ||

| H4 | tVDD_CODE | VDD at 3 V to internal POR deassert; first instruction executes | 500 | µs | ||

| H5 | DCRTCCLK | Duty cycle for RTCCLK output signal, when using a 32.768‑kHz crystal | 40% | 60% | ||

| Duty cycle for RTCCLK output signal, when using a 32.768‑kHz external single-ended (bypass) clock source | 30% | 70% | ||||

Figure 5-13 Hibernation Module Timing

Figure 5-13 Hibernation Module Timing

Table 5-20 lists the characteristics of the HIB module tamper detection.

Table 5-20 Hibernation Module Tamper I/O Characteristics

over operating free-air temperature (unless otherwise noted)| PARAMETER | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|

| RTPU | TMPRn pullup resistor | 3.5 | 4.4 | 5.2 | MΩ |

| tSP | TMPRn pulse duration with short glitch filter | 62 | µs | ||

| tLP | TMPRn pulse duration with long glitch filter | 94 | ms | ||

| tNMIS | TMPRn assertion to NMI (short glitch filter) | 95 | µs | ||

| tNMIL | TMPRn assertion to NMI (long glitch filter) | 94 | ms | ||

| VIH | TMPRn high-level input voltage when operating from VBAT | VBAT × 0.8 | V | ||

5.15.7 Flash Memory

Table 5-21 lists the characteristics of the flash memory.

Table 5-21 Flash Memory Characteristics

over operating free-air temperature (unless otherwise noted)| PARAMETER | MIN | TYP | MAX | UNIT | ||

|---|---|---|---|---|---|---|

| PECYC | Number of program and erase cycles | 100000 | cycles | |||

| tRET | Data retention with 100% power-on hours at TJ = 85°C | 20 | years | |||

| tRET_EXTEMP | Data retention with 10% power-on hours at TJ = 125°C and 90% power-on hours at TJ = 100°C | 11 | years | |||

| tPROG64 | Program time for double-word-aligned (64 bits) data | 30 | 100 | 300 | µs | |

| tERASE | Page erase time | <1k cycles | 8 | 15 | ms | |

| 10k cycles | 15 | 40 | ||||

| 100k cycles | 75 | 500 | ||||

| tME | Mass erase time | <1k cycles | 10 | 25 | ms | |

| 10k cycles | 20 | 70 | ||||

| 100k cycles | 300 | 2500 | ||||

5.15.8 EEPROM

Table 5-22 lists the characteristics of the EEPROM.

Table 5-22 EEPROM Characteristics

over operating free-air temperature (unless otherwise noted)| PARAMETER | MIN | TYP | MAX | UNIT | ||

|---|---|---|---|---|---|---|

| EPECYC | Number of mass program and erase cycles of a single word | 500000 | cycles | |||

| ETRET | Data retention with 100% power-on hours at TJ = 85°C | 20 | years | |||

| ETRET_EXTEMP | Data retention with 10% power-on hours at TJ = 125°C and 90% power-on hours at TJ = 100°C | 11 | years | |||

| ETPROG | Program time for 32 bits of data with memory space available | 110 | 600 | µs | ||

| Program time for 32 bits of data in which a copy to the copy buffer is required, the copy buffer has space, and less than 10% of EEPROM endurance used | 30 | ms | ||||

| Program time for 32 bits of data in which a copy to the copy buffer is required, the copy buffer has space, and more than 90% of EEPROM endurance used | 900 | |||||

| Program time for 32 bits of data in which a copy of the copy buffer is required, the copy buffer requires an erase, and less than 10% of EEPROM endurance used | 60 | |||||

| Program time for 32 bits of data a copy to the copy buffer is required, the copy buffer requires an erase, and more than 90% of EEPROM endurance used | 1800 | |||||

| ETREAD | Read access time | 7 + 2EWS | 9 + 4EWS | system clock cycles | ||

| ETME | Mass erase time | <1k cycles | 8 | 15 | ms | |

| 10k cycles | 15 | 40 | ||||

| 100k cycles | 75 | 500 | ||||

5.15.9 Input/Output Pin Characteristics

NOTE

All GPIO signals are 3.3-V tolerant, except for PB1 (USB0VBUS) which is 5-V tolerant. See the General-Purpose Input/Outputs (GPIOs) chapter of the MSP432E4 SimpleLink™ Microcontrollers Technical Reference Manual for more information on GPIO configuration.

Two types of pads are provided on the device:

- Fast GPIO pads: These pads provide variable, programmable drive strength and optimized voltage output levels.

- Slow GPIO pads: These pads provide 2-mA drive strength and are designed to be sensitive to voltage inputs. The following GPIOs port pins are designed with slow GPIO pads:

- PJ1

NOTE

Port pins PL6 and PL7 operate as fast GPIO pads, but have 4-mA drive capability only. GPIO register controls for drive strength, slew rate, and open drain have no effect on these pins. The following registers have no effect: GPIODR2R, GPIODR4R, GPIODR8R, GPIODR12R, GPIOSLR, and GPIOODR.

NOTE

Port pins PM[7:4] operate as fast GPIO pads but support only 2-, 4-, 6-, and 8-mA drive capability. All standard GPIO register controls, except for the GPIODR12R register, apply to these port pins.

Table 5-23 lists the characteristics of the fast GPIOs.

Table 5-23 Fast GPIO Module Characteristics

over operating free-air temperature (unless otherwise noted) (1) (2) (3) (4)| PARAMETER | MIN | TYP | MAX | UNIT | ||

|---|---|---|---|---|---|---|

| CLGPIO | Capacitive loading for measurements given in this table (5) | 50 | pF | |||

| RGPIOPU | Fast GPIO internal pullup resistor (6) | 12.1 | 16.0 | 20.2 | kΩ | |

| RGPIOPU4MA | Fast GPIO PL6 and PL7 (4 mA only) pullup resistor | 25 | 40 | kΩ | ||

| RGPIOPD | Fast GPIO internal pulldown resistor (6) | 13.0 | 20.5 | 35.5 | kΩ | |

| RGPIOPD4MA | Fast GPIO PL6 and PL7 (4 mA only) pulldown resistor | 10 | 14.3 | 17 | kΩ | |

| ILKG+ | Fast GPIO input leakage current, 0 V ≤ VIN ≤ VDD GPIO pins(7) | 400 | nA | |||

| Fast GPIO input leakage current, 0 V < VIN ≤ VDD, fast GPIO pins configured as ADC or analog comparator inputs | 400 | |||||

| IINJ- | DC injection current, VIN ≤ 0 V | 60 | µA | |||

| IMAXINJ- | Maximum negative injection if not voltage protected (4) | –0.5 | mA | |||

| tGPIOR | Fast GPIO rise time(8) | 2-mA drive | 7.85 | 11.73 | ns | |

| 4-mA drive | 4.15 | 6.35 | ||||

| 8-mA drive | 2.33 | 3.73 | ||||

| 8-mA drive with slew rate control | 3.77 | 5.76 | ||||

| 10-mA drive | 1.98 | 3.22 | ||||

| 12-mA drive | 1.75 | 2.9 | ||||

| tGPIOF | Fast GPIO fall time (9) | 2-mA drive | 10.3 | 16.5 | ns | |

| 4-mA drive | 5.15 | 8.29 | ||||

| 8-mA drive | 2.58 | 4.16 | ||||

| 8-mA drive with slew rate control | 3.54 | 5.55 | ||||

| 10-mA drive | 2.07 | 3.34 | ||||

| 12-mA drive | 1.73 | 2.78 | ||||

Table 5-24 lists the characteristics of the slow GPIOs.

Table 5-24 Slow GPIO Module Characteristics

over operating free-air temperature (unless otherwise noted)(1)(2)(3)| PARAMETER | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|

| CLGPIO | Capacitive loading for measurements given in this table(4) | 50 | pF | ||

| RGPIOPU | Slow GPIO internal pullup resistor | 13.8 | 20.0 | 31.4 | kΩ |

| RGPIOPD | Slow GPIO internal pulldown resistor | 13.0 | 20.5 | 35.5 | kΩ |

| ILKG+ | Slow GPIO input leakage current, 0 V ≤ VIN ≤ VDD, GPIO pins(5) | 3.25 | nA | ||

| Slow GPIO input leakage current, 0 V < VIN ≤ VDD, GPIO pins configured as ADC or analog comparator inputs | 3.25 | ||||

| IINJ- | DC injection current, VIN ≤ 0 V | 3.42 | µA | ||

| tGPIOR | Slow GPIO rise time, 2-mA drive(6) | 19.3 | 29.8 | ns | |

| tGPIOF | Slow GPIO fall time, 2-mA drive(7) | 12.8 | 21.1 | ns | |

5.15.9.1 Types of I/O Pins and ESD Protection

CAUTION

All device I/Os pins, except for PB1, are NOT 5-V tolerant; voltages in excess of the limits in Section 5.4 can permanently damage the device. PB1 is used for the USB0VBUS signal, which requires a 5-V input.

5.15.9.1.1 Hibernate WAKE pin

The Hibernate WAKE pin uses ESD protection, similar to the one shown in Figure 5-14. This ESD protection prevents a direct path between this pad and any power supply rails in the device. The WAKE pad input voltage should be kept inside the maximum ratings specified in Section 5.1 to ensure current leakage and current injections are within acceptable range. Table 5-25 lists current leakages and current injection for these pins.

Figure 5-14 ESD Protection

Figure 5-14 ESD Protection

Table 5-25 Pad Voltage and Current Characteristics for Hibernate WAKE Pin

over operating free-air temperature (unless otherwise noted)(1)(2)| PARAMETER | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|

| ILKG+ | Positive I/O leakage for VDD ≤ VIN ≤ VBAT + 0.3 V | 300 | nA | ||

| ILKG- | Negative I/O leakage for –0.3 V ≤ VIN ≤ 0 V(3) | 43.3 | µA | ||

| IINJ+ | Maximum positive injection if not voltage protected | 2 | mA | ||

| IINJ- | Maximum negative injection if not voltage protected (4) | –0.5 | mA | ||

5.15.9.1.2 Nonpower I/O Pins

Most nonpower I/Os (with the exception of the I/O pad for Hibernate WAKE input) have ESD protection as shown in Figure 5-15.

These I/Os have an ESD clamp to ground and a diode connection to the corresponding power supply rail. To prevent potential damage to the device, follow the specifications in Table 5-26 for the voltage and current of these I/Os. In addition, comply with that the ADC external reference specifications in Table 5-33 to prevent gain error.

Figure 5-15 ESD Protection for Nonpower Pins (Except WAKE Signal)

Figure 5-15 ESD Protection for Nonpower Pins (Except WAKE Signal)

Table 5-26 Nonpower I/O Pad Voltage and Current Characteristics

over operating free-air temperature (unless otherwise noted) (1) (2) (3)| PARAMETER | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|

| VIO | I/O pad voltage limits if voltage protected | –0.3 | VDD | VDD + 0.3 | V |

| ILKG+ | Positive I/O leakage for VDD ≤ VIN ≤VIO (4) | 400 | nA | ||

| ILKG- | Negative I/O leakage for VIO MIN ≤ VIN ≤ 0V (4) | 60 | µA | ||

| IINJ+ | Maximum positive injection if not voltage protected(5) | 2 | mA | ||

| IINJ- | Maximum negative injection if not voltage protected(5) | –0.5 | mA | ||

5.15.10 External Peripheral Interface (EPI)

Table 5-27 lists the load conditions used to characterize the EPI interface.

Table 5-27 EPI Interface Load Conditions

| SIGNALS | LOAD VALUE (CL) |

|---|---|

| EPI0S[35:0] SDRAM interface | 30 pF |

| EPI0S[35:0] General-Purpose interface | |

| EPI0S[35:0] Host-Bus interface | |

| EPI0S[35:0] PSRAM interface | 40 pF |

When the EPI module is in SDRAM mode, EPI CLK (EPI0S31) must be configured to 12 mA. The EPI data bus can be configured to 8 mA. Table 5-28 lists the rise and fall times in SDRAM mode.

Table 5-28 EPI SDRAM Characteristics

over operating free-air temperature (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| tSDRAMR | EPI rise time (from 20% to 80% of VDD) | 12-mA drive, CL = 30 pF | 2 | 3 | ns | |

| tSDRAMF | EPI fall time (from 80% to 20% of VDD) | 12-mA drive, CL = 30 pF | 2 | 3 | ns | |

Table 5-29 lists the switching characteristics of the SDRAM interface.

Table 5-29 EPI SDRAM Interface Characteristics

over operating free-air temperature (unless otherwise noted) (1) (see Figure 5-16, Figure 5-17, and Figure 5-18)| NO. | PARAMETER | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| E1 | tCK | SDRAM clock period | 16.67 | ns | ||

| E2 | tCH | SDRAM clock high time | 8.33 | ns | ||

| E3 | tCL | SDRAM clock low time | 8.33 | ns | ||

| E4 | tCOV | CLK to output valid | 4 | ns | ||

| E5 | tCOI | CLK to output invalid | 4 | ns | ||

| E6 | tCOT | CLK to output tristate | 4 | ns | ||

| E7 | tS | Input set up to CLK | 8.5 | ns | ||

| E8 | tH | CLK to input hold | 0 | ns | ||

| E9 | tPU | Power-up time | 100 | µs | ||

| E10 | tRP | Precharge all banks | 20 | ns | ||

| E11 | tRFC | Auto refresh | 66 | ns | ||

| E12 | tMRD | Program mode register | 2 | EPI CLK | ||

Figure 5-17 SDRAM Read Timing

Figure 5-17 SDRAM Read Timing

Figure 5-18 SDRAM Write Timing

Figure 5-18 SDRAM Write Timing

Table 5-30 lists the characteristics of the Host-Bus 8 and Host-Bus 16 interface.

Table 5-30 EPI Host-Bus 8 and Host-Bus 16 Interface Characteristics

over operating free-air temperature (unless otherwise noted) (see Figure 5-19, Figure 5-20, Figure 5-21, and Figure 5-22)| NO. | PARAMETER | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| E14 | tISU | Read data set up time | 10 | ns | ||

| E15 | tIH | Read data hold time | 0 | ns | ||

| E16 | tDV | WRn to write data valid | 3.6 | ns | ||

| E17 | tDI | Data hold from WRn invalid | 1 | EPI clock cycles | ||

| E18 | tOV | ALE/CSn to output valid | 4 | ns | ||

| E19 | tOINV | CSn to output invalid | 4 | ns | ||

| E20 | tSTLOW | WRn / RDn strobe duration low | 1 | EPI clock cycles | ||

| E21 | tALEHIGH | ALE duration high | 1 | EPI clock cycles | ||

| E22 | tCSLOW | CSn duration low | 2 | EPI clock cycles | ||

| E23 | tALEST | ALE rising to WRn / RDn strobe falling | 2 | EPI clock cycles | ||

| E24 | tALEADD | ALE falling to Address high impedance | 1 | EPI clock cycles | ||

Figure 5-19 Host-Bus 8/16 Asynchronous Mode Read Timing

Figure 5-19 Host-Bus 8/16 Asynchronous Mode Read Timing

Figure 5-20 Host-Bus 8/16 Asynchronous Mode Write Timing

Figure 5-20 Host-Bus 8/16 Asynchronous Mode Write Timing

Figure 5-21 Host-Bus 8/16 Mode Asynchronous Muxed Read Timing

Figure 5-21 Host-Bus 8/16 Mode Asynchronous Muxed Read Timing

Figure 5-22 Host-Bus 8/16 Mode Asynchronous Muxed Write Timing

Figure 5-22 Host-Bus 8/16 Mode Asynchronous Muxed Write Timing

Table 5-31 lists the switching characteristics of the general-purpose interface.

Table 5-31 EPI General-Purpose Interface Characteristics

over operating free-air temperature (unless otherwise noted) (see Figure 5-23)| NO. | PARAMETER | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| E25 | tCK | General-purpose clock period | 16.67 | ns | ||

| E26 | tCH | General-purpose clock high time | 8.33 | ns | ||

| E27 | tCL | General-purpose clock low time | 8.33 | ns | ||

| E28 | tISU | Input signal set up time to rising clock edge | 8.50 | ns | ||

| E29 | tIH | Input signal hold time from rising clock edge | 0 | ns | ||

| E30 | tDV | Falling clock edge to output valid | 4 | ns | ||

| E31 | tDI | Falling clock edge to output invalid | 4 | ns | ||

NOTE:

This figure shows accesses when the FRM50 bit is clear, the FRMCNT field is 0x0, and the WR2CYC bit is clear.Table 5-32 lists the switching characteristics of the PSRAM interface.

Table 5-32 EPI PSRAM Interface Characteristics

over operating free-air temperature (unless otherwise noted) (see Figure 5-24 and Figure 5-25)| NO. | PARAMETER | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| E33 | tEPICLK | EPI_CLK period | 20 | ns | ||

| E34 | tRTFT | EPI_CLK rise or fall time | 1.8 | ns | ||

| E35 | tOV | Falling EPI_CLK to address/write data or control output valid (1) | 4.5 | 20 | ns | |

| E36 | tHT | Falling EPI_CLK to address/write data or control hold time (1) | 2 | ns | ||

| E37 | tSUP | Read data setup time from EPI_CLK rising | 9 | ns | ||

| E38 | tDH | Read data output hold from EPI_CLK rising | 0 | ns | ||

| E39 | tIRV | iRDY setup time | 9 | ns | ||

| E40 | tIRH | iRDY hold time | 9 | ns | ||

Figure 5-24 PSRAM Single Burst Read

Figure 5-24 PSRAM Single Burst Read

Figure 5-25 PSRAM Single Burst Write

Figure 5-25 PSRAM Single Burst Write

5.15.11 Analog-to-Digital Converter (ADC)

Table 5-33 lists the electrical characteristics for the ADC at 1 Msps.

Table 5-33 Electrical Characteristics for ADC at 1 Msps

VREF+ = 3.3 V, fADC = 16 MHz (unless otherwise noted)(1)| PARAMETER | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|

| Power supply requirements | |||||

| VDDA | ADC supply voltage | 2.97 | 3.3 | 3.63 | V |

| GNDA | ADC ground voltage | 0 | V | ||

| VDDA and GNDA voltage reference | |||||

| CREF | Voltage reference decoupling capacitance | 1.0 // 0.01 (2) | µF | ||

| External voltage reference input | |||||

| VREFA+ | Positive external voltage reference for ADC, when VREF field in the ADCCTL register is 0x1(3) | 2.4 | VDDA | VDDA | V |

| VREFA- | Negative external voltage reference for ADC, when VREF field in the ADCCTL register is 0x1(3) | GNDA | GNDA | 0.3 | V |

| IVREF | Current on VREF+ input, using external VREF+ = 3.3 V | 330.5 | 440 | µA | |

| ILVREF | DC leakage current on VREF+ input when external VREF disabled | 2.0 | µA | ||

| CREF | External reference decoupling capacitance (3) | 1.0 // 0.01 (2) | µF | ||

| Analog input | |||||

| VADCIN | Single-ended, full-scale analog input voltage, internal reference (4) (5) | 0 | VDDA | V | |

| Differential, full-scale analog input voltage, internal reference (4)(6) | –VDDA | VVDDA | |||

| Single-ended, full-scale analog input voltage, external reference (3) (5) | VREFA- | VREFA+ | |||

| Differential, full-scale analog input voltage, external reference(3)(7) | –(VREFA+ – VREFA-) | VREFA+ – VREFA- | |||

| VINCM | Input common-mode voltage, differential mode(8) | [(VREFA+ + VREFA-) / 2] ±0.025 | V | ||

| IL | ADC input leakage current(9) | 2.0 | µA | ||

| RADC | ADC equivalent input resistance (9) | 2.5 | kΩ | ||

| CADC | ADC equivalent input capacitance (9) | 10 | pF | ||

| RS | Analog source resistance (9) | 500 | Ω | ||

| Sampling dynamics | |||||

| fADC | ADC conversion clock frequency(10) | 16 | MHz | ||

| fCONV | ADC conversion rate |

|

1 | Msps | |

| tS | ADC sample time | 250 | ns | ||

| tC | ADC conversion time (11) | 1 | µs | ||

| tLT | Latency from trigger to start of conversion | 2 | ADC clock cycles | ||

| System performance when using external reference (12) (13) | |||||

| N | Resolution |

|

12 | bits | |

| INL | Integral nonlinearity error, over full input range | ±1.5 | ±3.0 | LSB | |

| DNL | Differential nonlinearity error, over full input range | ±0.8 | +2.0/–1.0 (14) | LSB | |

| EO | Offset error | ±1.0 | ±3.0 | LSB | |

| EG | Gain error (15) | ±2.0 | ±3.0 | LSB | |

| ET | Total unadjusted error, over full input range (16) | ±2.5 | ±4.0 | LSB | |

| System performance when using internal reference | |||||

| N | Resolution |

|

12 | bits | |

| INL | Integral nonlinearity error, over full input range | ±1.5 | ±3.0 | LSB | |

| DNL | Differential nonlinearity error, over full input range | ±0.8 | +2.0/–1.0 (14) | LSB | |

| EO | Offset error | ±5.0 | ±15.0 | LSB | |

| EG | Gain error (15) | ±10.0 | ±30.0 | LSB | |

| ET | Total unadjusted error, over full input range (16) | ±10.0 | ±30.0 | LSB | |

| Dynamic characteristics (12) (17) | |||||

| SNRD | Signal-to-noise-ratio, Differential input, VADCIN: –20 dB FS, 1 kHz (18) | 70 | 72 | dB | |

| SDRD | Signal-to-distortion ratio, Differential input, VADCIN: –3 dB FS, 1 kHz (18) (19) (20) | 72 | 75 | dB | |

| SNDRD | Signal-to-Noise+Distortion ratio, Differential input, VADCIN: –3 dB FS, 1 kHz (18) (21) (22) | 68 | 70 | dB | |

| SNRS | Signal-to-noise-ratio, Single-ended input, VADCIN: –20 dB FS, 1 kHz (23) | 60 | 65 | dB | |

| SDRS | Signal-to-distortion ratio, Single-ended input, VADCIN: –3 dB FS, 1 kHz (19) (20) | 70 | 72 | dB | |

| SNDRS | Signal-to-Noise+Distortion ratio, Single-ended input, VADCIN: –3 dB FS, 1 kHz (23) (21) (22) | 60 | 63 | dB | |

| Temperature sensor | |||||

| VTSENS | Temperature sensor voltage, junction temperature 25°C | 1.633 | V | ||

| STSENS | Temperature sensor slope at: –40°C to 105°C ambient (extended temperature part) |

–13.3 | mV/°C | ||

| ETSENS | Temperature sensor accuracy (24) at: –40°C to 105°C ambient (extended temperature part) |

±5 | °C | ||

Table 5-34 lists the electrical characteristics for the ADC at 2 Msps.

Table 5-34 Electrical Characteristics for ADC at 2 Msps

VREF+ = 3.3 V, fADC = 32 MHz, over operating free-air temperature (unless otherwise noted) (see Figure 5-26 and Figure 5-27)(1)| PARAMETER | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|

| Power supply requirements | |||||

| VDDA | ADC supply voltage | 2.97 | 3.3 | 3.63 | V |

| GNDA | ADC ground voltage | 0 | V | ||

| VDDA and GNDA voltage reference | |||||

| CREF | Voltage reference decoupling capacitance | 1.0 // 0.01 (2) | µF | ||

| External voltage reference input | |||||

| VREFA+ | Positive external voltage reference for ADC, when VREF field in the ADCCTL register is 0x1(3) | 2.4 | VDDA | VDDA | V |

| VREFA- | Negative external voltage reference for ADC, when VREF field in the ADCCTL register is 0x1 (3) | GNDA | GNDA | 0.3 | V |

| IVREF | Current on VREF+ input, using external VREF+ = 3.3 V | 330.5 | 440 | µA | |

| ILVREF | DC leakage current on VREF+ input when external VREF disabled | 2.0 | µA | ||

| CREF | External reference decoupling capacitance (3) | 1.0 // 0.01 (2) | µF | ||

| Analog input | |||||

| VADCIN | Single-ended, full-scale analog input voltage, internal reference(4)(5) | 0 | VDDA | V | |

| Differential, full-scale analog input voltage, internal reference (4)(6) | –VDDA | VVDDA | |||

| Single-ended, full-scale analog input voltage, external reference (3) (5) | VREFA- | VREFA+ | |||

| Differential, full-scale analog input voltage, external reference (3)(7) | –(VREFA+ – VREFA-) | VREFA+ – VREFA- | |||

| VINCM | Input common-mode voltage, differential mode (8) | [(VREFA+ + VREFA-) / 2] ±0.025 | V | ||

| IL | ADC input leakage current(9) | 2.0 | µA | ||

| RADC | ADC equivalent input resistance (9) | 2.5 | kΩ | ||

| CADC | ADC equivalent input capacitance (9) | 10 | pF | ||

| RS | Analog source resistance (9) | 250 | Ω | ||

| Sampling dynamics | |||||

| fADC | ADC conversion clock frequency(10) | 32 | MHz | ||

| fCONV | ADC conversion rate | 2 | Msps | ||

| tS | ADC sample time | 125 | ns | ||

| tC | ADC conversion time (11) | 0.5 | µs | ||

| tLT | Latency from trigger to start of conversion | 2 | ADC clock cycles | ||

| System performance when using external reference (12) (13) | |||||

| N | Resolution |

|

12 | bits | |

| INL | Integral nonlinearity error, over full input range | ±1.5 | ±3.0 | LSB | |

| DNL | Differential nonlinearity error, over full input range | ±0.8 | +2.0/–1.0 (14) | LSB | |

| EO | Offset error | ±1.0 | ±3.0 | LSB | |

| EG | Gain error (15) | ±2.0 | ±3.0 | LSB | |

| ET | Total unadjusted error, over full input range (16) | ±2.5 | ±4.0 | LSB | |

| System performance when using internal reference | |||||

| N | Resolution |

|

12 | bits | |

| INL | Integral nonlinearity error, over full input range | ±1.5 | ±3.0 | LSB | |

| DNL | Differential nonlinearity error, over full input range | ±0.8 | +2.0/–1.0 (14) | LSB | |

| EO | Offset error | ±5.0 | ±15.0 | LSB | |

| EG | Gain error (15) | ±10.0 | ±30.0 | LSB | |

| ET | Total unadjusted error, over full input range (16) | ±10.0 | ±30.0 | LSB | |

| Dynamic characteristics (17) (18) | |||||

| SNRD | Signal-to-noise-ratio, differential input, VADCIN: –20 dB FS, 1 kHz (19) | 68 | 72 | dB | |

| SDRD | Signal-to-distortion ratio, differential input, VADCIN: –3 dB FS, 1 kHz (19) (20) (21) | 70 | 75 | dB | |

| SNDRD | Signal-to-noise+distortion ratio, differential input, VADCIN: –3 dB FS, 1 kHz (19) (22) (23) | 65 | 70 | dB | |

| SNRS | Signal-to-noise-ratio, single-ended input, VADCIN: –20 dB FS, 1 kHz (24) | 58 | 65 | dB | |

| SDRS | Signal-to-distortion ratio, single-ended input, VADCIN: –3 dB FS, 1 kHz (20) (21) | 68 | 72 | dB | |

| SNDRS | Signal-to-noise+distortion ratio, single-ended input, VADCIN: –3 dB FS, 1 kHz (24) (22) (23) | 58 | 63 | dB | |

Figure 5-26 ADC External Reference Filtering

Figure 5-26 ADC External Reference Filtering

Figure 5-27 ADC Input Equivalency

Figure 5-27 ADC Input Equivalency

5.15.12 Synchronous Serial Interface (SSI)

Table 5-35 SSI Characteristics

over operating free-air temperature (unless otherwise noted) (see Figure 5-28, Figure 5-29, and Figure 5-30)| NO. | PARAMETER | MIN | TYP | MAX | UNIT | ||

|---|---|---|---|---|---|---|---|

| S1 | tCLK_PER | SSIClk cycle time | As master(1) | 16.67 | ns | ||

| As slave(2) | 100 | ||||||

| S2 | tCLK_HIGH | SSIClk high time | As master | 8.33 | ns | ||

| As slave | 50 | ||||||

| S3 | tCLK_LOW | SSIClk low time | As master | 8.33 | ns | ||

| As slave | 50 | ||||||

| S4 | tCLKR | SSIClk rise time(3) | 1.25 | ns | |||

| S5 | tCLKF | SSIClk fall time (3) | 1.25 | ns | |||

| S6 | tTXDMOV | Master mode: master Tx data output (to slave) valid time from edge of SSIClk | 4.00 | ns | |||

| S7 | tTXDMOH | Master mode: master Tx data output (to slave) hold time after next SSIClk | 0.60 | ns | |||

| S8 | tRXDMS | Master mode: master Rx data In (from slave) setup time | 7.89 | ns | |||

| S9 | tRXDMH | Master mode: master Rx data In (from slave) hold time | 0 | ns | |||

| S10 | tTXDSOV | Slave mode: master Tx data output (to master) valid time from edge of SSIClk | 47.60(4) | ns | |||

| S11 | tTXDSOH | Slave mode: slave Tx data output (to master) hold time from next SSIClk | 37.4(5) | ns | |||

| S13 | tRXDSSU | Slave mode: Rx data in (from master) setup time | 0 | ns | |||

| S14 | tRXDSH | Slave mode: Rx data in (from master) hold time | 37.03(6) | ns | |||

Figure 5-28 SSI Timing for TI Frame Format (FRF = 01), Single Transfer Timing Measurement

Figure 5-28 SSI Timing for TI Frame Format (FRF = 01), Single Transfer Timing Measurement

Figure 5-29 Master Mode SSI Timing for SPI Frame Format (FRF = 00), With SPH = 1

Figure 5-29 Master Mode SSI Timing for SPI Frame Format (FRF = 00), With SPH = 1

Figure 5-30 Slave Mode SSI Timing for SPI Frame Format (FRF = 00), With SPH = 1

Figure 5-30 Slave Mode SSI Timing for SPI Frame Format (FRF = 00), With SPH = 1

Table 5-36 lists the characteristics for Bi-SSI and Quad-SSI.

Table 5-36 Bi- and Quad-SSI Characteristics(1)

over operating free-air temperature (unless otherwise noted)| NO. | PARAMETER | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| S15 | tCLK_PER | SSIClk cycle time, as master (2) | 16.67 | ns | ||

| S16 | tCLK_HIGH | SSIClk high time, as master | 8.33 | ns | ||

| S17 | tCLK_LOW | SSIClk low time, as master | 8.33 | ns | ||

| S18 | tCLKR | SSIClk rise time (3) | 1.25 | ns | ||

| S19 | tCLKF | SSIClk fall time (3) | 1.25 | ns | ||

| S20 | tTXDMOV | Master mode: master SSInXDATn data output (to slave) valid time from edge of SSIClk | 4.04 | ns | ||

| S21 | tTXDMOH | Master mode: master SSInXDATn data output (to slave) hold time after next SSIClk | 0.60 | ns | ||

| S22 | tRXDMS | Master mode: master SSInXDATn data in (from slave) setup time | 5.78 | ns | ||

| S23 | tRXDMH | Master mode: master SSInXDATn data in (from slave) hold time | 0 | ns | ||

5.15.13 Inter-Integrated Circuit (I2C) Interface

Table 5-37 lists the characteristics for the I2C interface.

Table 5-37 I2C Characteristics

over operating free-air temperature (unless otherwise noted) (see Figure 5-31)| NO. | PARAMETER | MIN | TYP | MAX | UNIT | ||

|---|---|---|---|---|---|---|---|

| I1(1) | tSCH | Start condition hold time | 36 | system clock cycles | |||

| I2 (1) | tLP | Clock low period | 36 | system clock cycles | |||