SLAZ145I October 2012 – May 2021 MSP430F1610

6.5 CPU41

CPU Module

Category

Functional

Function

Incorrect address fetching during interrupt priority decoding

Description

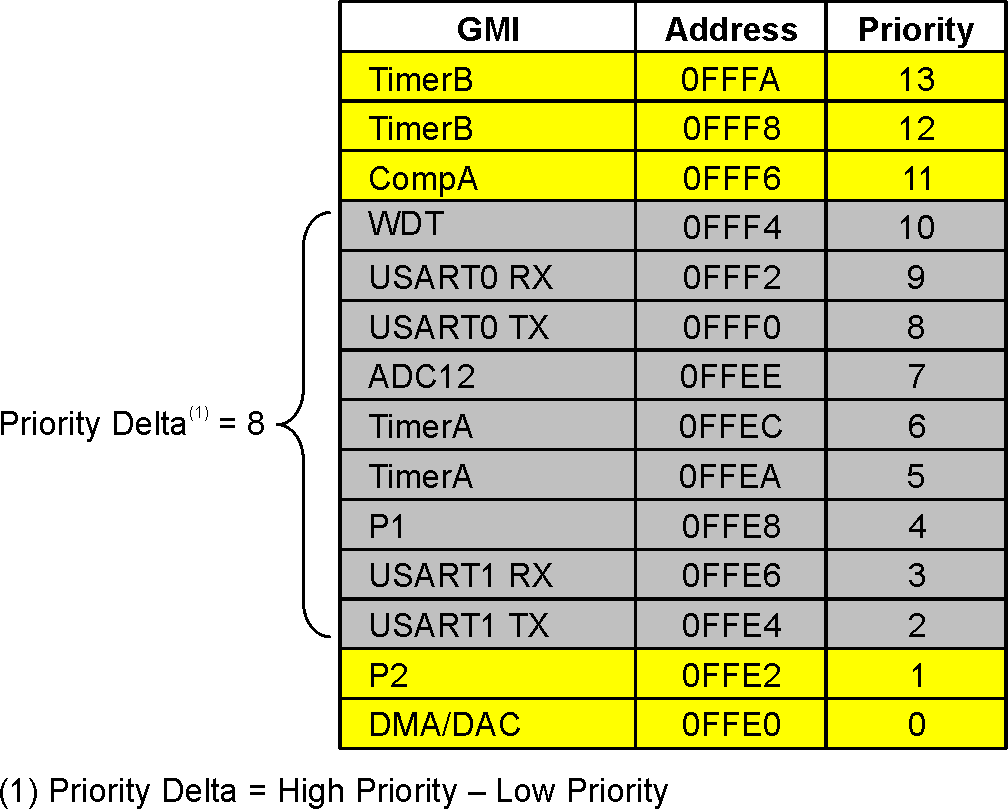

The CPU might fetch a random address if the system clock is greater than 6 MHz and two general maskable interrupts (GMI) with large priority difference are triggered within a time frame of 8 system clock cycles. In fail case, a race condition of the internal interrupt priority chain is corrupting the address bus.

The issue can potentially occur if the priority delta between the two occurring interrupts is greater than 8.

NOTE: This erratum supersedes the DMA9 erratum.

Workaround

1. Reduce the system frequency below 6MHz.

OR

2. Disable affected interrupts and poll the IFGs.