SLLA643 August 2024 MCF8315C , MCF8315C-Q1 , MCF8316C-Q1

5.2 Single Ground with AVDD Shorted to FB_BK

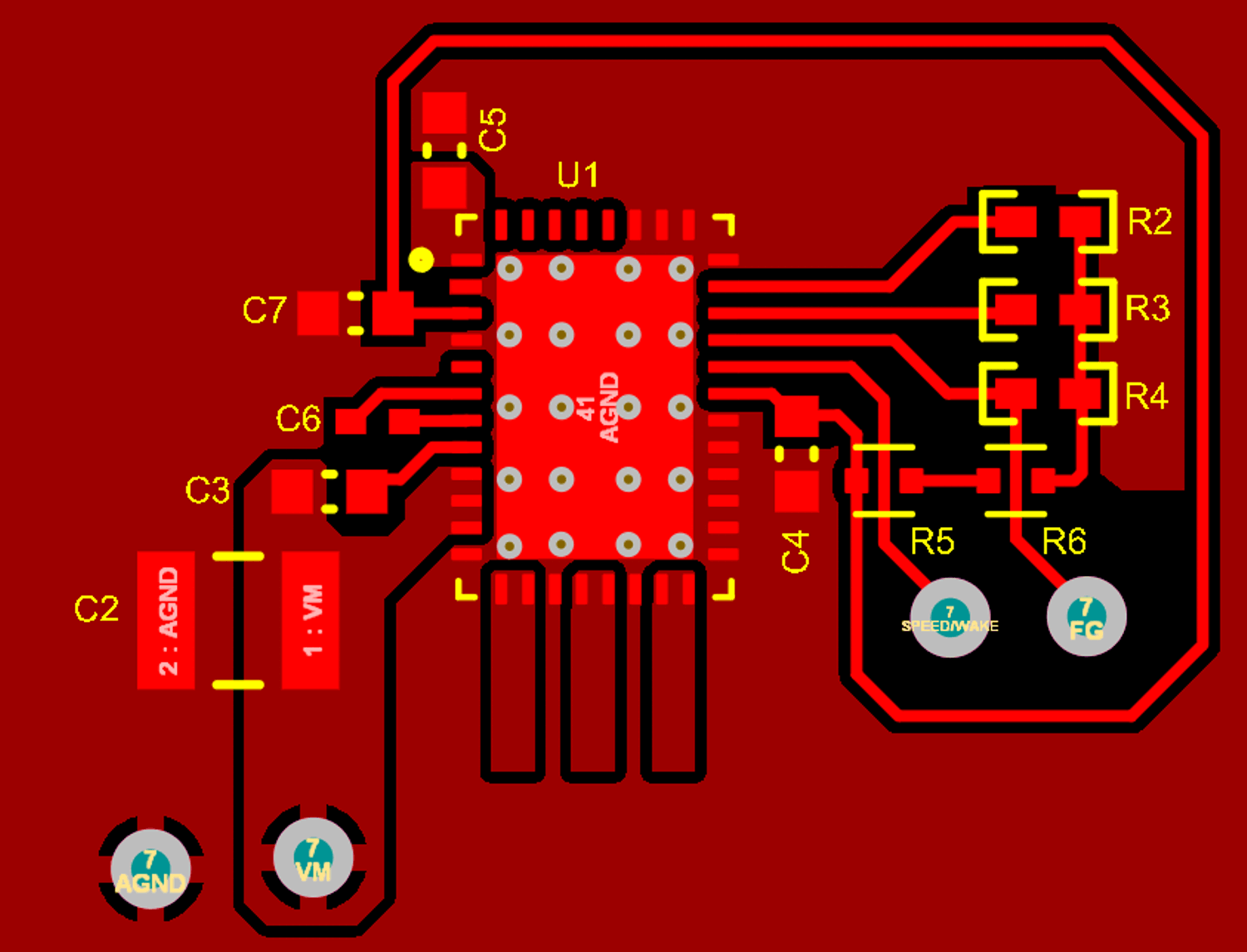

As shown in Section 4.7, for low power/cost applications where the buck regulator is disabled, the recommendation is to connect FB_BK and AVDD externally on the board. Refer to Figure 5-3 and Figure 5-4 for a sample schematic and layout for a single ground plane PCB. One additional capacitor 1uF(C7) is added close to FB_BK due to long trace from AVDD to FB_BK.

Figure 5-3 PCB Schematic for Single

Ground Plane and FB_BK Powered by AVDD

Figure 5-3 PCB Schematic for Single

Ground Plane and FB_BK Powered by AVDD Figure 5-4 PCB Layout for Single Ground

Plane and FB_BK Powered by AVDD

Figure 5-4 PCB Layout for Single Ground

Plane and FB_BK Powered by AVDD