SLLA643 August 2024 MCF8315C , MCF8315C-Q1 , MCF8316C-Q1

5.1 Single Ground Plane

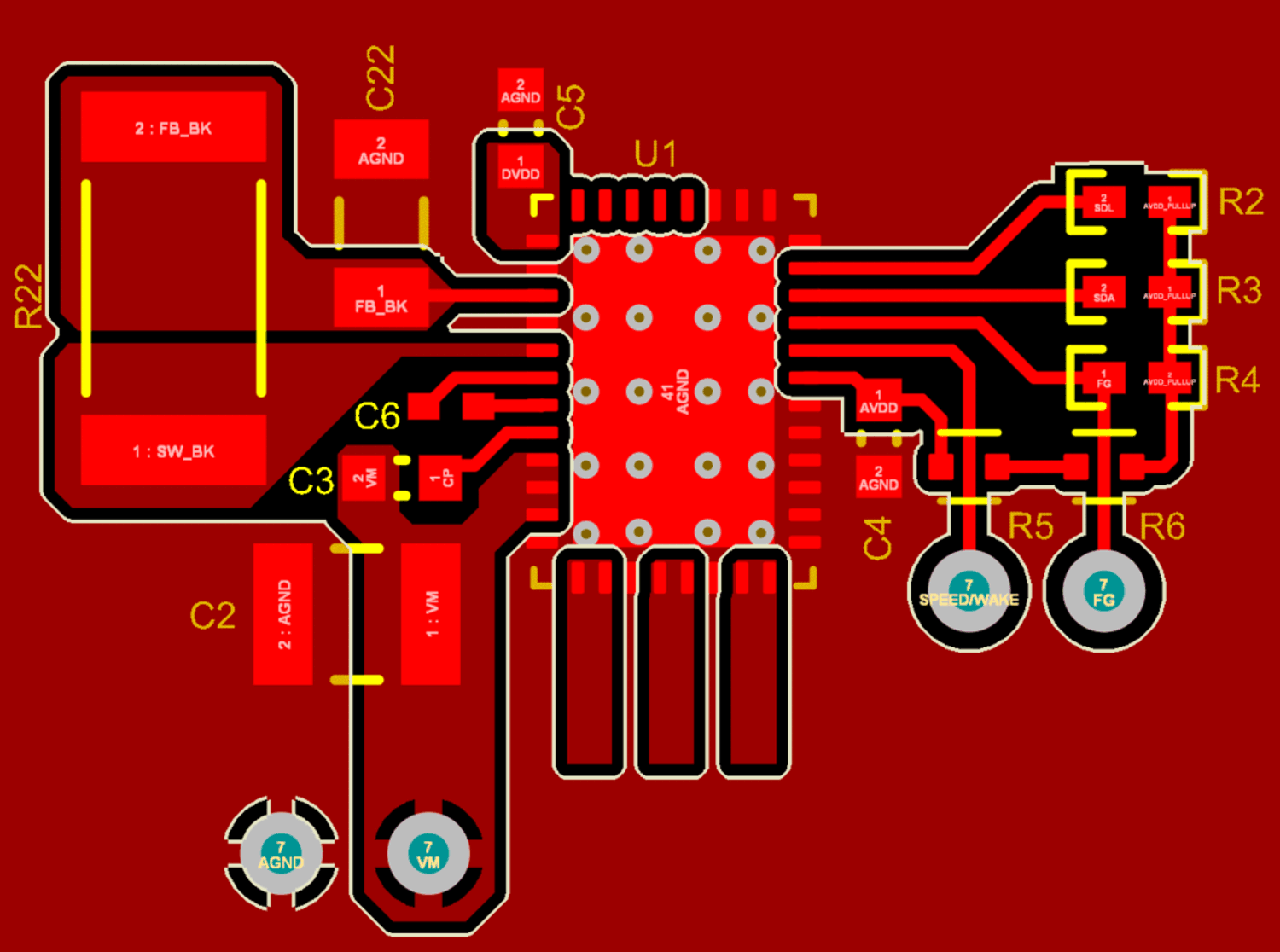

For low cost applications, wherein switching noise coupling between power ground and signal ground is not critical, short all ground pins together. Refer to Figure 5-1 and Figure 5-2 for a sample schematic and layout for a single ground plane PCB.

Figure 5-1 PCB Schematic for Single

Ground Plane

Figure 5-1 PCB Schematic for Single

Ground Plane Figure 5-2 PCB Layout for Single Ground

Plane

Figure 5-2 PCB Layout for Single Ground

Plane