SLLSFS3 May 2024 MCT8316A-Q1

PRODUCTION DATA

- 1

- 1 Features

- 2 Applications

- 3 Description

- 4 Pin Configuration and Functions

- 5 Specifications

-

6 Detailed Description

- 6.1 Overview

- 6.2 Functional Block Diagram

- 6.3

Feature Description

- 6.3.1 Output Stage

- 6.3.2 Device Interface Modes

- 6.3.3 Step-Down Mixed-Mode Buck Regulator

- 6.3.4 AVDD Linear Voltage Regulator

- 6.3.5 Charge Pump

- 6.3.6 Slew Rate Control

- 6.3.7 Cross Conduction (Dead Time)

- 6.3.8 SPEED Control

- 6.3.9 Starting the Motor Under Different Initial Conditions

- 6.3.10 Motor Start Sequence (MSS)

- 6.3.11 Closed Loop Operation

- 6.3.12 Speed Loop

- 6.3.13 Input Power Regulation

- 6.3.14 Anti-Voltage Surge (AVS)

- 6.3.15 Output PWM Switching Frequency

- 6.3.16 Fast Start-up (< 50 ms)

- 6.3.17 Fast Deceleration

- 6.3.18 Active Demagnetization

- 6.3.19 Motor Stop Options

- 6.3.20 FG Configuration

- 6.3.21

Protections

- 6.3.21.1 VM Supply Undervoltage Lockout

- 6.3.21.2 AVDD Undervoltage Lockout (AVDD_UV)

- 6.3.21.3 BUCK Undervoltage Lockout (BUCK_UV)

- 6.3.21.4 VCP Charge Pump Undervoltage Lockout (CPUV)

- 6.3.21.5 Overvoltage Protection (OVP)

- 6.3.21.6 Overcurrent Protection (OCP)

- 6.3.21.7 Buck Overcurrent Protection

- 6.3.21.8

Cycle-by-Cycle (CBC) Current Limit (CBC_ILIMIT)

- 6.3.21.8.1 CBC_ILIMIT Automatic Recovery next PWM Cycle (CBC_ILIMIT_MODE = 000xb)

- 6.3.21.8.2 CBC_ILIMIT Automatic Recovery Threshold Based (CBC_ILIMIT_MODE = 001xb)

- 6.3.21.8.3 CBC_ILIMIT Automatic Recovery after 'n' PWM Cycles (CBC_ILIMIT_MODE = 010xb)

- 6.3.21.8.4 CBC_ILIMIT Report Only (CBC_ILIMIT_MODE = 0110b)

- 6.3.21.8.5 CBC_ILIMIT Disabled (CBC_ILIMIT_MODE = 0111b or 1xxxb)

- 6.3.21.9 Lock Detection Current Limit (LOCK_ILIMIT)

- 6.3.21.10 Thermal Warning (OTW)

- 6.3.21.11 Thermal Shutdown (TSD)

- 6.3.21.12 Motor Lock (MTR_LCK)

- 6.3.21.13 Motor Lock Detection

- 6.3.21.14 IPD Faults

- 6.4 Device Functional Modes

- 6.5 External Interface

- 6.6 EEPROM access and I2C interface

- 6.7 EEPROM (Non-Volatile) Register Map

- 6.8 RAM (Volatile) Register Map

- 7 Application and Implementation

- 8 Device and Documentation Support

- 9 Revision History

- 10Mechanical, Packaging, and Orderable Information

7.2.1.4 Setting the BEMF threshold

The BEMF_THRESHOLD1 and BEMF_THRESHOLD2 values used for commutation instant detection in MCT8316A can be computed from the motor phase voltage waveforms during coasting. For example, consider the three-phase voltage waveforms of a BLDC motor while coasting as in Figure 7-6. The motor phase voltage during coasting is the motor back-EMF.

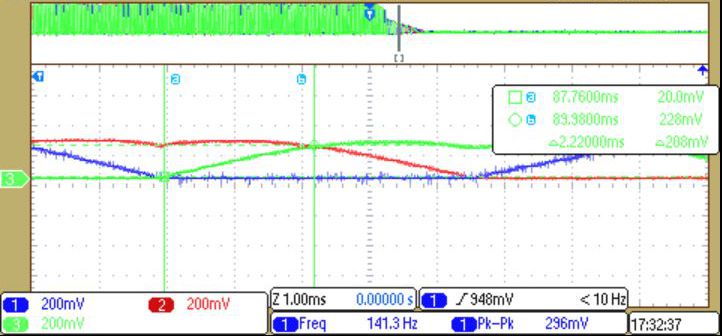

Figure 7-6 Motor phase voltage during coasting

Figure 7-6 Motor phase voltage during coastingIn Figure 7-6, one floating phase voltage interval is denoted by the vertical markers on channel 3. The Vpeak (peak-peak back-EMF) on channel 3 is 208mV and Tc (commutation interval) is 2.22ms as denoted by the horizontal and vertical markers on channel 3. The digital equivalent counts for Vpeak and Tc are calculated as follows.

In MCT8316A, a 3V analog input corresponds to 4095 counts(12-bit) and phase voltage is scaled down by 10x factor before ADC input; therfore, Vpeak of 208mV corresponds to an ADC input of 20.8mV, which in turn equals 29 ADC counts. Assuming the PWM switching frequency is 25kHz, one back-EMF sample is available every 40μs. So, in a time interval of 2.22ms, a total of 55 back-EMF samples are integrated. Therefore, the BEMF_THRESHOLD1 or BEMF_THRESHOLD2 value calculated as per is (½) * (29/2) * (55/2) = 199. Hence, in this example, BEMF_THRESHOLD1 and BEMF_THRESHOLD2 are set to 8h (corresponding to 200 which is the closest value to 199) for commutation instant detection using back-EMF integration method during fast start-up. The exact speed at which the Vpeak and Tc values are measured to calculate the BEMF_THRESHOLD1 and BEMF_THRESHOLD2 values is not critical (as long as there is sufficient resolution in digital counts) since the product (Vpeak * Tc) is, largely, a constant for a given BLDC motor.