SLUSFM3 September 2024 LMR51425-Q1 , LMR51435-Q1

PRODUCTION DATA

- 1

- 1 Features

- 2 Applications

- 3 Description

- 4 Device Comparison Table

- 5 Pin Configuration and Functions

- 6 Specifications

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3

Feature Description

- 7.3.1 Fixed Frequency Peak Current Mode Control

- 7.3.2 Adjustable Output Voltage

- 7.3.3 Enable

- 7.3.4 Switching Frequency

- 7.3.5 Power-Good Flag Output

- 7.3.6 Minimum ON-Time, Minimum OFF-Time, and Frequency Foldback

- 7.3.7 Bootstrap Voltage

- 7.3.8 Overcurrent and Short-Circuit Protection

- 7.3.9 Soft Start

- 7.3.10 Thermal Shutdown

- 7.4 Device Functional Modes

- 8 Application and Implementation

- 9 Device and Documentation Support

- 10Revision History

- 11Mechanical, Packaging, and Orderable Information

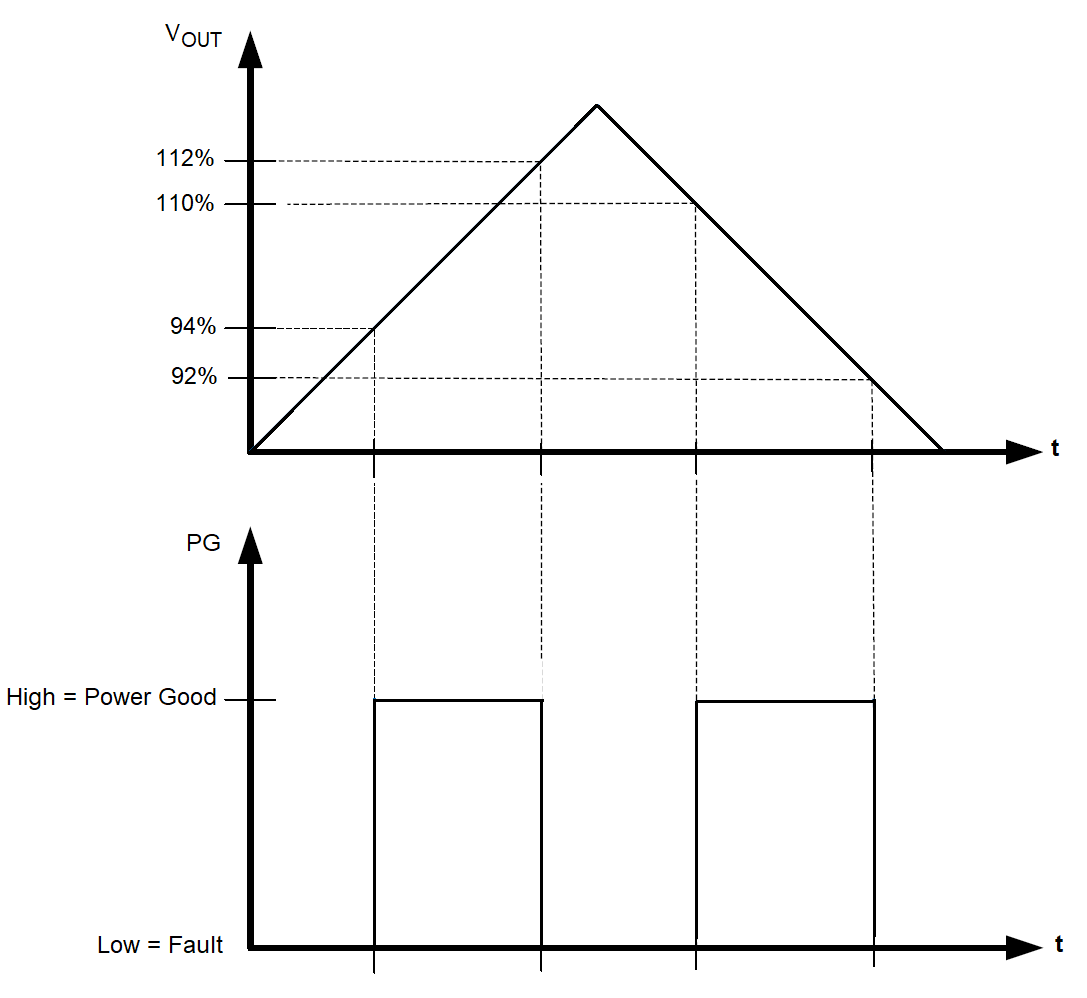

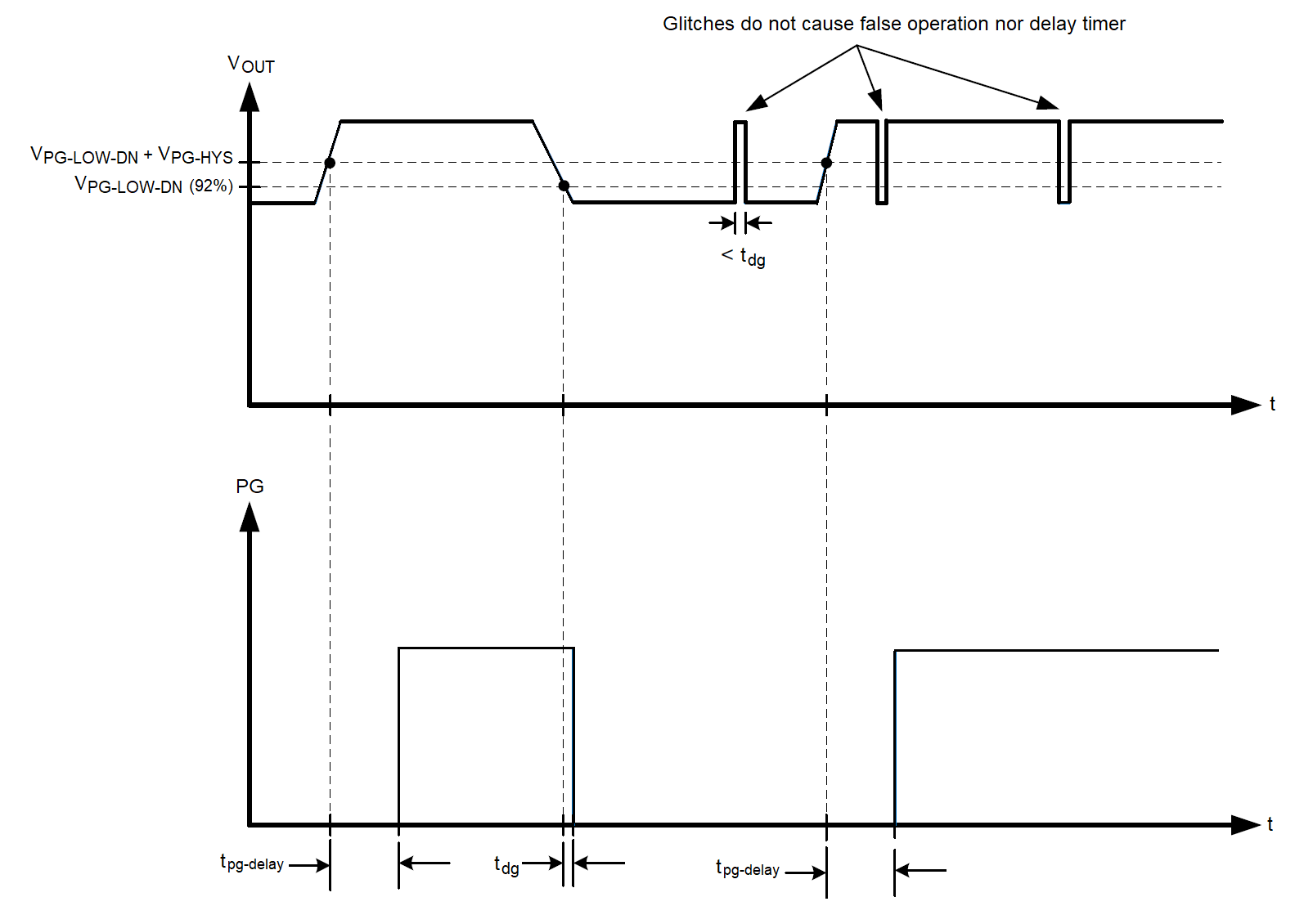

7.3.5 Power-Good Flag Output

The power-good flag function (PG output pin) of the LMR514x5-Q1 can be used to reset a system microprocessor whenever the output voltage is out of regulation. This open-drain output goes low under fault conditions, such as current limit and thermal shutdown, as well as during normal start-up. A glitch filter prevents false flag operation for short excursions of the output voltage, such as during line and load transients. Output voltage excursions lasting less than tdg 35μs (typical) do not trip the power-good flag. After the FB voltage has returned to the regulation value and after a delay of tpg-delay 3.1ms (typical) , the power-good flag goes high.

The power-good output consists of an open-drain NMOS, requiring an external pullup resistor to a suitable logic supply. It can be pulled up to power supply below 20V through a 10kΩ to 100kΩ resistor, as desired. If this function is not needed, the PG pin must be left floating. When EN is pulled low, the flag output is also forced low. With EN low, power good remains valid as long as the input voltage is greater than or equal to 1.5V (typical). Limit the current into the power-good flag pin to less than 5mA D.C.

Figure 7-5 Static Power-Good Operation

Figure 7-5 Static Power-Good Operation Figure 7-6 Power-Good Timing Behavior

Figure 7-6 Power-Good Timing Behavior