SLUUCD1A April 2020 – April 2022 TPS62860

3.1 Layout

Figure 3-1 through Figure 3-5 show the component placement and PCB layout of the TPS6286x1EVM.

Figure 3-1 TPS6286x1EVM PCB - Assembly Layer

Figure 3-2 TPS6286x1EVM PCB - Top Layer

Figure 3-3 TPS6286x1EVM PCB - Signal Layer 1 (Top View)

Figure 3-4 TPS6286x1EVM PCB - Signal Layer 2 (Top View)

Figure 3-5 TPS6286x1EVM PCB - Bottom Layer (Top View)

Figure 3-6 TPS628601EVM Angled View

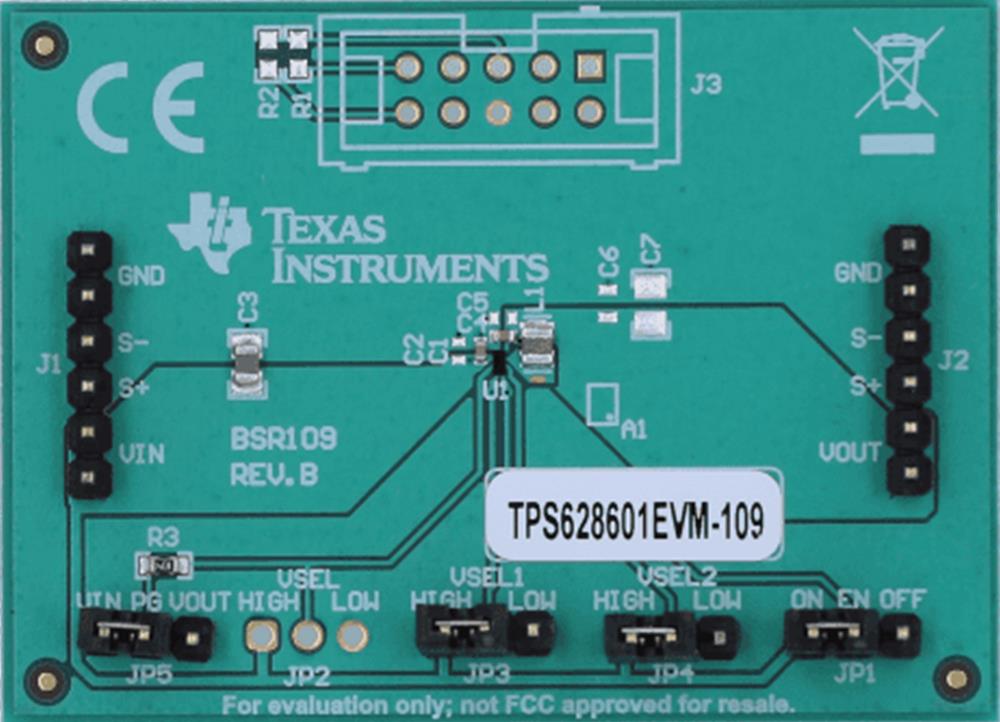

Figure 3-6 TPS628601EVM Angled View Figure 3-7 TPS628601EVM Overhead View

Figure 3-7 TPS628601EVM Overhead View