SLUUCV8 October 2023 TPS4810-Q1

4.2 PCB Layout

Figure 5-2 shows component placement of the EVAL Board, and Figure 5-4 and Figure 5-6 show PCB layout images.

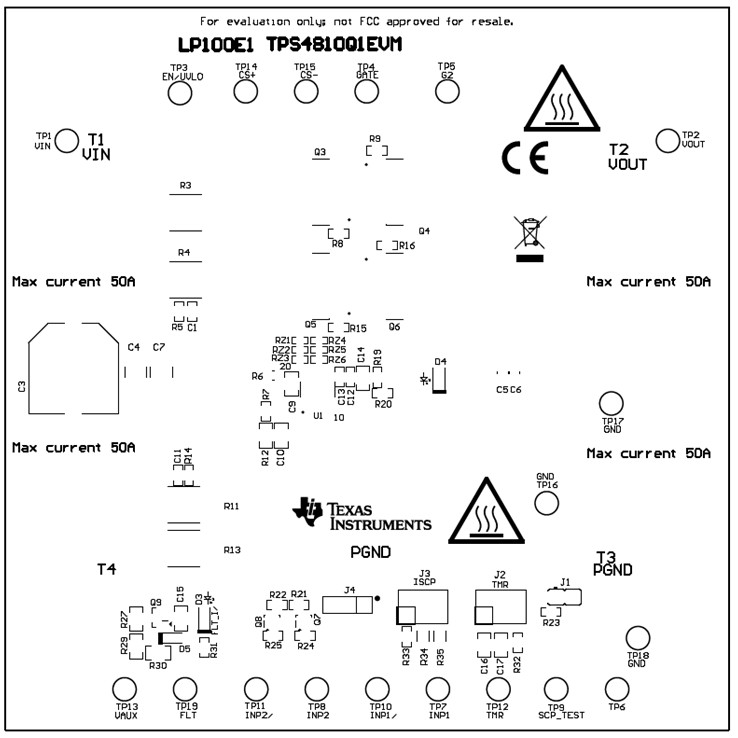

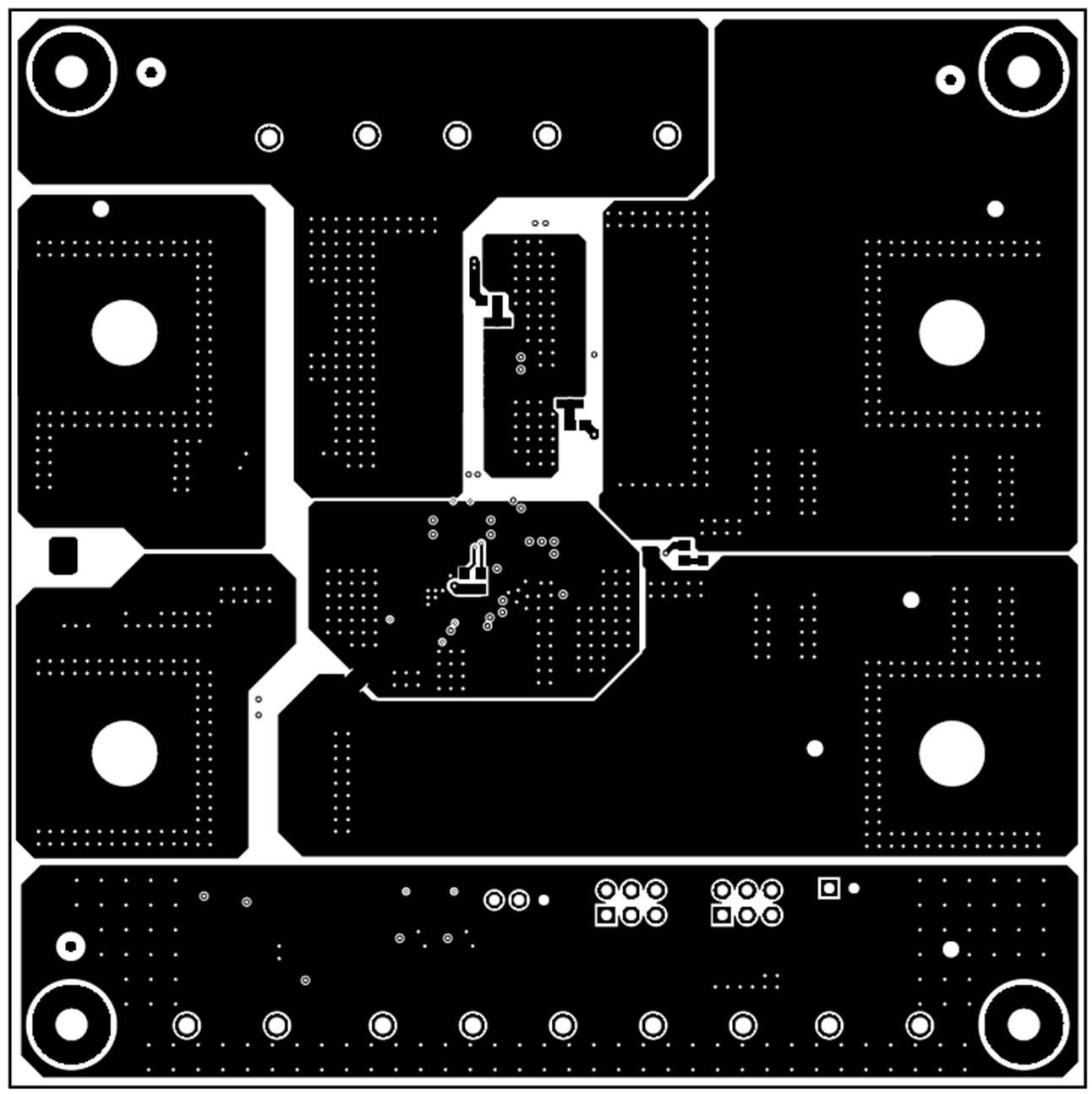

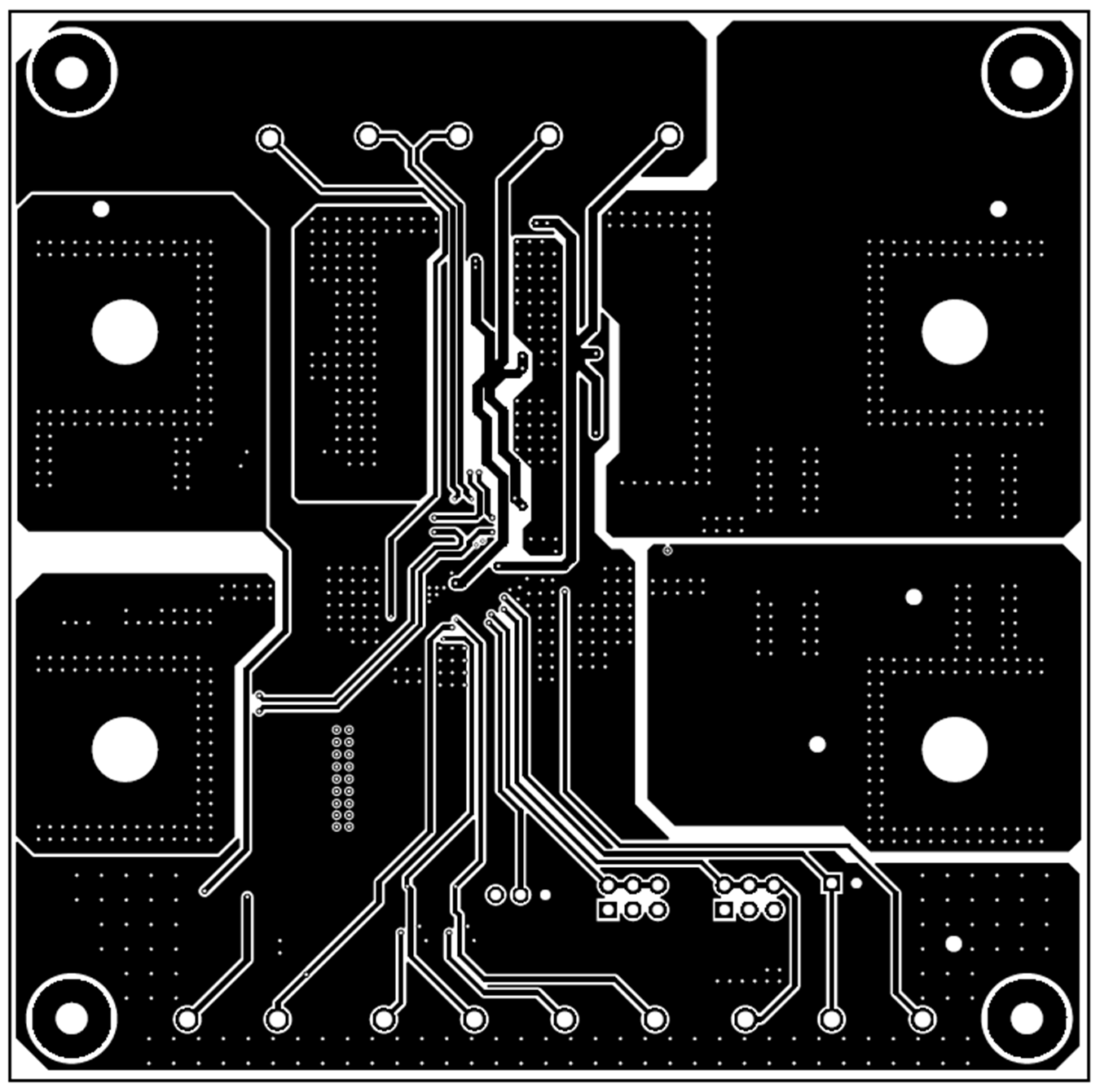

Figure 4-2 TPS4810Q1EVM Board Top

Overlay

Figure 4-2 TPS4810Q1EVM Board Top

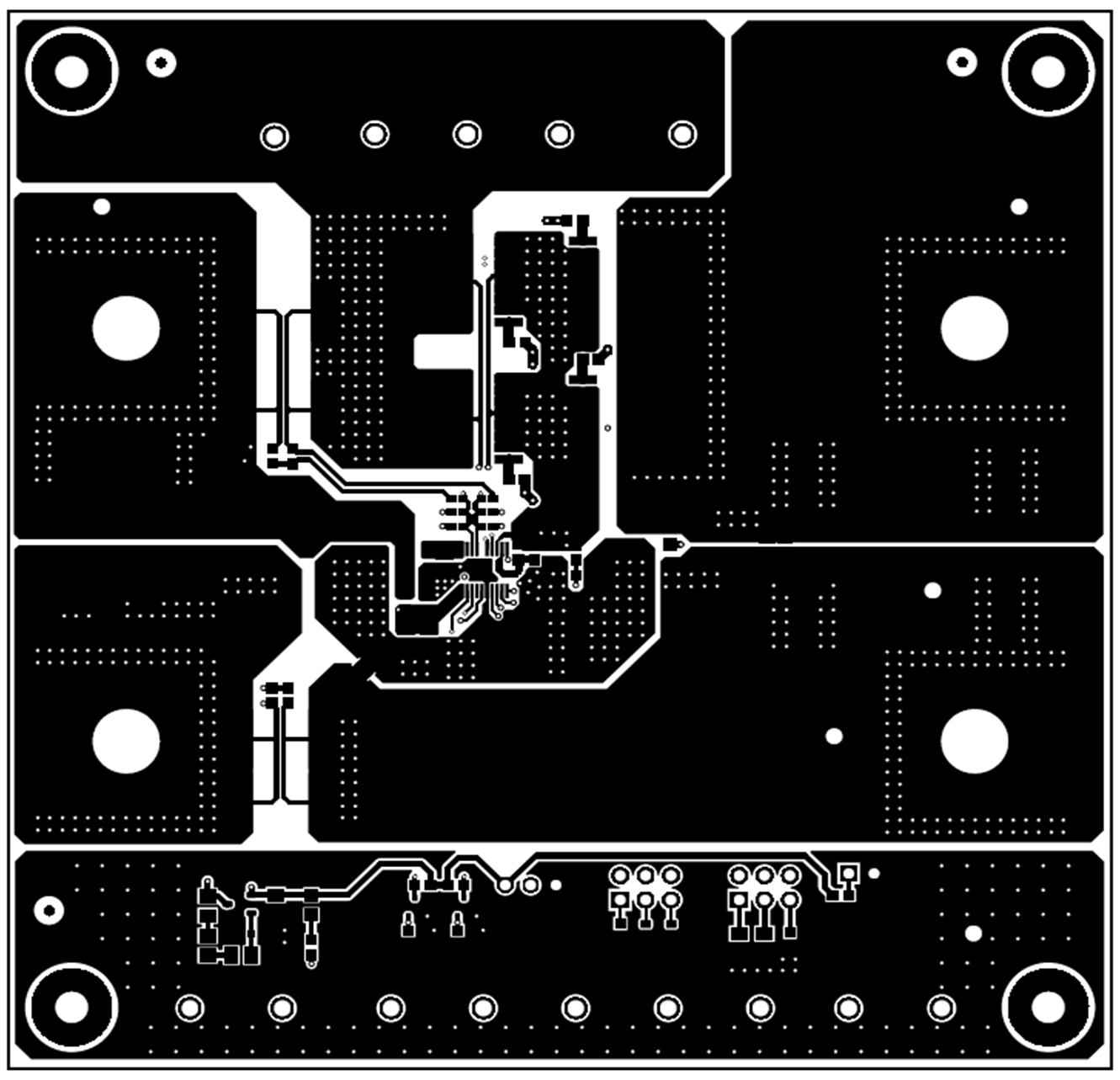

Overlay Figure 4-4 TPS4810Q1EVM Board Top

Layer

Figure 4-4 TPS4810Q1EVM Board Top

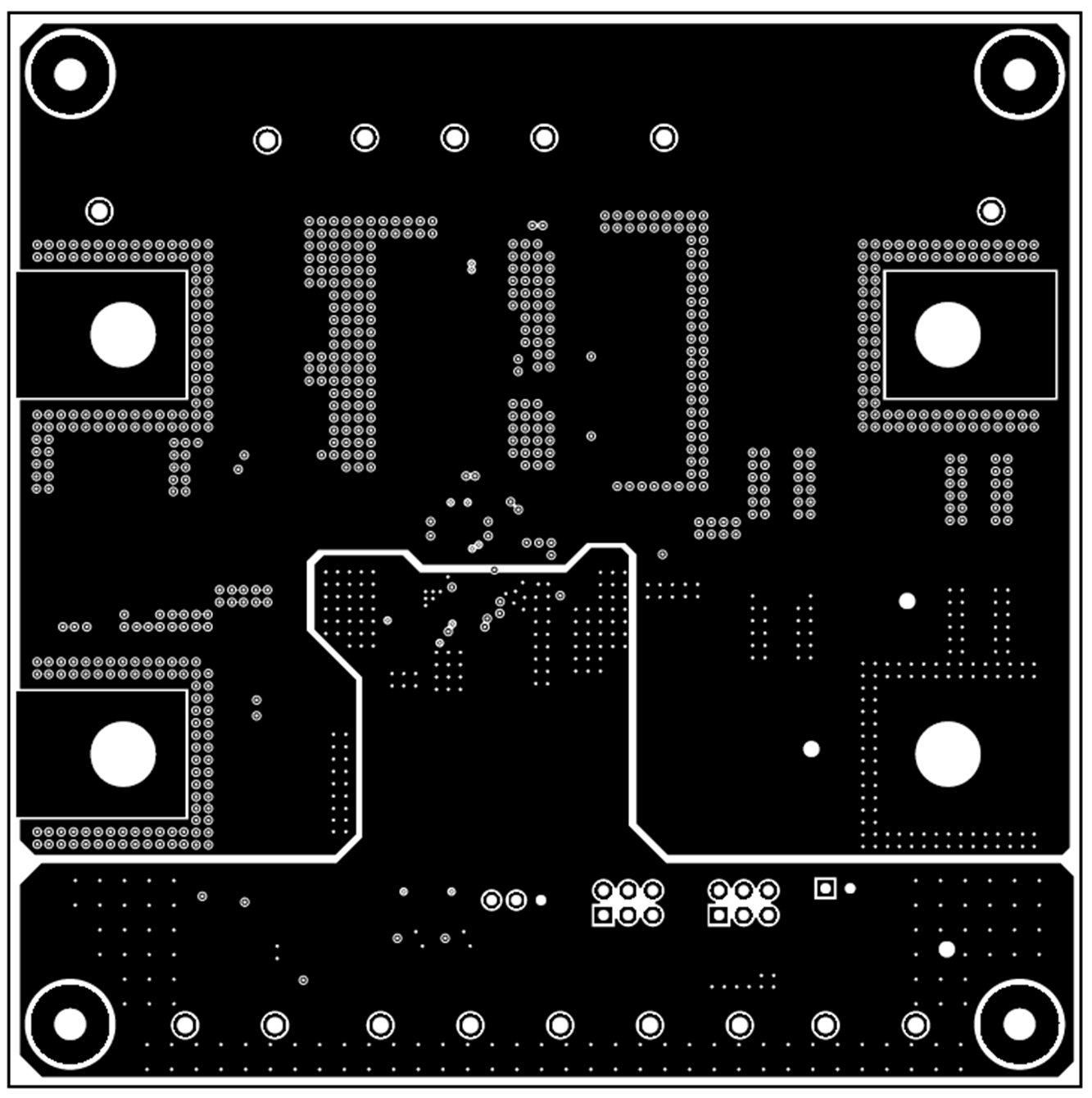

Layer  Figure 4-6 TPS4810Q1EVM Board Inner

Signal Layer

Figure 4-6 TPS4810Q1EVM Board Inner

Signal Layer  Figure 4-3 TPS4810Q1EVM Board Bottom

Overlay

Figure 4-3 TPS4810Q1EVM Board Bottom

Overlay Figure 4-5 TPS4810Q1EVM Board Bottom

Layer

Figure 4-5 TPS4810Q1EVM Board Bottom

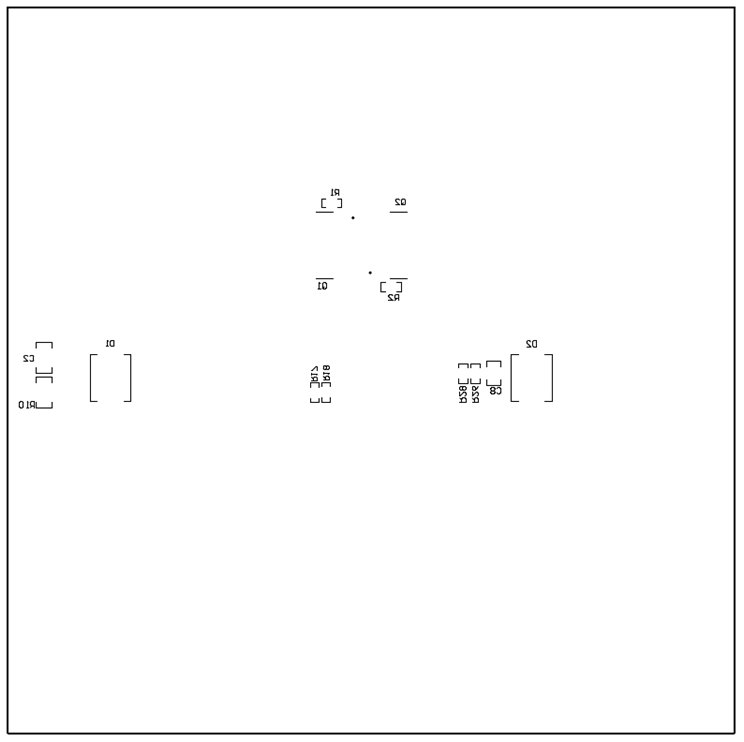

Layer Figure 4-7 TPS4810Q1EVM Board Inner

Routing Layer

Figure 4-7 TPS4810Q1EVM Board Inner

Routing Layer