-

Mitigating Procedure on Voltage Spike of Switching Node from Flyback Converter

Mitigating Procedure on Voltage Spike of Switching Node from Flyback Converter

Trademarks

All other trademarks are the property of their respective owners.

1 Switching Node Voltage Stress from Flyback

1.1 Reflected Voltage, VOR

In a typical flyback converter, there is voltage which is reflected from secondary side when the primary side switch is turned off and the stored energy is transferring to the load through transformer. This reflected voltage, VOR will form voltage stress to the switching device after adding maximum input VDC, VIN in worst case. So the amplitude of the reflected voltage, VOR will be a key design factor, affecting voltage stress to the switching device.

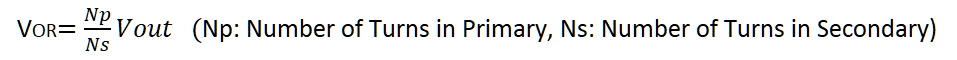

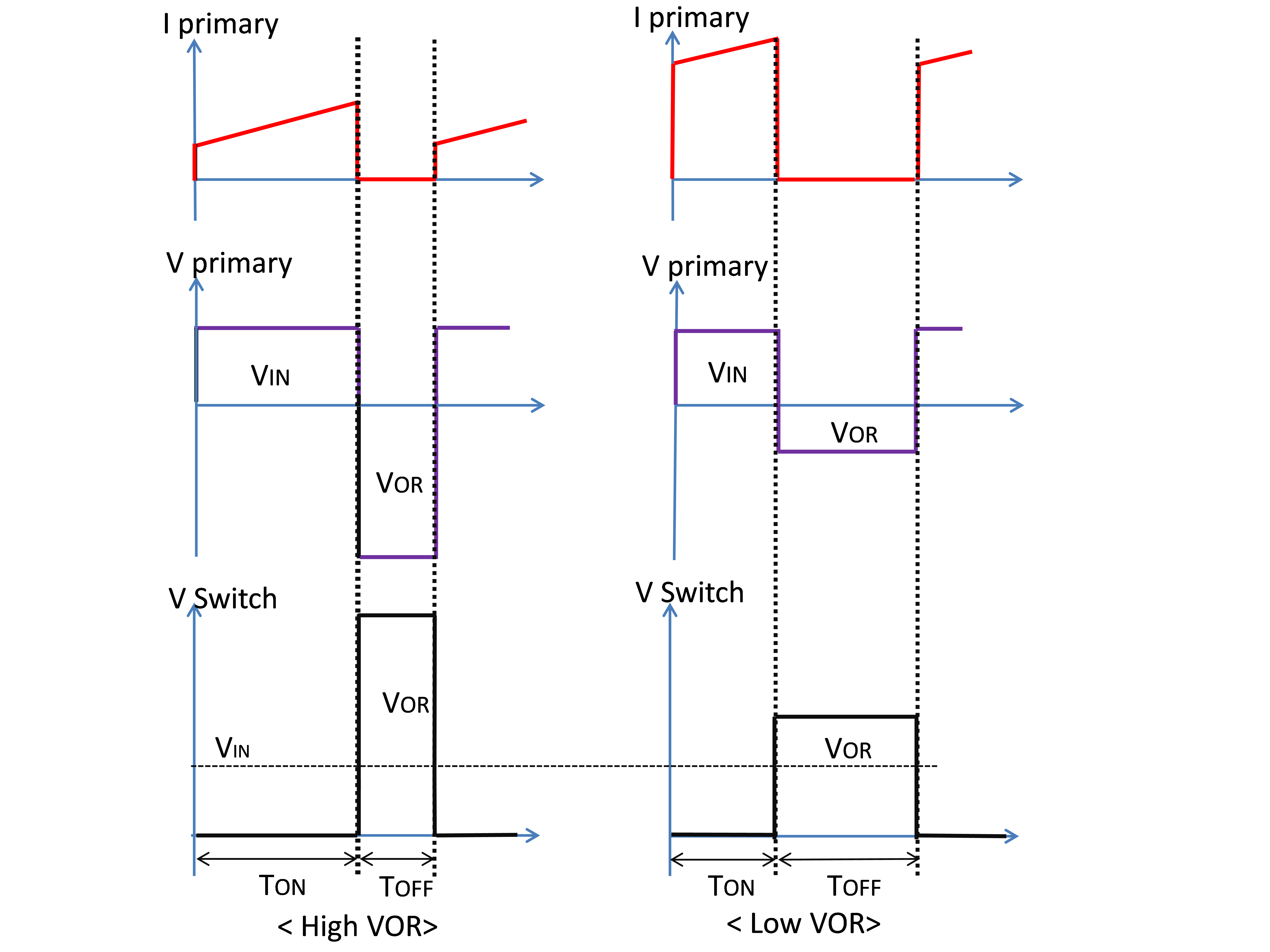

From the simple equation above, VOR is set by primary to secondary turn ratio once output voltage is set. And then Flyback controller or convert will set its’ duty ratio by inductor’s volt-sec balance if VOR is fixed. Figure 1-1 shows the comparison voltage and current stress according to VOR level.

Figure 1-1 Flyback Converter's Primary

Side Current, Voltage, and Switch Note Voltage

Figure 1-1 Flyback Converter's Primary

Side Current, Voltage, and Switch Note VoltageBy adjusting turn ratio, VOR could be contained if it tops a limited level that is required by system. But a lower VOR will cause a higher peak current stress and make system have lower efficiency due to an increased conduction loss. Also, it is possible for higher peak to trigger internal current limit of the device which integrates FET inside.

1.2 Leakage Inductance Factor

In addition to voltage stress (VIN + VOR), there is a large voltage spike at turned off moment that is caused by the stored energy in leakage inductance of primary winding. Basically, it is a fact that magnetic flux from one winding that does not couple to other winding 100%, so it remains as a leakage inductance in the circuit. One of methods to reduce leakage factor is to improve transformer winding structure such as interleaving winding. Figure 1-2 is the simulated result after adding a small amount of leakage inductance in primary side equivalently.

Figure 1-2 Switch Note Waveform with

Leakage Inductance

Figure 1-2 Switch Note Waveform with

Leakage InductanceAs the simulated result, the stored energy in the leakage inductance turns to voltage spike immediately at turn off transient moment and then mainly resonates with the capacitance on the node. Usually it resonates under a few hundreds of MHz so it may cause EMI problems in the systems and need additional snubbing measures. Plus, if the voltage peak is higher than device’s AMR (Absolute Maximum Rating), it will lead to IC or FET’s damage issue either in the design stage or field.