SLVAF47 March 2021 TPS7H4001-SP

3 AC Regulation

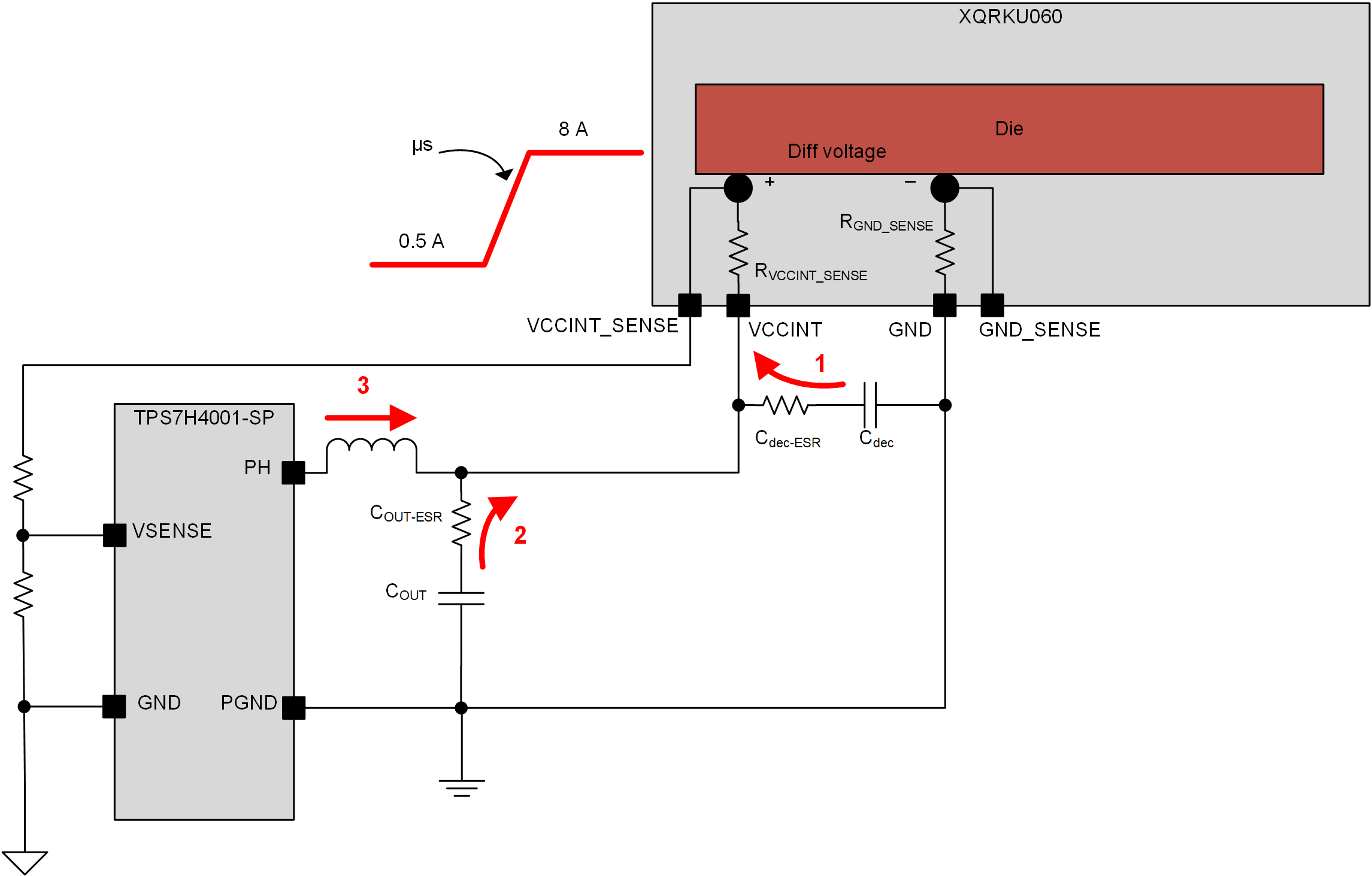

AC regulation is associated with load transients in the VCCINT rail. These load transients depend heavily on the programming code used in the FPGA. Consequently, we recommending writing the code in a way that avoids severe transients as much as possible – in other words, avoid enabling a large amount of logic in the FPGA at once. Load transients are always present, however, you need to properly address them to meet the regulation requirements.

Given the nature of some of these transients (some with high slew rates in the ampere-per-nanosecond range), the converter might not respond to the voltage drop caused by the transient quickly enough. This is where the decoupling capacitors recommended by Xilinx become critical (see the XQRKU060 data sheet for detailed information regarding decoupling capacitors for different transient scenarios). These decoupling capacitors are in addition to any internal decoupling capacitors typically included in FPGA packages. Figure 3-1 shows an example of an approximately 7-A load transient in the microseconds range.

Figure 3-1 AC Regulation Response Due to

Load Transients

Figure 3-1 AC Regulation Response Due to

Load TransientsInitially, the internal and external decoupling capacitors will respond to the current increase. The external decoupling capacitors are sized to match the worst-case expected transient based on the XQRKU060 data sheet recommendation and, as a result, they will handle the transient properly. In case the FPGA still requires additional current after the depletion of the decoupling capacitors, the output capacitors of the converter will supply current until the converter is able to respond. You must choose the crossover frequency of the converter and the respective feedback compensation accordingly for every application.