-

DRV8832 Low-Voltage Motor Driver IC

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

- IMPORTANT NOTICE

DRV8832 Low-Voltage Motor Driver IC

1 Features

- H-Bridge Voltage-Controlled Motor Driver

- Drives DC Motor, One Winding of a Stepper Motor, or Other Actuators/Loads

- Efficient PWM Voltage Control for Constant Motor Speed With Varying Supply Voltages

- Low MOSFET On-Resistance:

HS + LS 450 mΩ

- 1-A Maximum DC/RMS or Peak Drive Current

- 2.75-V to 6.8-V Operating Supply Voltage Range

- 300-nA (Typical) Sleep Mode Current

- Reference Voltage Output

- Current Limit Circuit

- Fault Output

- Thermally-Enhanced Surface Mount Packages

2 Applications

- Battery-Powered:

- Printers

- Toys

- Robotics

- Cameras

- Phones

- Small Actuators, Pumps, and so forth

3 Description

The DRV8832 provides an integrated motor driver solution for battery-powered toys, printers, and other low-voltage or battery-powered motion control applications. The device has one H-bridge driver, and can drive one DC motor or one winding of a stepper motor, as well as other loads like solenoids. The output driver block consists of N-channel and P-channel power MOSFETs configured as an H-bridge to drive the motor winding.

Provided with sufficient PCB heatsinking, the DRV8832 can supply up to 1 A of DC/RMS or peak output current. The device operates on power supply voltages from 2.75 V to 6.8 V.

To maintain constant motor speed over varying battery voltages while maintaining long battery life, a PWM voltage regulation method is provided. An input pin allows programming of the regulated voltage. A built-in voltage reference output is also provided.

Internal protection functions are provided for overcurrent protection, short-circuit protection, undervoltage lockout, and overtemperature protection.

The DRV8832 also provides a current limit function to regulate the motor current during conditions like motor start-up or stall, as well as a fault output pin to signal a host processor of a fault condition.

The DRV8832 is available in a tiny 3-mm × 3-mm 10-pin VSON package and MSOP PowerPAD™ package (Eco-friendly: RoHS & no Sb/Br).

Device Information(1)

| PART NUMBER | PACKAGE | BODY SIZE (NOM) |

|---|---|---|

| DRV8832 | MSOP PowerPAD (10) | 3.00 mm × 3.00 mm |

| VSON (10) | 3.00 mm × 3.00 mm |

- For all available packages, see the orderable addendum at the end of the data sheet.

Simplified Schematic

4 Revision History

Changes from H Revision (October 2013) to I Revision

- Added ESD Ratings table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section Go

- Added VHYS parameter row under the Logic-Level Inputs section in Electrical Characteristics Go

- Changed the paragraph describing the FAULT behavior in Current LimitGo

- Updated the paragraphs in Power Dissipation and added Equation 4Go

5 Pin Configuration and Functions

Pin Functions

| PIN | I/O | DESCRIPTION | ||

|---|---|---|---|---|

| NAME | NO. | |||

| FAULTn | 6 | OD | Fault output | Open-drain output driven low if fault condition present |

| GND | 5 | — | Device ground | |

| IN1 | 9 | I | Bridge A input 1 | Logic high sets OUT1 high |

| IN2 | 10 | I | Bridge A input 2 | Logic high sets OUT2 high |

| ISENSE | 2 | IO | Current sense resistor | Connect current sense resistor to GND. Resistor value sets current limit level. |

| OUT1 | 3 | O | Bridge output 1 | Connect to motor winding |

| OUT2 | 1 | O | Bridge output 2 | Connect to motor winding |

| VCC | 4 | — | Device and motor supply | Bypass to GND with a 0.1-μF (minimum) ceramic capacitor. |

| VREF | 8 | O | Reference voltage output | Reference voltage output |

| VSET | 7 | I | Voltage set input | Input voltage sets output regulation voltage |

6 Specifications

6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)(2)| MIN | MAX | UNIT | ||

|---|---|---|---|---|

| Power supply voltage, VCC | –0.3 | 7 | V | |

| Input pin voltage | –0.5 | 7 | V | |

| Peak motor drive output current(3) | Internally limited | A | ||

| Continuous motor drive output current(3) | –1 | 1 | A | |

| Continuous total power dissipation | See Thermal Information | |||

| TJ | Operating virtual junction temperature | –40 | 150 | °C |

| Tstg | Storage temperature | –60 | 150 | °C |

6.2 ESD Ratings

| VALUE | UNIT | |||

|---|---|---|---|---|

| V(ESD) | Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins(1) | ±2500 | V |

| Charged device model (CDM), per JEDEC specification JESD22-C101, all pins(2) | ±1000 | |||

6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)| MIN | NOM | MAX | UNIT | ||

|---|---|---|---|---|---|

| VCC | Motor power supply voltage | 2.75 | 6.8 | V | |

| IOUT | Continuous or peak H-bridge output current(1) | 0 | 1 | A | |

6.4 Thermal Information

| THERMAL METRIC(1) | DRV8832 | UNIT | ||

|---|---|---|---|---|

| DGQ (MSOP PowerPAD) | DRC (VSON) | |||

| 10 PINS | 10 PINS | |||

| RθJA | Junction-to-ambient thermal resistance | 69.3 | 50.2 | °C/W |

| RθJC(top) | Junction-to-case (top) thermal resistance | 63.5 | 78.4 | °C/W |

| RθJB | Junction-to-board thermal resistance | 51.6 | 18.8 | °C/W |

| ψJT | Junction-to-top characterization parameter | 1.5 | 1.1 | °C/W |

| ψJB | Junction-to-board characterization parameter | 23.2 | 17.9 | °C/W |

| RθJC(bot) | Junction-to-case (bottom) thermal resistance | 9.5 | 5.1 | °C/W |

6.5 Electrical Characteristics

VCC = 2.75 V to 6.8 V, TA = –40°C to 85°C (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| POWER SUPPLIES | ||||||

| IVCC | VCC operating supply current | VCC = 5 V | 1.4 | 2 | mA | |

| IVCCQ | VCC sleep mode supply current | VCC = 5 V, TA = 25°C | 0.3 | 1 | μA | |

| VUVLO | VCC undervoltage lockout voltage | VCC rising | 2.575 | 2.75 | V | |

| VCC falling | 2.47 | |||||

| LOGIC-LEVEL INPUTS | ||||||

| VIL | Input low voltage | 0.25 × VCC | V | |||

| VHYS | Input hysteresis | 0.08 × Vcc | V | |||

| VIH | Input high voltage | 0.5 × VCC | V | |||

| IIL | Input low current | VIN = 0 | –10 | 10 | μA | |

| IIH | Input high current | VIN = 3.3 V | 50 | μA | ||

| LOGIC-LEVEL OUTPUTS (FAULTn) | ||||||

| VOL | Output low voltage | VCC = 5 V, IOL = 4 mA(1) | 0.5 | V | ||

| H-BRIDGE FETS | ||||||

| RDS(ON) | HS FET on resistance | VCC = 5 V, I O = 0.8 A, TJ = 85°C | 290 | 400 | mΩ | |

| VCC = 5 V, I O = 0.8 A, TJ = 25°C | 250 | |||||

| RDS(ON) | LS FET on resistance | VCC = 5 V, I O = 0.8 A, TJ = 85°C | 230 | 320 | mΩ | |

| VCC = 5 V, I O = 0.8 A, TJ = 25°C | 200 | |||||

| IOFF | Off-state leakage current | –20 | 20 | μA | ||

| MOTOR DRIVER | ||||||

| tR | Rise time | VCC = 3 V, load = 4 Ω | 50 | 300 | ns | |

| tF | Fall time | VCC = 3 V, load = 4 Ω | 50 | 300 | ns | |

| fSW | Internal PWM frequency | 44.5 | kHz | |||

| PROTECTION CIRCUITS | ||||||

| IOCP | Overcurrent protection trip level | 1.3 | 3 | A | ||

| tOCP | OCP deglitch time | 2 | μs | |||

| TTSD | Thermal shutdown temperature | Die temperature(1) | 150 | 160 | 180 | °C |

| VOLTAGE CONTROL | ||||||

| VREF | Reference output voltage | 1.235 | 1.285 | 1.335 | V | |

| ΔVLINE | Line regulation | VCC = 3.3 V to 6 V, VOUT = 3 V(1)

IOUT = 500 mA |

±1% | |||

| ΔVLOAD | Load regulation | VCC = 5 V, VOUT = 3 V IOUT = 200 mA to 800 mA(1) |

±1% | |||

| CURRENT LIMIT | ||||||

| VILIM | Current limit sense voltage | 160 | 200 | 240 | mV | |

| tILIM | Current limit fault deglitch time | 275 | ms | |||

| RISEN | Current limit set resistance (external resistor value) | 0 | 1 | Ω | ||

6.6 Typical Characteristics

(VIN = 5 V, VOUT = 3 V)

Figure 3. IVCC vs VVCC

Figure 3. IVCC vs VVCC

Figure 5. RDS(ON) vs VVCC

Figure 5. RDS(ON) vs VVCC

Figure 2. Efficiency vs Output Voltage

Figure 2. Efficiency vs Output Voltage(VIN = 5 V, IOUT = 500 mA)

Figure 4. IVCCQ vs VVCC

Figure 4. IVCCQ vs VVCC

Figure 6. RDS(ON) HS + LS vs Temperature

Figure 6. RDS(ON) HS + LS vs Temperature

7 Detailed Description

7.1 Overview

The DRV8832 is an integrated motor driver solution used for brushed motor control. The device integrates one H-bridge, current regulation circuitry, and a PWM voltage regulation method.

Using the PWM voltage regulation allows the motor to maintain the desired speed as VCC changes. Battery operation is an example of using this feature. When the battery is new or fully charged VCC will be higher than when the battery is old or partially discharged. The speed of the motor will vary based on the voltage of the battery. By setting the desired voltage across the motor at a lower voltage, a fully charged battery will use less power and spin the motor at the same speed as a battery that has been partially discharged.

7.2 Functional Block Diagram

7.3 Feature Description

7.3.1 PWM Motor Driver

The DRV8832 contains an H-bridge motor driver with PWM voltage-control circuitry with current limit circuitry. Figure 7 shows a block diagram of the motor control circuitry.

Figure 7. Motor Control Circuitry

Figure 7. Motor Control Circuitry

7.3.2 Bridge Control

The IN1 and IN2 control pins enable the H-bridge outputs. Table 1 shows the logic:

Table 1. H-Bridge Logic

| IN1 | IN2 | OUT1 | OUT2 | Function |

|---|---|---|---|---|

| 0 | 0 | Z | Z | Sleep/Coast |

| 0 | 1 | L | H | Reverse |

| 1 | 0 | H | L | Forward |

| 1 | 1 | H | H | Brake |

When both inputs are low, the output drivers are disabled and the device is placed into a low-power sleep state. The current limit fault condition (if present) is also cleared. Note that when transitioning from either brake or sleep mode to forward or reverse, the voltage control PWM starts at zero duty cycle. The duty cycle slowly ramps up to the commanded voltage. This can take up to 12 ms to go from sleep to 100% duty cycle. Because of this, high-speed PWM signals cannot be applied to the IN1 and IN2 pins. To control motor speed, use the VSET pin as described below.

Because of the sleep mode functionality described previously, when applying an external PWM to the DRV8832, hold one input logic high while applying a PWM signal to the other. If the logic input is held low instead, then the device will cycle in and out of sleep mode, causing the FAULTn pin to pulse low on every sleep mode exit.

7.3.3 Voltage Regulation

The DRV8832 provides the ability to regulate the voltage applied to the motor winding. This feature allows constant motor speed to be maintained even when operating from a varying supply voltage such as a discharging battery.

The DRV8832 uses a pulse-width modulation (PWM) technique instead of a linear circuit to minimize current consumption and maximize battery life.

The circuit monitors the voltage difference between the output pins and integrates it, to get an average DC voltage value. This voltage is divided by 4 and compared to the VSET pin voltage. If the averaged output voltage (divided by 4) is lower than VSET, the duty cycle of the PWM output is increased; if the averaged output voltage (divided by 4) is higher than VSET, the duty cycle is decreased.

During PWM regulation, the H-bridge is enabled to drive current through the motor winding during the PWM on time. This is shown in the diagram below as case 1. The current flow direction shown indicates the state when IN1 is high and IN2 is low.

Note that if the programmed output voltage is greater than the supply voltage, the device will operate at 100% duty cycle and the voltage regulation feature will be disabled. In this mode the device behaves as a conventional H-bridge driver.

During the PWM off time, winding current is recirculated by enabling both of the high-side FETs in the bridge as shown in Figure 8.

Figure 8. Voltage Regulation

Figure 8. Voltage Regulation

7.3.4 Reference Output

The DRV8832 includes a reference voltage output that can be used to set the motor voltage. Typically for a constant-speed application, VSET is driven from VREF through a resistor divider to provide a voltage equal to 1/4 the desired motor drive voltage.

For example, if VREF is connected directly to VSET, the voltage will be regulated at 5.14 V. If the desired motor voltage is 3 V, VREF should be 0.75 V. This can be obtained with a voltage divider using 53 kΩ from VREF to VSET, and 75 kΩ from VSET to GND.

7.3.5 Current Limit

A current limit circuit is provided to protect the system in the event of an overcurrent condition, such as what would be encountered if driving a DC motor at start-up or with an abnormal mechanical load (stall condition).

The motor current is sensed by monitoring the voltage across an external sense resistor. When the voltage exceeds a reference voltage of 200 mV for more than approximately 3 µs, the PWM duty cycle is reduced to limit the current through the motor to this value. This current limit allows for starting the motor while controlling the current.

If the current limit condition persists for some time, it is likely that a fault condition has been encountered, such as the motor being run into a stop or a stalled condition. An overcurrent event must persist for approximately

275 ms before the fault is registered. After approximately 275 ms, a fault signaled to the host by driving the FAULTn signal low. Operation of the motor driver will continue.

The current limit fault condition is self-clearing and will be released when the abnormal load (stall condition) is removed.

The resistor used to set the current limit must be less than 1 Ω. Its value may be calculated using Equation 1:

where

- RISENSE is the current sense resistor value

- ILIMIT is the desired current limit (in mA)

If the current limit feature is not needed, the ISENSE pin may be directly connected to ground.

7.3.6 Protection Circuits

The DRV8832 is fully protected against undervoltage, overcurrent and overtemperature events.

7.3.6.1 Overcurrent Protection (OCP)

An analog current limit circuit on each FET limits the current through the FET by removing the gate drive. If this analog current limit persists for longer than the OCP time, all FETs in the H-bridge will be disabled, and the FAULTn signal will be driven low. The device will remain disabled until VCC is removed and re-applied.

Overcurrent conditions are sensed independently on both high and low side devices. A short to ground, supply, or across the motor winding will all result in an overcurrent shutdown. Note that OCP is independent of the current limit function, which is typically set to engage at a lower current level; the OCP function is intended to prevent damage to the device under abnormal (for example, short-circuit) conditions.

7.3.6.2 Thermal Shutdown (TSD)

If the die temperature exceeds safe limits, all FETs in the H-bridge will be disabled and the FAULTn signal will be driven low. Once the die temperature has fallen to a safe level operation will automatically resume.

7.3.6.3 Undervoltage Lockout (UVLO)

If at any time the voltage on the VCC pins falls below the undervoltage lockout threshold voltage, all circuitry in the device will be disabled, the FAULTn signal will be driven low, and internal logic will be reset. Operation will resume when VCC rises above the UVLO threshold.

Table 2. Device Protection

| FAULT | CONDITION | ERROR REPORT | H-BRIDGE | INTERNAL CIRCUITS | RECOVERY |

|---|---|---|---|---|---|

| VCC undervoltage (UVLO) | VCC < VUVLO | FAULTn | Disabled | Disabled | VCC > VUVLO |

| Overcurrent (OCP) | IOUT > IOCP | FAULTn | Disabled | Operating | Power Cycle VCC |

| Thermal Shutdown (TSD) | TJ > TTSD | FAULTn | Disabled | Operating | TJ < TTSD – THYS |

7.4 Device Functional Modes

The DRV8832 is active when either IN1 or IN2 are set to a logic high. Sleep mode is entered when both IN1 and IN2 are set to a logic low. When in sleep mode, the H-bridge FETs are disabled (Hi-Z).

Table 3. Modes of Operation

| FAULT | CONDITION | H-BRIDGE | INTERNAL CIRCUITS |

|---|---|---|---|

| Operating | IN1 or IN2 high | Operating | Operating |

| Sleep mode | IN1 and IN2 low | Disabled | Disabled |

| Fault encountered | Any fault condition met | Disabled | See Table 2 |

8 Application and Implementation

NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI’s customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

8.1 Application Information

The DRV8832 is used in brushed DC applications to provide a constant motor speed over varying voltages. The following design procedure can be used to configure the DRV8832 for a system with a VCC variance of 4 V to

6 V.

8.2 Typical Application

Figure 9 shows a common application of the DRV8832.

Figure 9. Typical Application Schematic

Figure 9. Typical Application Schematic

8.2.1 Design Requirements

Table 4 lists the design parameters for this application.

Table 4. Design Parameters

| DESIGN PARAMETER | REFERENCE | EXAMPLE VALUE |

|---|---|---|

| Motor voltage | VCC | 4 V |

| Motor RMS current | IRMS | 0.3 A |

| Motor start-up current | ISTART | 0.6 A |

| Motor current trip point | ILIMIT | 0.5 A |

8.2.2 Detailed Design Procedure

8.2.2.1 Motor Voltage

The motor voltage to use will depend on the ratings of the motor selected and the desired RPM. A higher voltage spins a brushed DC motor faster with the same PWM duty cycle applied to the power FETs. A higher voltage also increases the rate of current change through the inductive motor windings.

For the DRV8832, TI recommends setting a motor voltage at the lowest system VCC. This will maintain a constant RPM across varying VCC conditions.

For example if the VCC voltage can vary from 4.5 V to 5.5 V, setting the VSET voltage to 1.125 V will compensate for power supply variation. The DRV8832 will set the motor voltage at 4.5 V, even if VCC is 5.5 V.

8.2.2.2 Motor Current Trip Point

When the voltage on pin ISENSE exceeds VILIM (0.2 V), overcurrent is detected. The RSENSE resistor should be sized to set the desired ILIMIT level.

To set ILIMIT to 5 A, RISENSE = 0.2 V / 0.5 A = 0.4 Ω.

To prevent false trips, ILIMIT must be higher than regular operating current. Motor current during start-up is typically much higher than steady-state spinning, because the initial load torque is higher, and the absence of back-EMF causes a higher voltage and extra current across the motor windings.

It can be beneficial to limit start-up current by using series inductors on the DRV8832 output, as that allows ILIMIT to be lower, and it may decrease the system’s required bulk capacitance. Start-up current can also be limited by ramping the forward drive duty cycle.

8.2.2.3 Sense Resistor

For optimal performance, it is important for the sense resistor to be:

- Surface-mount

- Low inductance

- Rated for high enough power

- Placed closely to the motor driver

The power dissipated by the sense resistor equals IRMS2 × R. For example, if peak motor current is 1 A, RMS motor current is 0.7 A, and a 0.4-Ω sense resistor is used, the resistor will dissipate 0.7 A2× 0.4 Ω = 0.2 W. The power quickly increases with higher current levels.

Resistors typically have a rated power within some ambient temperature range, along with a derated power curve for high ambient temperatures. When a PCB is shared with other components generating heat, margin should be added. It is always best to measure the actual sense resistor temperature in a final system, along with the power MOSFETs, as those are often the hottest components.

Because power resistors are larger and more expensive than standard resistors, it is common practice to use multiple standard resistors in parallel, between the sense node and ground. This distributes the current and heat dissipation.

8.2.2.4 Low Power Operation

Under normal operation, using sleep mode to minimize supply current should be sufficient.

If desired, power can be removed to the DRV8832 to further decrease supply current. TI recommends removing power to the FAULTn pullup resistor when removing power to the DRV8832. Removing power from the FAULTn pullup resistor will eliminate a current path from the FAULTn pin through an ESD protection diode to VCC. TI also recommends setting both IN1 and IN2 as a logic low when power is removed.

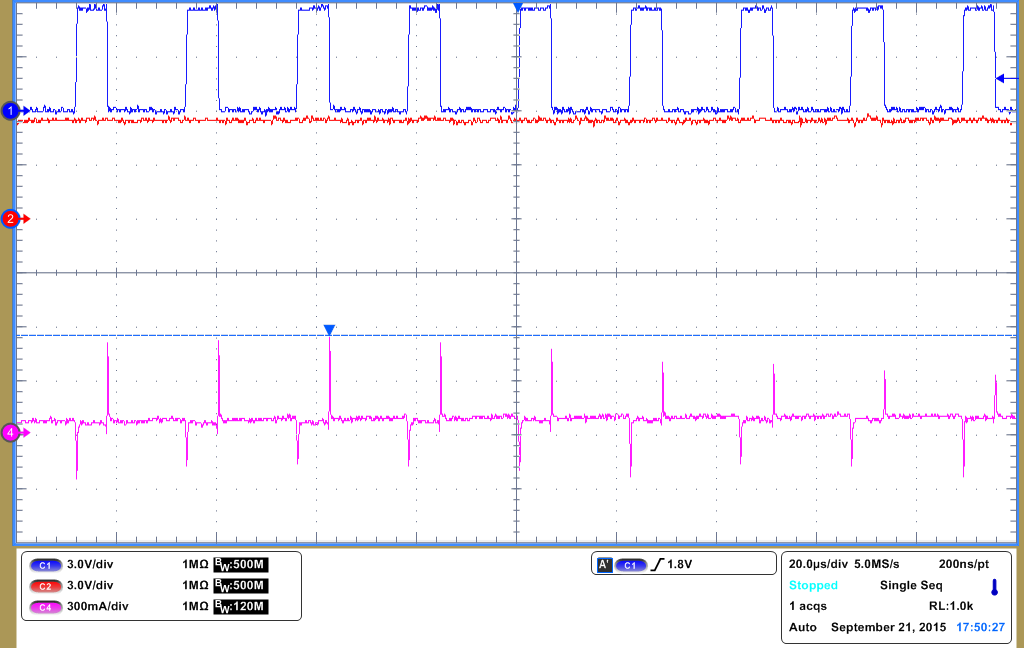

8.2.3 Application Curves

The following scope captures show how the output duty cycle changes to as VCC increases. This allows the motor to spin at a constant speed as VCC changes. At VCC=3.9V, the output duty cycle is 100% on. As the VCC voltage increases to greater than 4 V, the output duty cycle begins to decrease. The output duty cycle is shown at VCC=4.5 V, VCC=5 V and VCC=5.5 V.

- Channel 1 – OUT1: IN1 – Logic Low

- Channel 2 – OUT2: IN2 – Logic High

- Channel 4 – Motor current: VSET – 1 V

- Motor used: NMB Technologies Corporation, PPN7PA12C1

Figure 10. Output Pulse Width Modulating at VCC = 3.9 V

Figure 10. Output Pulse Width Modulating at VCC = 3.9 V

Figure 12. Output Pulse Width Modulating at VCC = 4.5 V

Figure 12. Output Pulse Width Modulating at VCC = 4.5 V

Figure 14. Output Pulse Width Modulating at VCC = 5.5 V

Figure 14. Output Pulse Width Modulating at VCC = 5.5 V

Figure 11. Output Pulse Width Modulating at VCC = 4 V

Figure 11. Output Pulse Width Modulating at VCC = 4 V

Figure 13. Output Pulse Width Modulating at VCC = 5 V

Figure 13. Output Pulse Width Modulating at VCC = 5 V