SLVSCB2D October 2013 – April 2018 TPS7B67-Q1

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Device Comparison

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Detailed Description

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

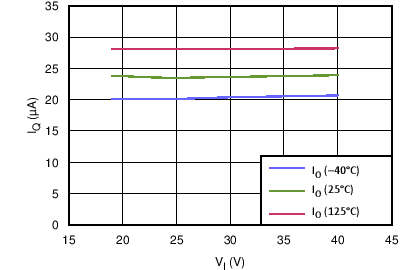

7.7 Typical Characteristics

(VO = 1.5 V)

(VO = 18 V)

(VI = 14 V, VO = 1.5 V)

(VO ≥ 2.5 V)

(Fixed 3.3-V Version, IL = 0)

10-µF Ceramic Output Capacitor

(VI = 14 V, VO = 1.5 V)

(VI = 24 V, VO = 18 V)

(VO ≤ 2.5 V)

(Fixed 5-V Version, IL = 0)

(VI = 14 V, CO = 47 µF, IL = 25 mA)