SLVUBI1 May 2021

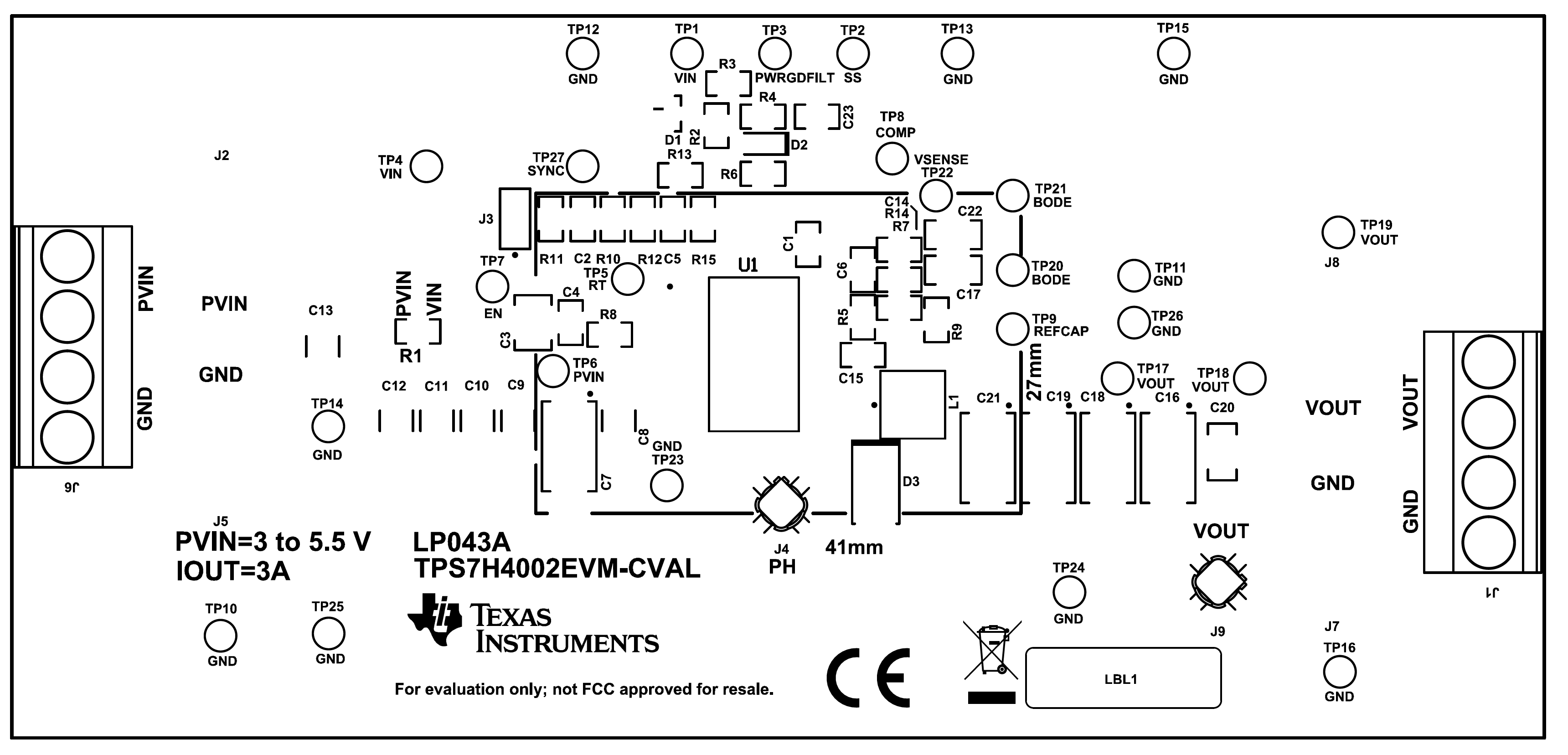

7 Board Layout

Figure 7-1 through Figure 7-11 illustrate the layer stack of the TPS7H4002EVM-CVAL board.

Figure 7-1 Top Overlay

Figure 7-1 Top Overlay Figure 7-2 Top Solder

Figure 7-2 Top Solder Figure 7-3 Layer 1 -Top Layer

Figure 7-3 Layer 1 -Top Layer Figure 7-4 Layer 2- GND

Figure 7-4 Layer 2- GND Figure 7-5 Layer Three - Signal

Figure 7-5 Layer Three - Signal Figure 7-6 Layer Four -Bottom Layer

Figure 7-6 Layer Four -Bottom Layer Figure 7-7 Bottom Solder

Figure 7-7 Bottom Solder Figure 7-8 Bottom Overlay

Figure 7-8 Bottom Overlay Figure 7-9 Drill Drawing

Figure 7-9 Drill Drawing Figure 7-10 Drill Table

Figure 7-10 Drill Table Figure 7-11 Board Dimensions

Figure 7-11 Board Dimensions