SLVUBW7 May 2020

- TPS7H4001QEVM-CVAL Evaluation Module User's Guide

7 Board Layout

The following is the layer stack of the TPS7H4001QEVM-CVAL board.

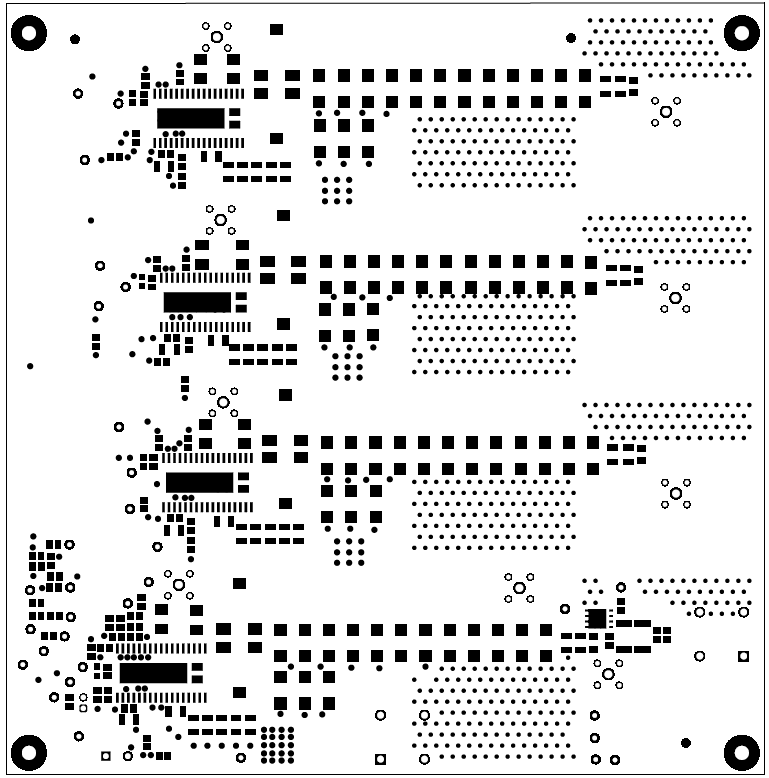

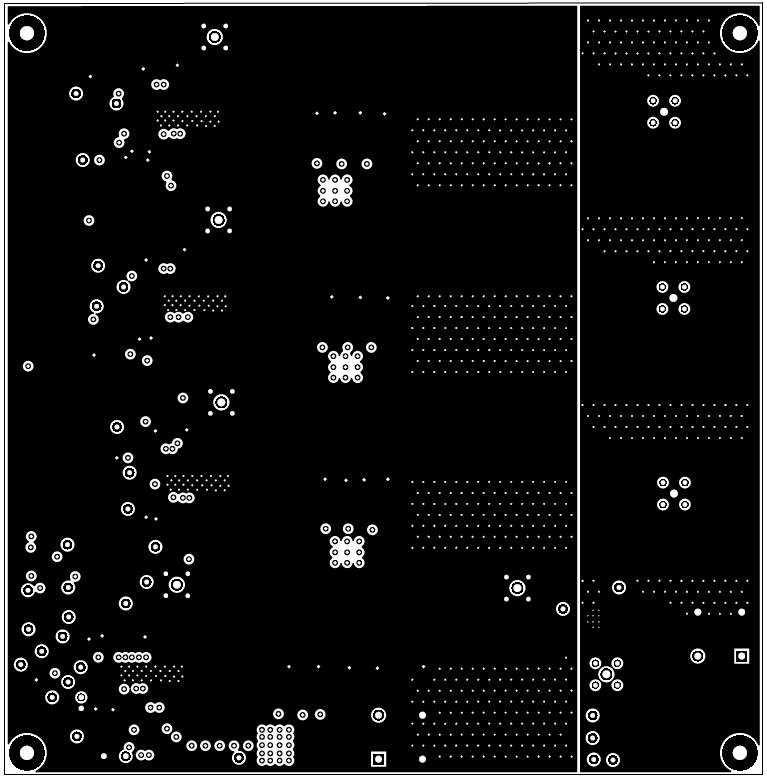

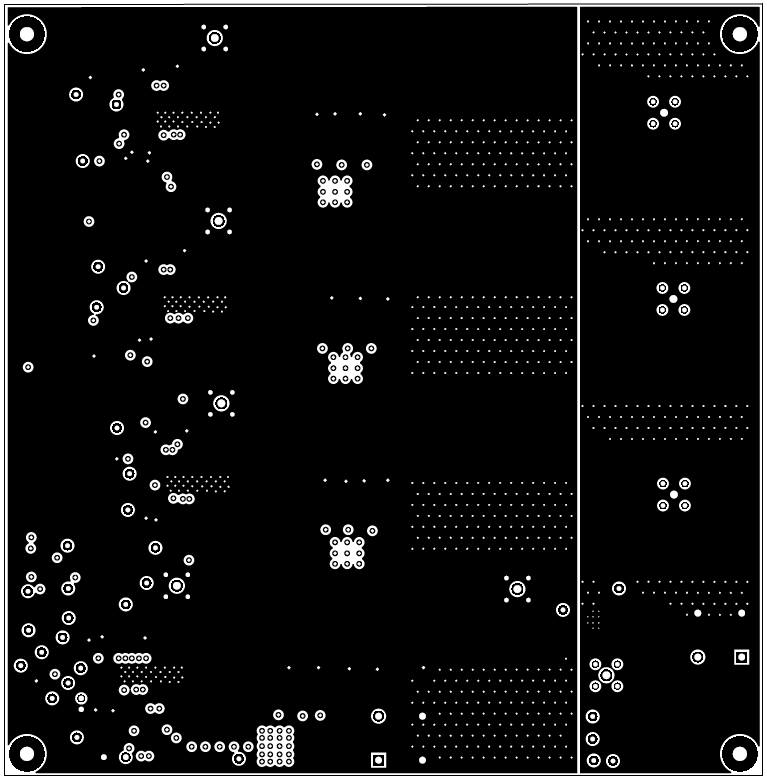

Figure 23. Top Overlay

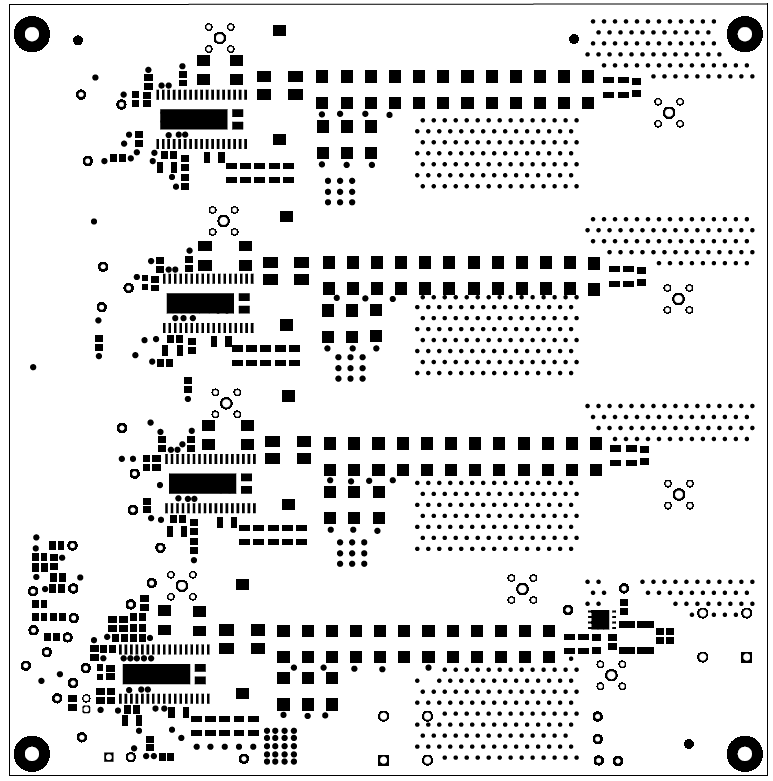

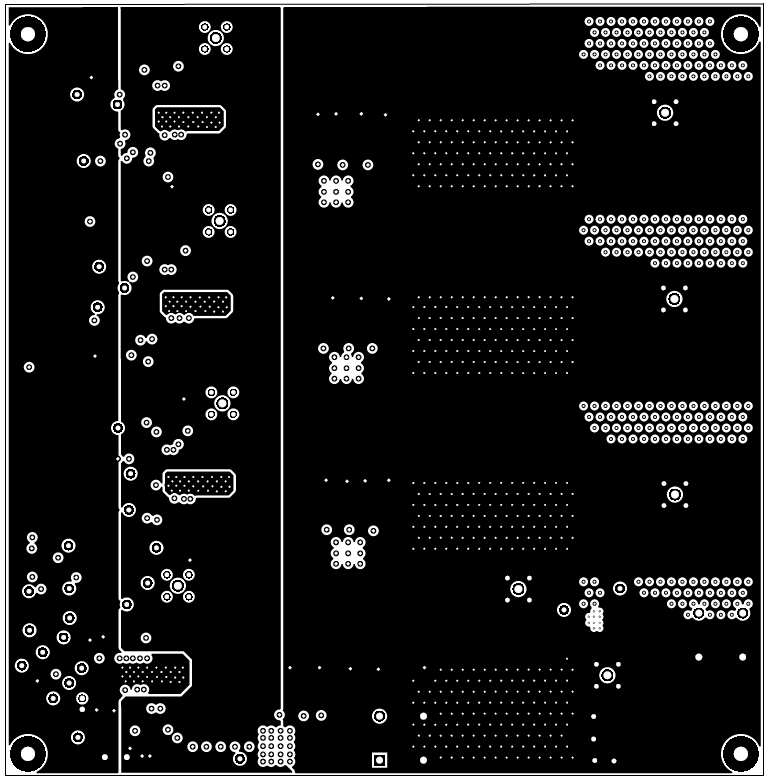

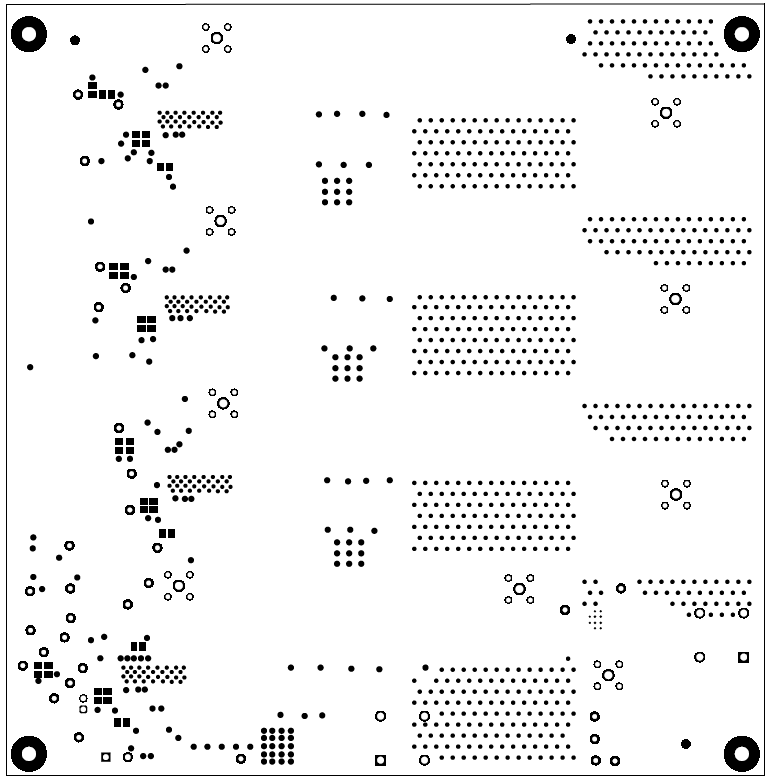

Figure 23. Top Overlay  Figure 24. Top Solder

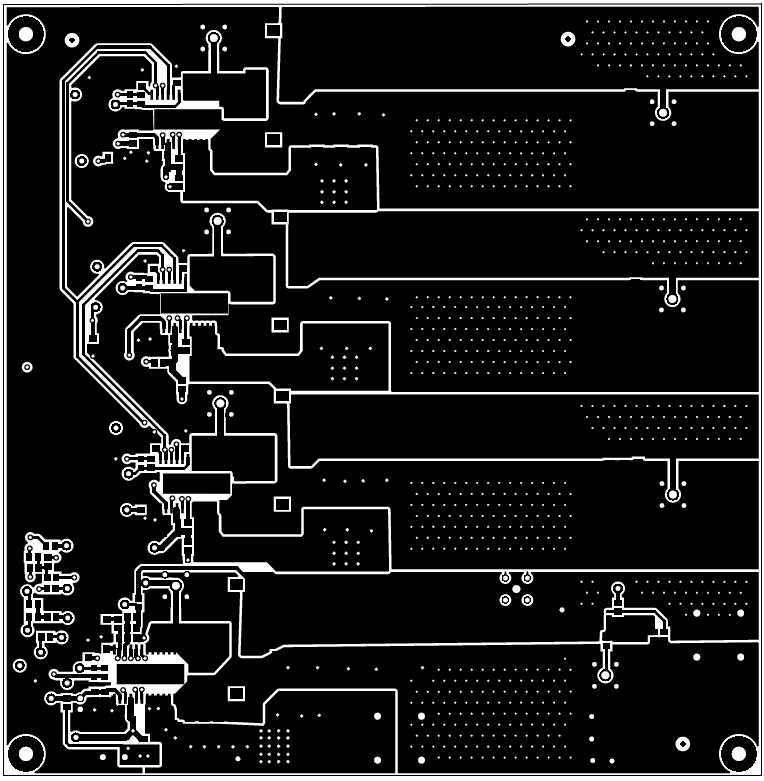

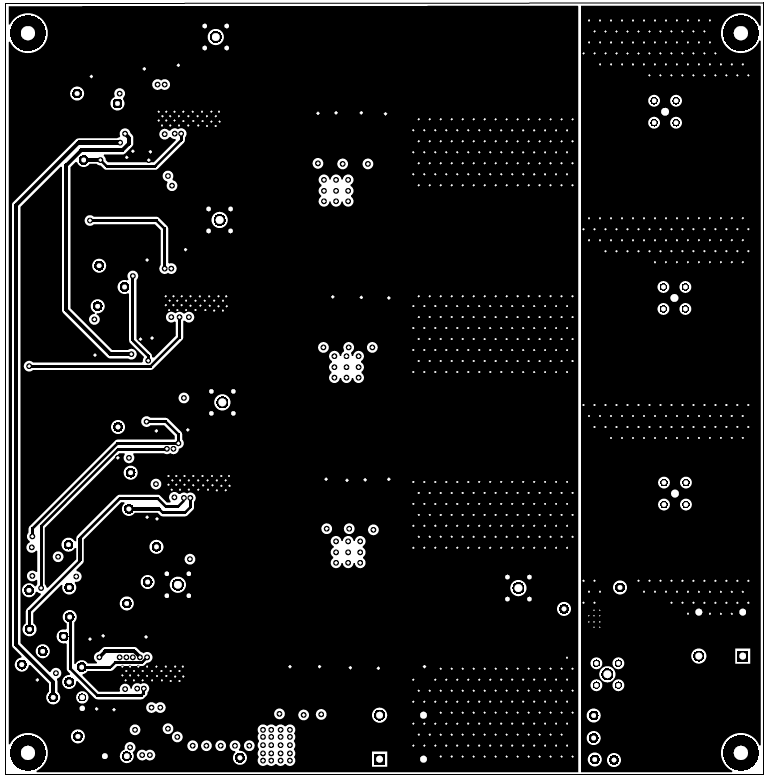

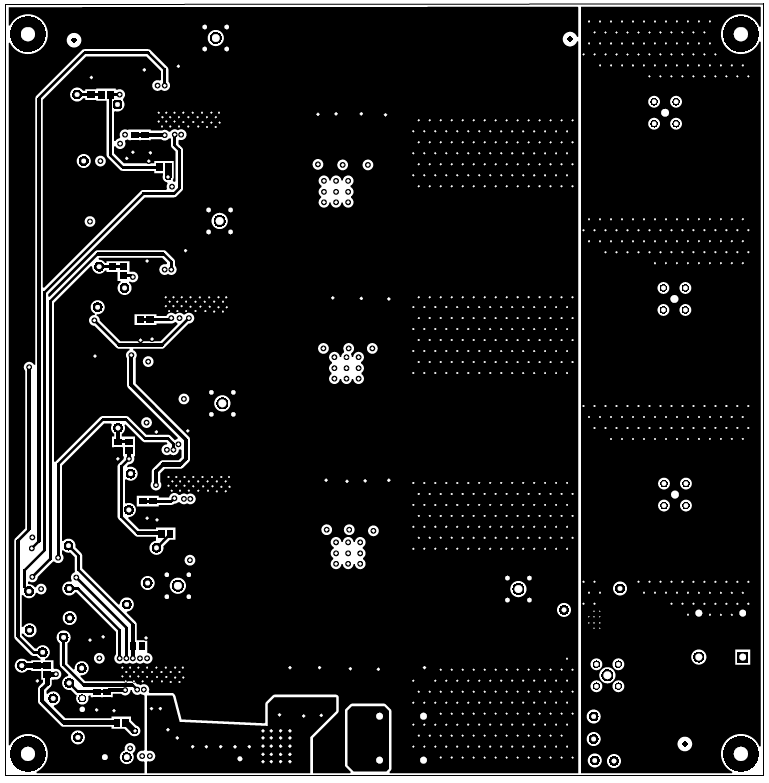

Figure 24. Top Solder  Figure 25. Top Layer

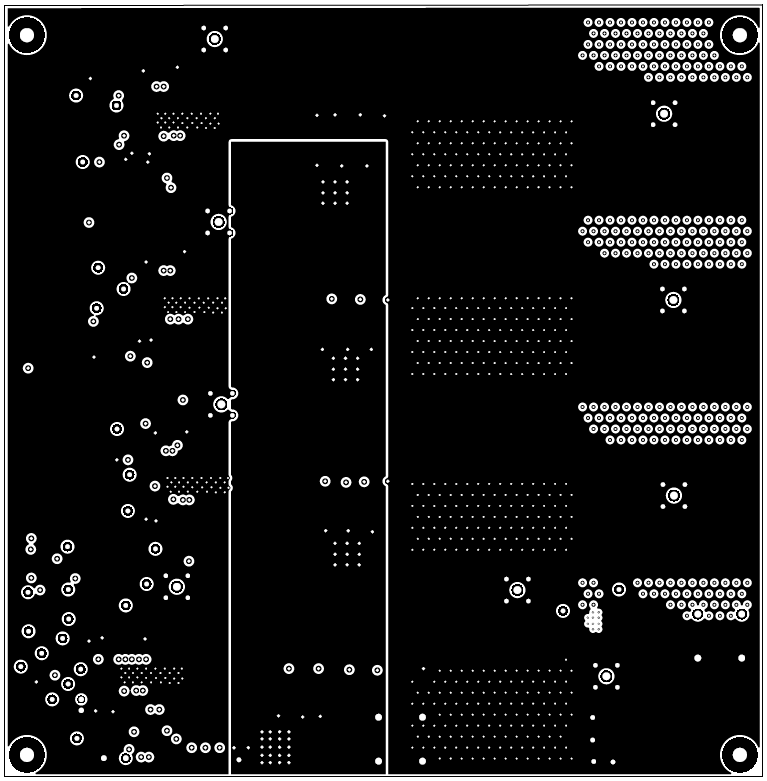

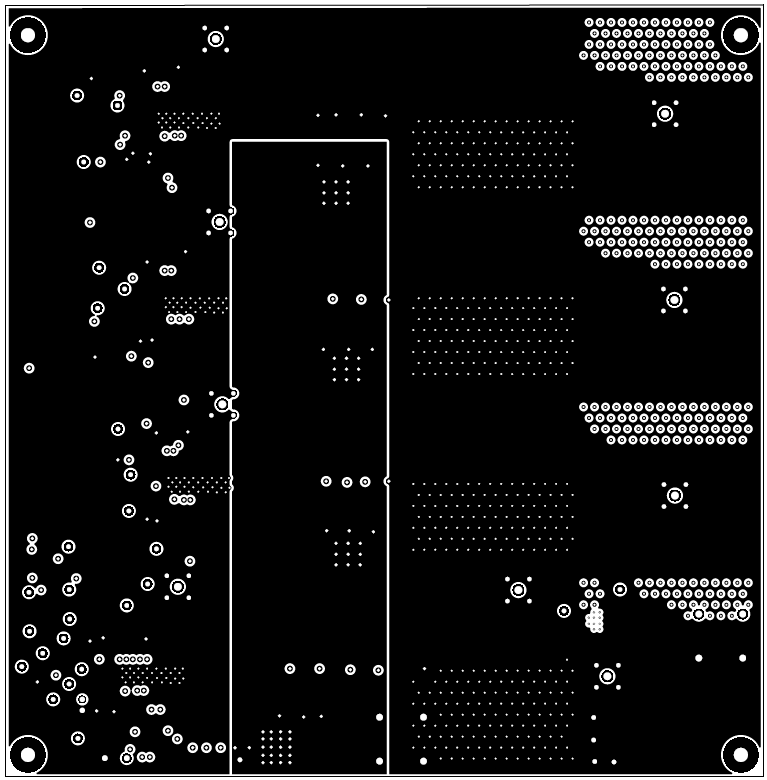

Figure 25. Top Layer  Figure 26. Signal Layer One

Figure 26. Signal Layer One  Figure 27. Signal Layer Two

Figure 27. Signal Layer Two  Figure 28. Signal Layer Three

Figure 28. Signal Layer Three  Figure 29. Signal Layer Four

Figure 29. Signal Layer Four  Figure 30. Signal Layer Five

Figure 30. Signal Layer Five  Figure 31. Signal Layer Six

Figure 31. Signal Layer Six  Figure 32. Bottom Layer

Figure 32. Bottom Layer  Figure 33. Bottom Solder

Figure 33. Bottom Solder  Figure 34. Bottom Overlay

Figure 34. Bottom Overlay