SLVUC06 October 2020 TPS650320-Q1

- Trademarks

- 1Introduction

- 2EVM Configurations

- 3Test Points

- 4Graphical User Interface

- 5Typical Performance Plots

- 6TPS650320-Q1 EVM Schematic

- 7TPS650320-Q1 EVM PCB Layers

- 8TPS650320-Q1 EVM Bill of Materials

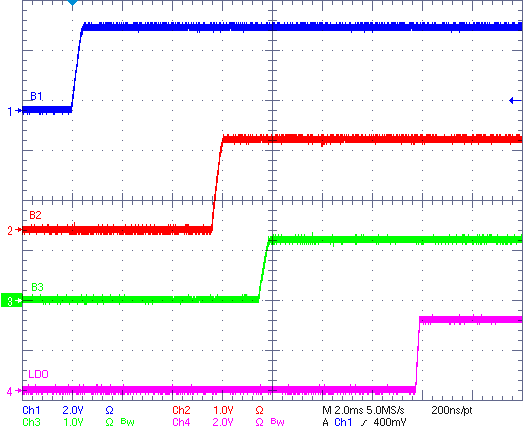

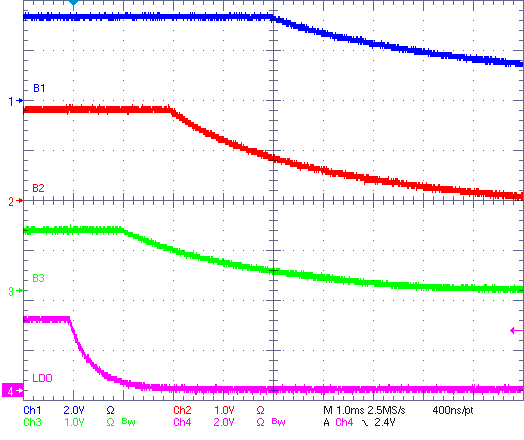

5.1 Power Sequence Plots

Figure 5-1 TPS650320-Q1 Default Power

Up Sequence

Figure 5-1 TPS650320-Q1 Default Power

Up Sequence Figure 5-2 TPS650320-Q1 Default Power

Down Sequence

Figure 5-2 TPS650320-Q1 Default Power

Down Sequence