SLVUCC4 January 2022 TPS629206

3.8 Loop Response Measurement

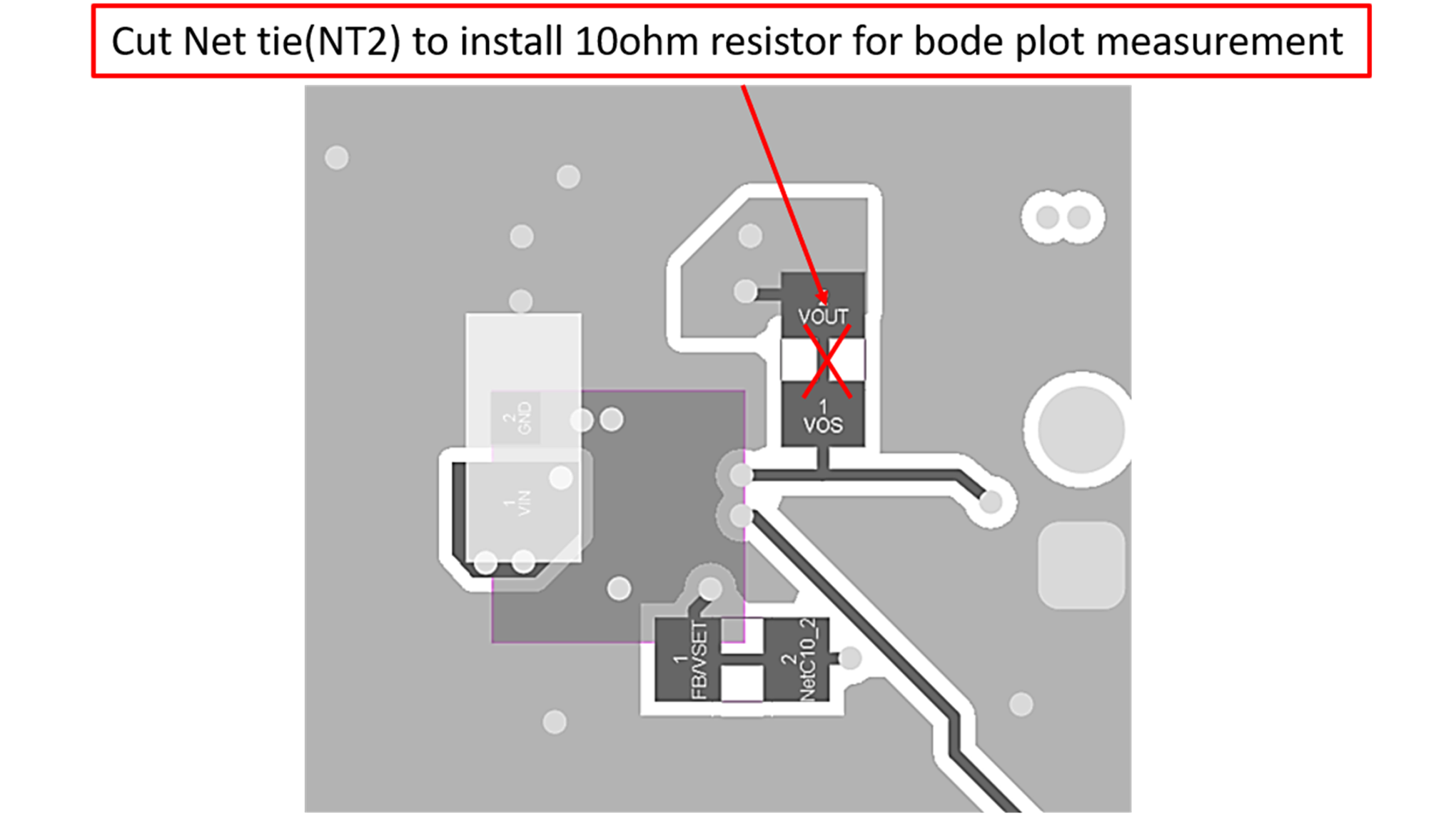

The loop response can be measured after simple changing to the board. First, cut net tie (NT2) and install a 10-Ω 0603 resistor on the bottom of board. Figure 3-2 shows this change. An AC signal (10-mV, peak-to-peak amplitude is recommended) can be injected into the control loop across the added 10-Ω resistor.

Figure 3-2 Bode Plot Measurement Board

Modification

Figure 3-2 Bode Plot Measurement Board

Modification