SLVUCC4 January 2022 TPS629206

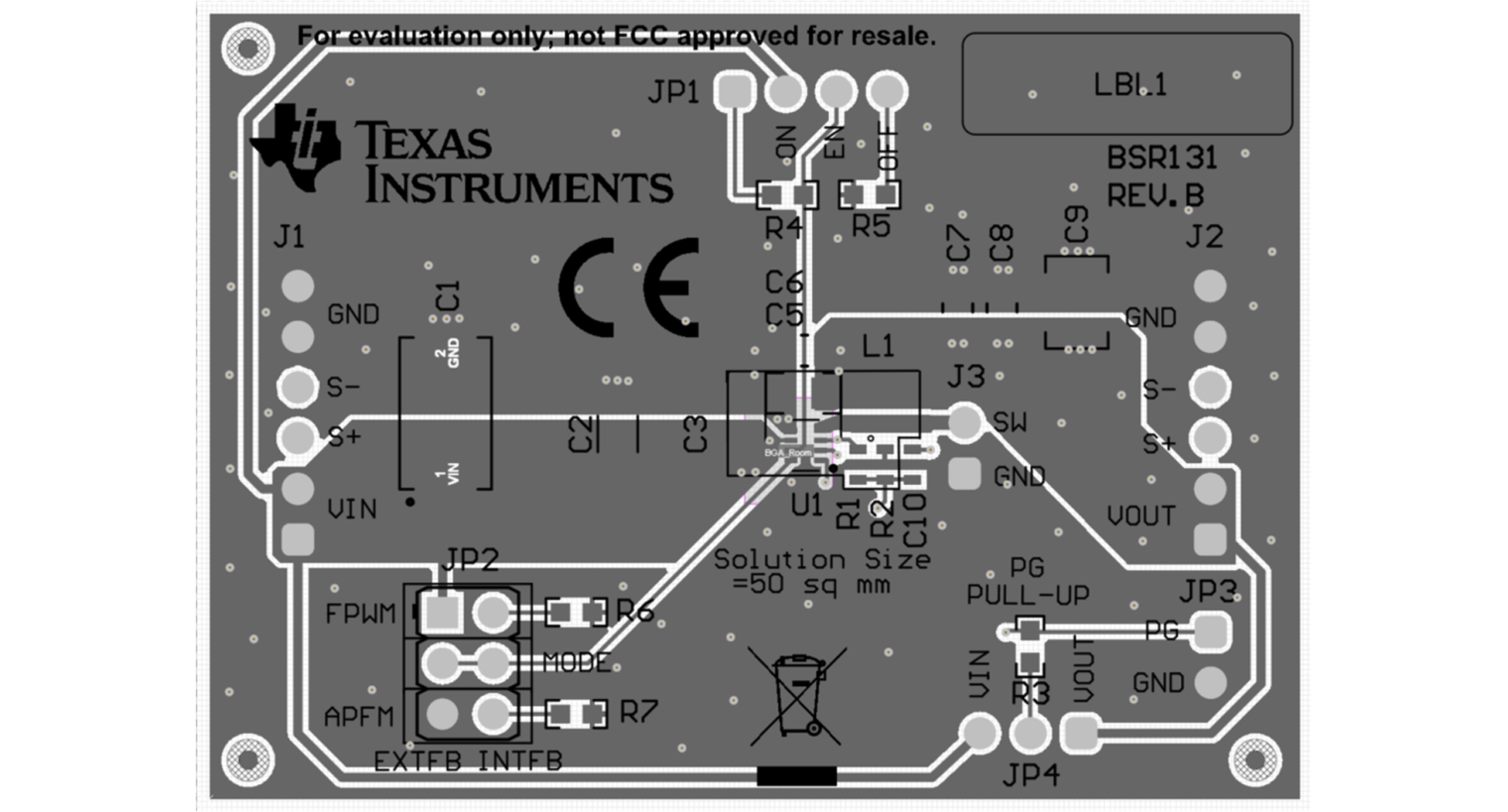

6 Board Layout

This section provides the EVM board layout and illustrations.

Figure 6-1 Top

Assembly

Figure 6-1 Top

Assembly Figure 6-2 Top

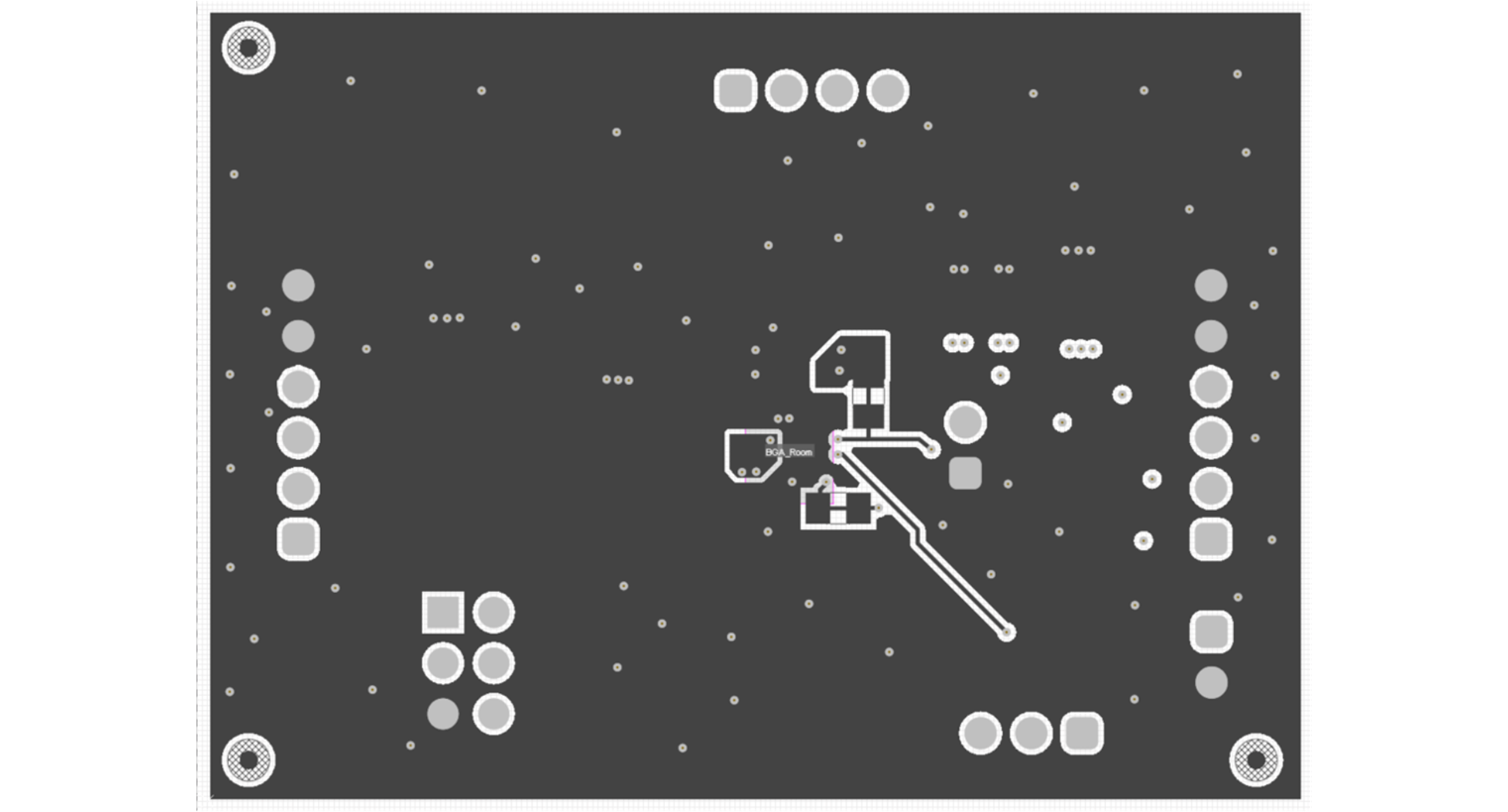

Layer

Figure 6-2 Top

Layer Figure 6-3 Internal

Layer 1

Figure 6-3 Internal

Layer 1 Figure 6-4 Internal

Layer 2

Figure 6-4 Internal

Layer 2 Figure 6-5 Bottom

Layer

Figure 6-5 Bottom

Layer