SLVUCK5 December 2022 TLVM23625

6 Layout

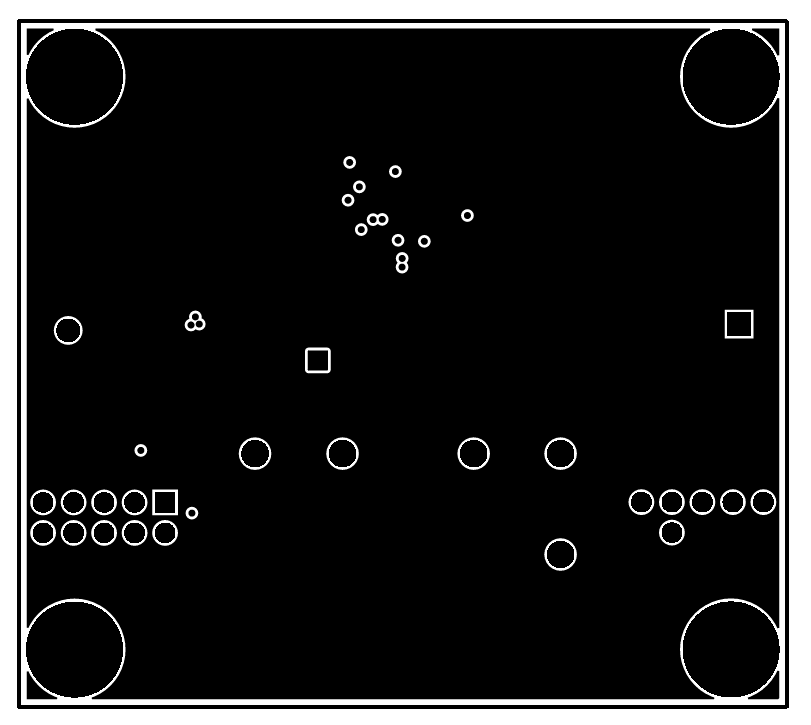

Figure 6-1 PCB Top 2-D (TLVM23625EVM)

Figure 6-1 PCB Top 2-D (TLVM23625EVM) Figure 6-2 PCB Bottom 2-D

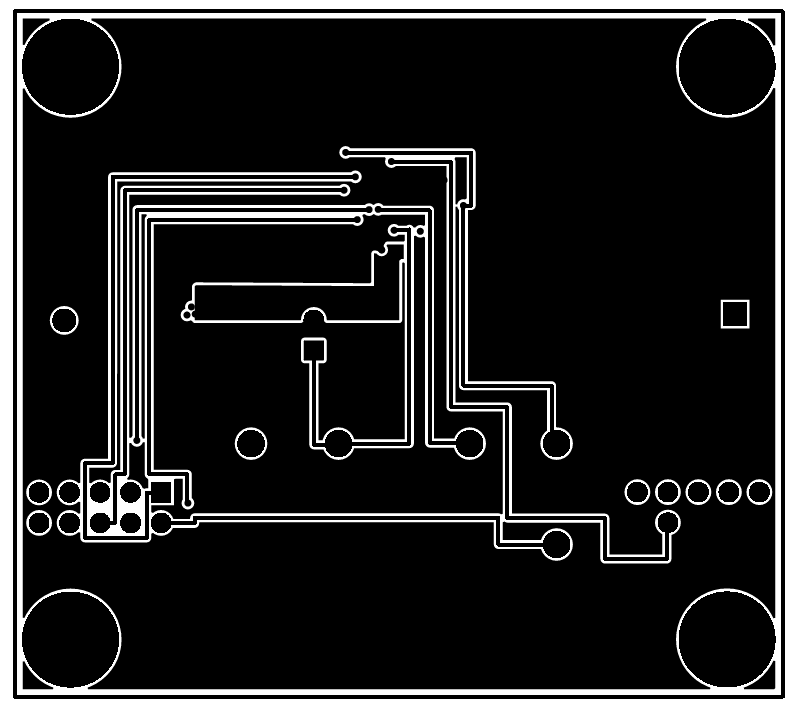

Figure 6-2 PCB Bottom 2-D Figure 6-3 Top Layer

Figure 6-3 Top LayerReserved for solid ground plane for low-noise and optimized thermal design.

Figure 6-4 Mid Layer 1

Figure 6-4 Mid Layer 1Primary routing layer

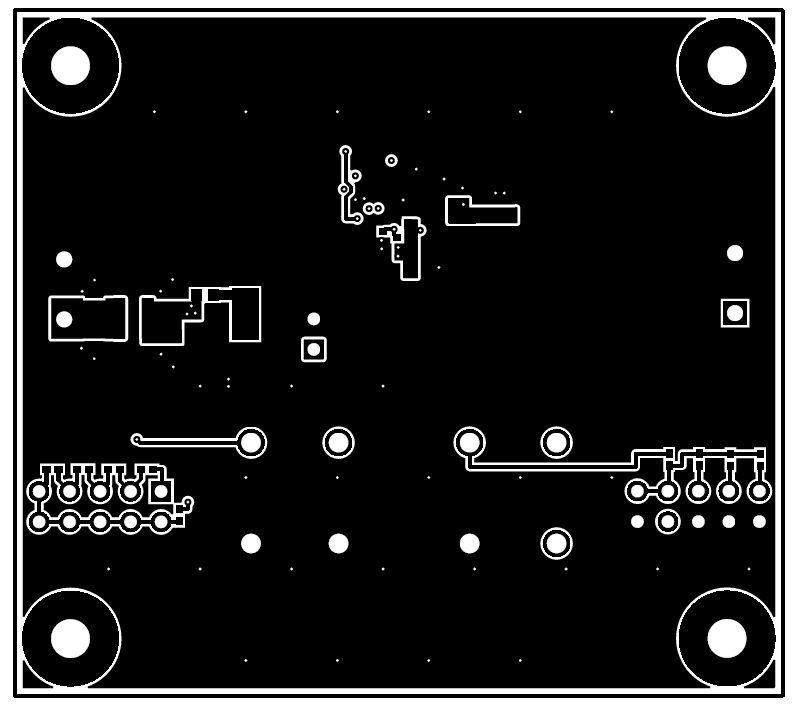

Figure 6-5 Mid Layer 2

Figure 6-5 Mid Layer 2Reserved for PI filter and non-critical passive component placement (minus input capacitor). An input capacitor is placed on the bottom side of the PCB as it provides a slightly lower input loop inductance. A single layer implementation is satisfactory as well.

Figure 6-6 Bottom Layer

Figure 6-6 Bottom Layer