SLVUCX5 May 2024

2.2.4 Stack-up Headers

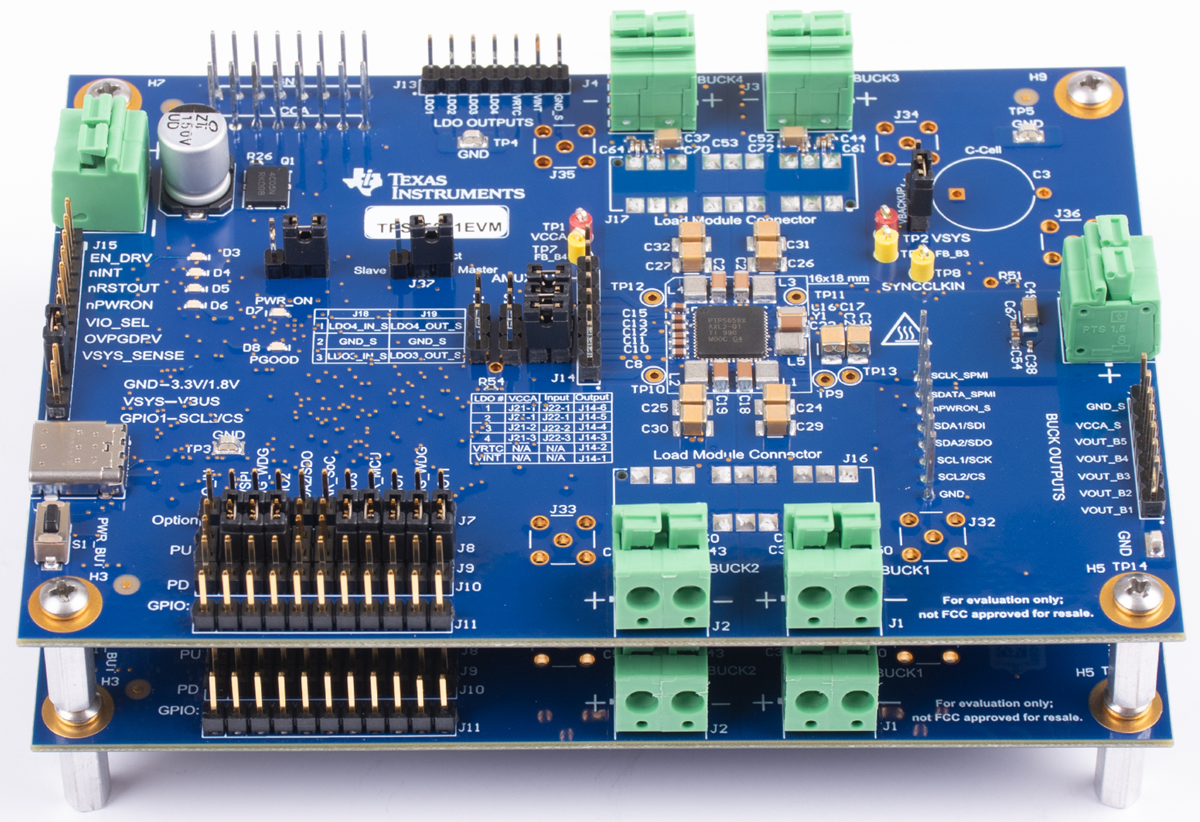

As shown in Figure 3-3, multiple boards can be configured into a controller-target relationship (1 controller and up to 5 targets) and physically stacked upon each other. Stacked boards can be either LP87694Q1EVM, LP87644Q1EVM, TPS65941111EVM or TPS65941212EVM evaluation modules. VCCA and GND are shared between boards on headers J27 and J28. Communication between the boards is shared on header J29. This header, J29, is marked on the bottom silkscreen, as shown in Figure 3-4.

Figure 2-3 EVM Controller-Target

Configuration

Figure 2-3 EVM Controller-Target

Configuration Figure 2-4 EVM (Bottom View)

Figure 2-4 EVM (Bottom View)Setting J22 to controller position connects nPWRON signal from controller to target through nPWRON_S pin on connector J29. This signal allows a SPMI connection between controller and target PMICs. Jumper J22 needs to be set to target position on target EVMs to disable pull-up resistors. By using this stackup configuration, the power up sequences of one or more target EVMs always follow the controller.

Figure 2-5 Header J22, Recommended Power

Sequence (Enable) for Controller and One or More Targets

Figure 2-5 Header J22, Recommended Power

Sequence (Enable) for Controller and One or More Targets| Configuration | Description |

|---|---|

| Open | When used as a single PMIC (no stacking). The controller EVM can use GPIO8 and GPIO9 to be connected to a MCU on EVM. I2C pull-up resistors are enabled. |

| Target, M/S select: closed | Target mode: the target EVM can use GPIO8 and GPIO9 for SPMI communication between PMICs. I2C pull-up resistors are disabled on target EVMs. |

| M/S select, controller: closed | Controller mode: the controller EVM can use GPIO8 and GPIO9 for SPMI communication between PMICs. I2C pull-up resistors are enabled on controller EVM. |