SLVUCZ2 May 2024

2.1 Headers and Test Points Information

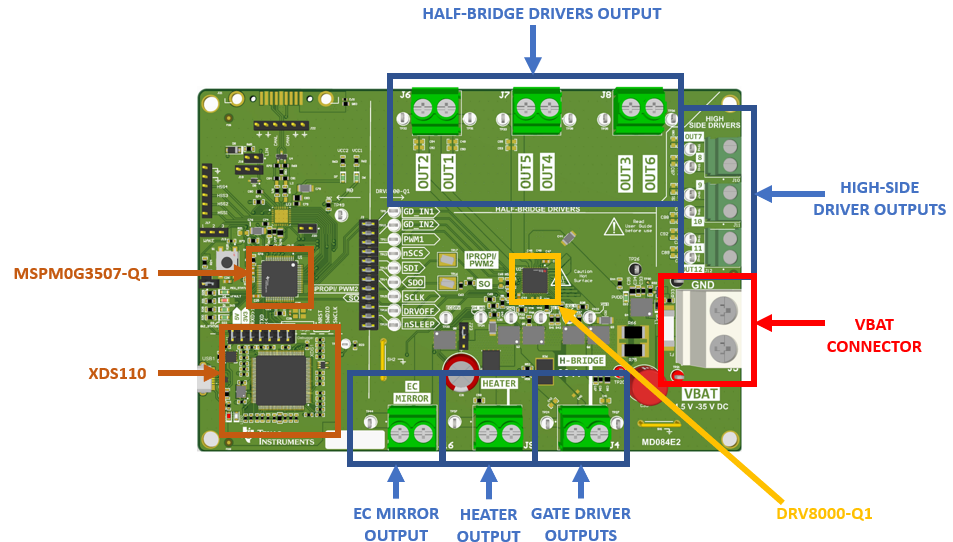

Figure 2-1 DRV8000-Q1EVM (MD084-001) (Top

View)

Figure 2-1 DRV8000-Q1EVM (MD084-001) (Top

View)CAUTION: Hot surface temperature. The EVM can have high surface temperatures marked by the FIRE triangular symbol on the EVM. Avoid touching the marked hot surface area when driving high currents to prevent potential burn damage.

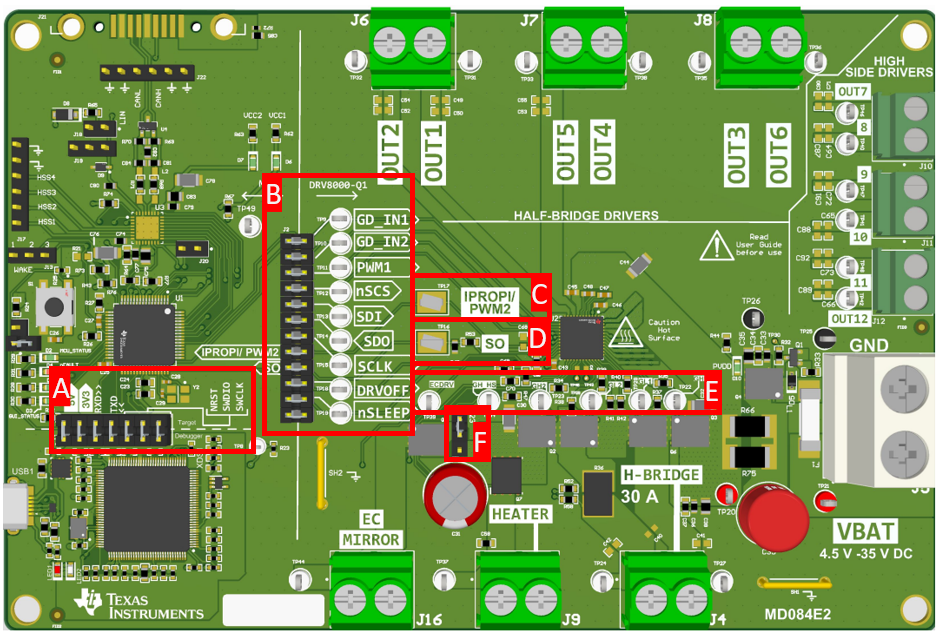

Figure 2-2 DRV8000-Q1EVM Header and Test

Point Information

Figure 2-2 DRV8000-Q1EVM Header and Test

Point InformationTable 2-1 Header and Test Point

Description - DRV8000-Q1EVM

| Component label | Description |

|---|---|

| Aee | XDS110 header between MSP432E401Y and MSPM0G3507. |

| B |

Main signal header:

|

| C |

IPROPI/ PWM2 - Sense output is multiplexed from any of driver load current feedback, PVDD voltage feedback, or thermal cluster temperature feedback. Can also be configured as second PWM pin input for half-bridge drivers. |

| D | SO - Shunt amplifier output. |

| E |

Gate Driver, EC Driver, Heater Test points (Left to Right):

|

| F | Drain of external EC

voltage regulation FET (Top to Bottom):

|