SNAA365 June 2024 LMK5B33216

- 1

- Abstract

- Trademarks

- 1Hardware Architecture

- 2syn1588® Synchronization Algorithm

- 3Test Setup

- 4PTP System Application

- 5Additional Development

- 6Conclusion

- 7References

3 Test Setup

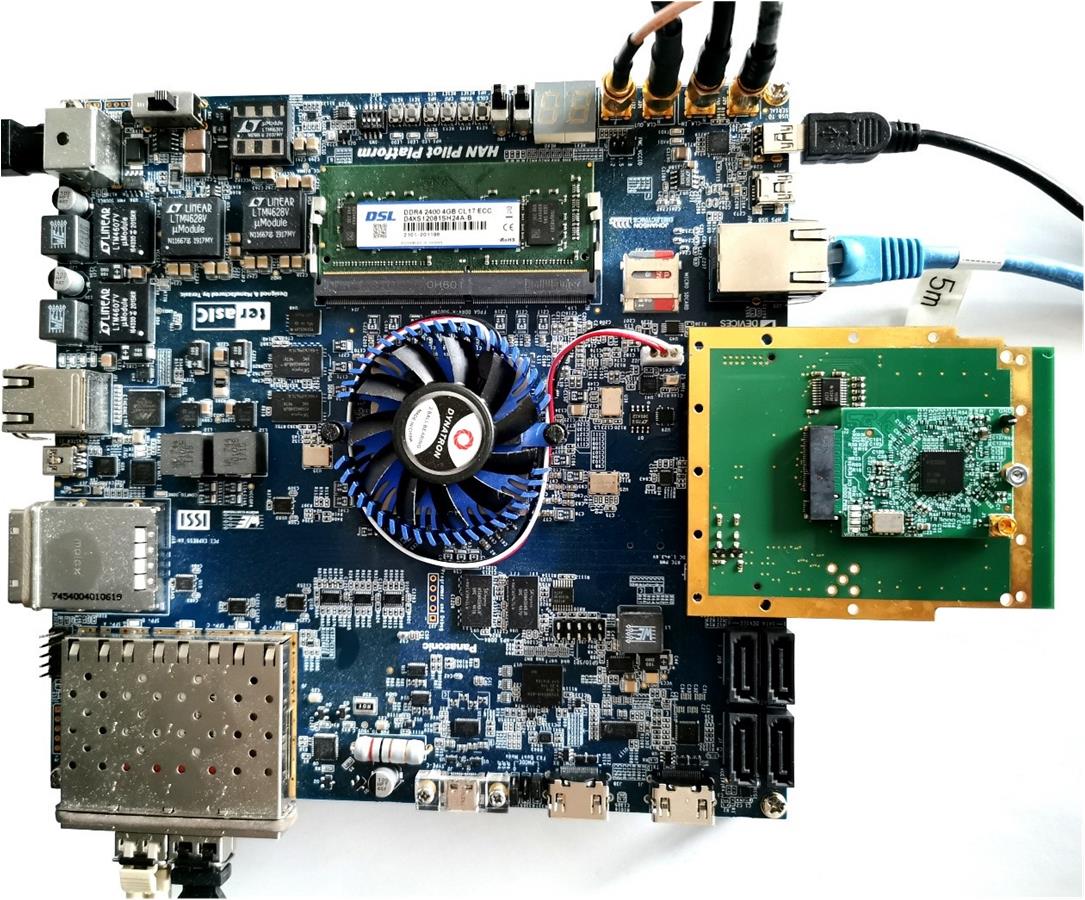

The PTP implementation on the Intel® FPGA is functionally tested by mounting the LMK5XXXXXS1 M2 module onto an interface connector board to match the FMC connector of the HAN Pilot platform. The setup is captured in Figure 3-1.

Figure 3-1 Lab Measurement Setup

Figure 3-1 Lab Measurement Setup