SNAA365 June 2024 LMK5B33216

- 1

- Abstract

- Trademarks

- 1Hardware Architecture

- 2syn1588® Synchronization Algorithm

- 3Test Setup

- 4PTP System Application

- 5Additional Development

- 6Conclusion

- 7References

3.2 Compliance Test Setup

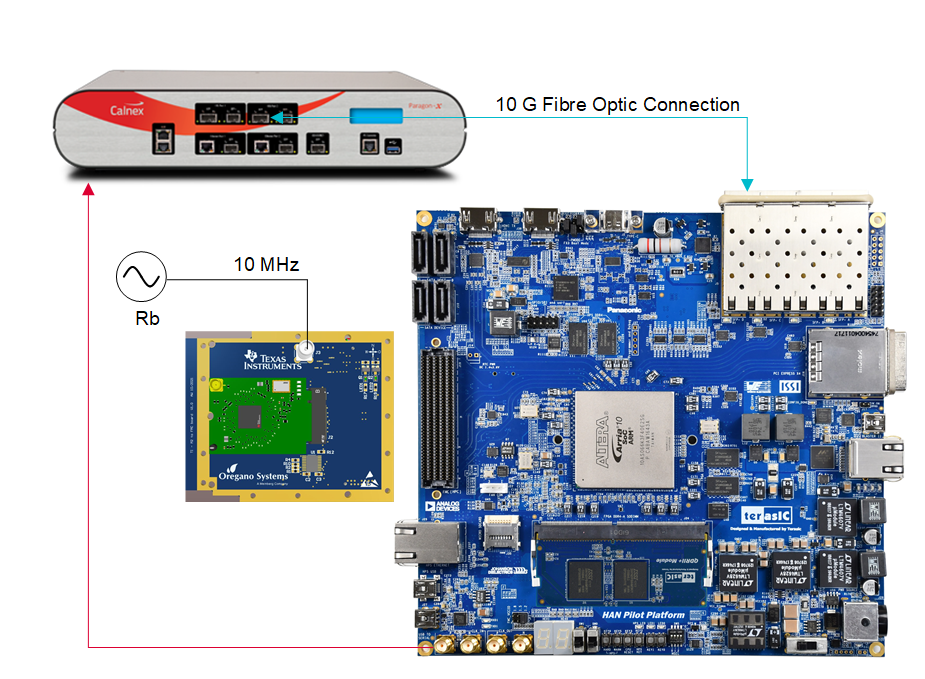

The compliance test setup is shown in Figure 3-4. In some test cases the Calnex Paragon-X is replaced with the Calnex Neo for improved nanosecond-level accuracy.

Figure 3-4 Compliance Test Setup

Figure 3-4 Compliance Test Setup