SNAA417 September 2024 LMH1239

1 Introduction

In August of 1992, Japanese Scientist Takeo Iguchi released a paper discussing two areas of concerns when using an SDI data scrambler. One area of concern was that low frequency content can cause a DC shift. The second area of concern was the possibility of a long-run-length data pattern prohibiting the PLL from seeing data transitions. Iguchi proposed a method to generate the most undesirable – but still possible – signals and pass them over the SDI channel as a test signal. In this scenario. to recreate this undesirable effect – 10-bits 0x300h followed by a 0x198h values are used during the active line, excluding EAV, SAV, and ancillary data.

The pathological pattern can create long run lengths of 0s or 1s because of SDI's NRZI data pattern and scrambler equation. A long length of 1s or 0s creates an envelope or DC shift. Using a large coupling capacitor value, the DC shift can be eliminated. RP178 SMPTE specification is the only SMPTE document describing this occurrence using a scrambler for SMPTE159M/259M/244M. In these SMPTE specs, this stress pattern is used to generate maximum DC content/shift. Applying the sequence of 300h,198h continuously during the active line can produce a signal of 19 ones(zeros) followed by one zero (one) state in a repetitive manner - once the scrambler obtains the required starting point or seed.

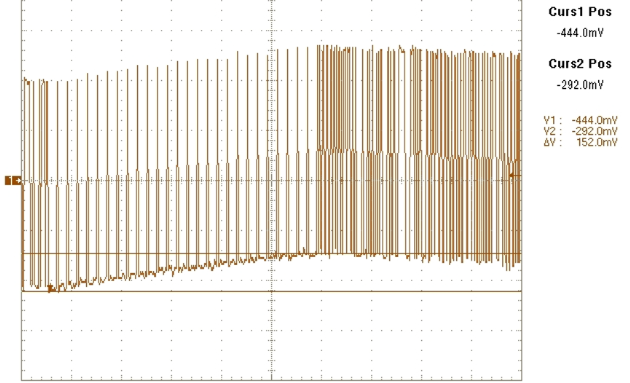

As noted earlier, a large value of AC coupling capacitor can be used to eliminate this DC shift due to the pathological data pattern. ST-292 and ST-424 and higher data rates called for a maximum of 50mV DC wander. An old SDI generator used a small AC coupling capacitor value in the order of nano-farads. In the case of the Figure 1-1, DC wander is measured at about 152mV.

Figure 1-1 DC Wander from the Pathological Pattern at

270Mbps

Figure 1-1 DC Wander from the Pathological Pattern at

270Mbps