SNAU182A March 2021 – May 2022

3.2.1 FSK Modulation

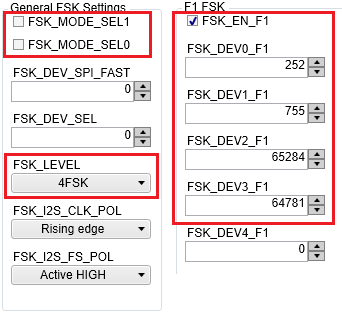

Direct digital FSK modulation is supported in LMX2571. FSK PIN mode supports discrete 2-, 4-, or 8-level FSK modulation while other FSK modes support arbitrary level FSK modulation. Table 3-2 is an FSK PIN mode example.

Table 3-2 FSK PIN Mode Example

| PARAMETER | EXAMPLE VALUE |

|---|---|

| Phase detector frequency | 80 MHz |

| CHDIV1 | Divided by 4 |

| CHDIV2 | Divided by 1 |

| PLL_DEN | 224 |

| Prescalar | 2 |

| Frequency deviation | ±600 Hz; ±1800 Hz |

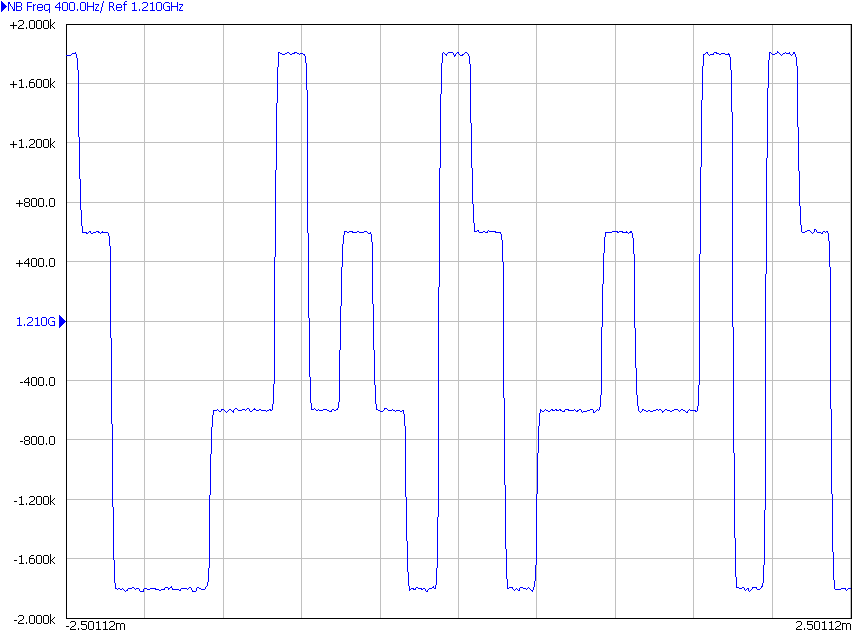

Continue to toggle the FSK_D[1:0] and FSK_DV pins, the output is a discrete 4-level FSK modulated signal.

Figure 3-3 FSK PIN

Mode Setting

Figure 3-3 FSK PIN

Mode Setting Figure 3-4 FSK PIN Mode

Figure 3-4 FSK PIN Mode