SNAU277C April 2022 – October 2024 LMK6C , LMK6D , LMK6H , LMK6P

2.1.1 Connection Diagram

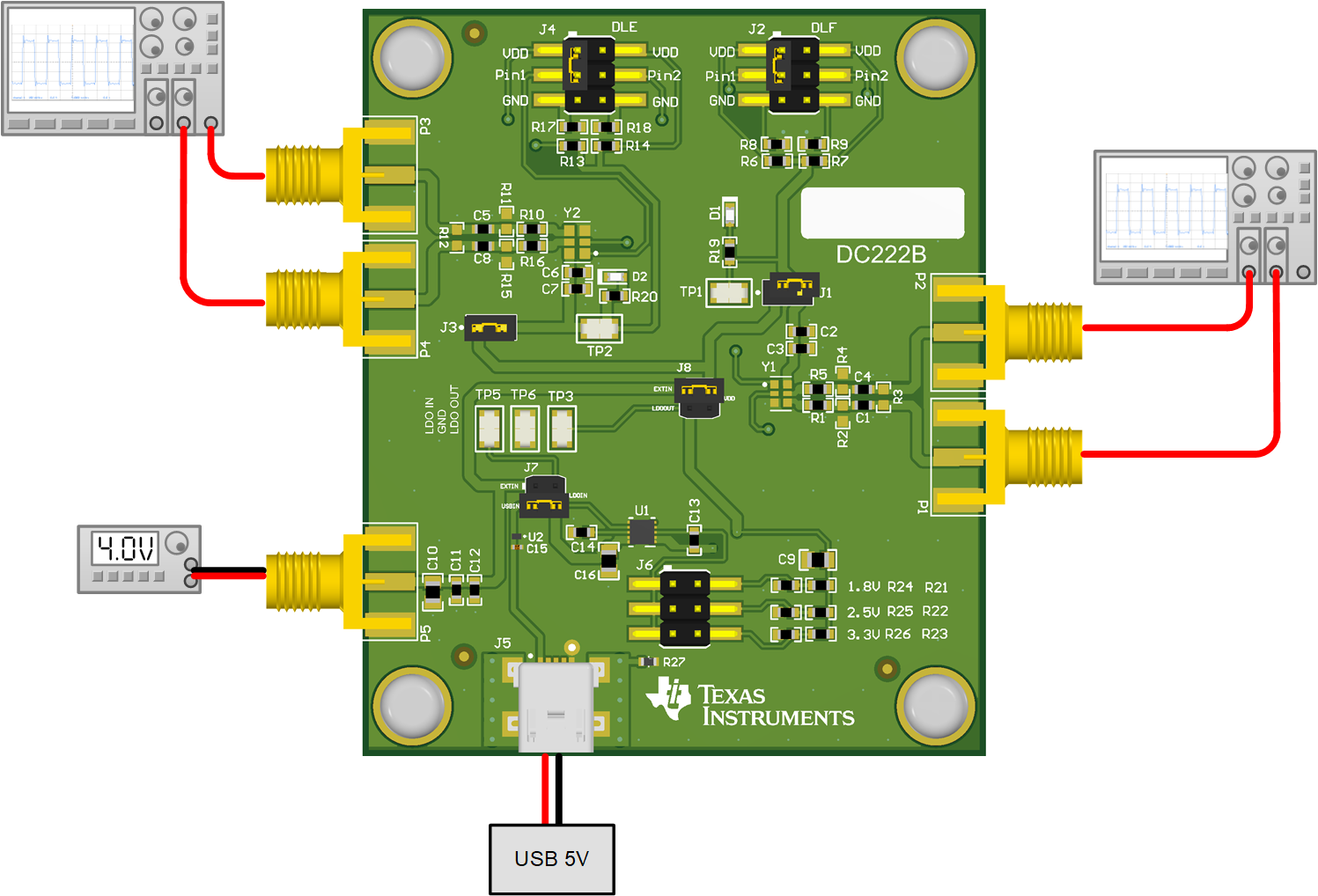

Figure 2-1 shows the LMK6EVM (DCC222A) connection diagram. To test LMK6xDLF variants (DLF 2.5mm × 2.0mm package), the device must be soldered on Y1, and P1 and P2 can be connected to an oscilloscope or phase noise analyzer to evaluate the device output. Similarly for LMK6xDLE variants (DLE 3.2mm × 2.5mm package), the device must be soldered on Y2, and P3 and P4 used accordingly to measure the output. Note that for LMK6C variants with an LVCMOS output format, only the positive clock output connection is used. The 4-pin LMK6C variants can share the same footprint as the 6-pin LMK6D/P/H variants. The corner pins are shared, but the middle pins are left unused for the LMK6C devices.

Figure 2-1 Connection Diagram

Figure 2-1 Connection Diagram