SNAU296 December 2023 LMK5C33414A

- 1

- Abstract

- Trademarks

- 1Introduction

- 2EVM Quick Start

- 3EVM Configuration

-

4EVM

Schematics

- 4.1 Power Supply Schematic

- 4.2 Alternative Power Supply Schematic

- 4.3 Power Distribution Schematic

- 4.4 LMK5C33414A and Input References IN0 to IN3 Schematic

- 4.5 Clock Outputs OUT0 to OUT3 Schematic

- 4.6 Clock Outputs OUT4 to OUT9 Schematic

- 4.7 Clock Outputs OUT10 to OUT13 and Clock Inputs IN2 and IN3 Schematic

- 4.8 XO Schematic

- 4.9 Logic I/O Interfaces Schematic

- 4.10 USB2ANY Schematic

- 5EVM Bill of Materials

-

6Appendix A - TICS Pro LMK5C33414A Software

- 6.1 Using the Start Page

- 6.2 Using the Status Page

- 6.3 Using the Input Page

- 6.4 Using APLL1, APLL2, and APLL3 Pages

- 6.5 Using the DPLL1, DPLL2, and DPLL3 Pages

- 6.6 Using the Validation Page

- 6.7 Using the GPIO Page

- 6.8 SYNC/SYSREF/1-PPS Page

- 6.9 Using the Outputs Page

- 6.10 EEPROM Page

- 6.11 Design Report Page

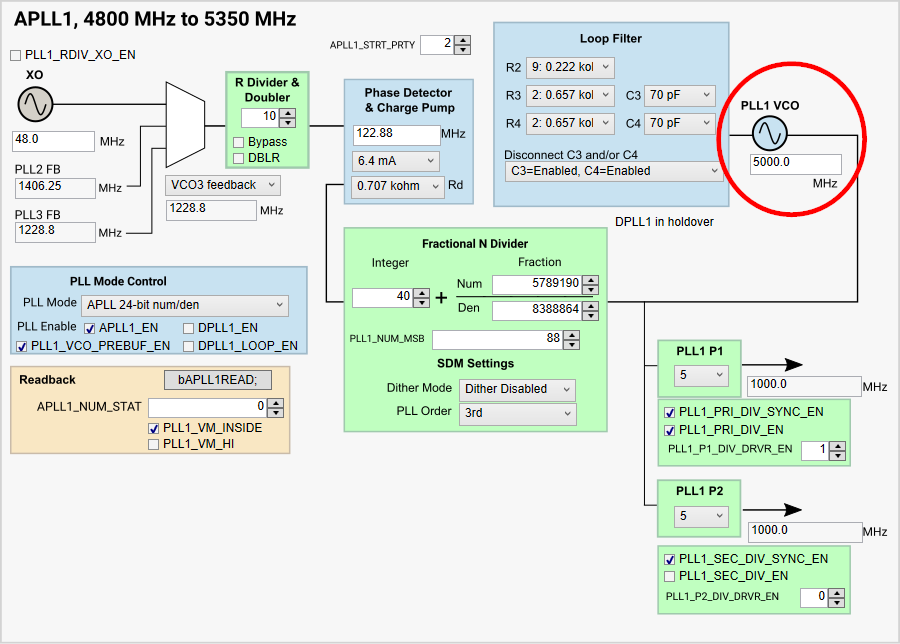

6.4 Using APLL1, APLL2, and APLL3 Pages

The APLL pages can be used to see detailed information on APLL behavior including the output dividers. A possibility is to type a VCO frequency into the PLL1 VCO frequency box (as shown in red circle) to have the fractional N value re-calculated.

When the DPLL is not used, the APLLs support an APLL-only mode with a programmable 24-bit denominator. Support for this mode is currently not implemented in the TICS Pro software.

Figure 6-13 APLL1 Page

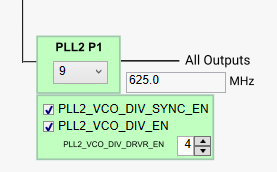

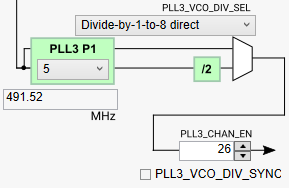

Figure 6-13 APLL1 PageFigure 6-14 shows the post divider for PLL2. Figure 6-15 shows the post divider for PLL3. PLL3 supports all outputs of the LMK5C33414A.

Figure 6-14 PLL2 Post Divider

Figure 6-14 PLL2 Post Divider Figure 6-15 PLL3 Dividers

Figure 6-15 PLL3 Dividers