SNLU131A February 2013 – June 2024

- 1

- Trademarks

- 1 DS90UH928QEVM Introduction

- 2Quick Start Guide

- 3Evaluation Hardware Overview

- 4ALP Software

- 5Related Documentation

- 6Board Schematic

- 7Bill of Materials

- 8Board Layout and Layers

- 9Revision History

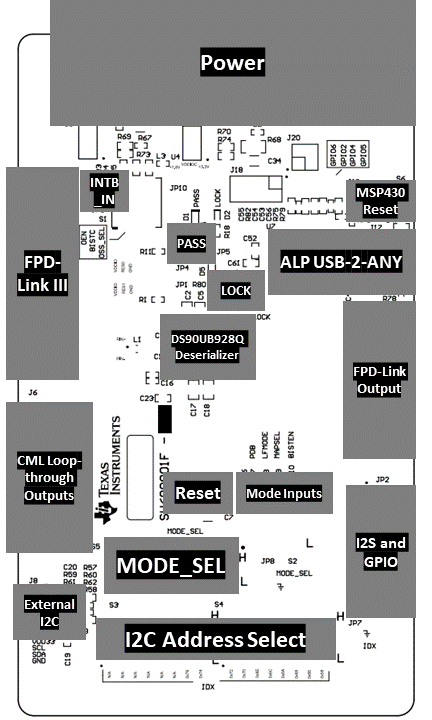

3.1 Board Overview

The evaluation board includes circuits and interfaces facilitating the different device features of the DS90UH928Q deserializer, including power, video data, FPD-Link III interface, I2S audio, I2C control, connectors, and configuration switches.

Figure 3-1 DS90UB928-Q1EVM Layout

Figure 3-1 DS90UB928-Q1EVM Layout