SNOS674J October 1997 – September 2024 LMC6482 , LMC6484

PRODUCTION DATA

- 1

- 1 Features

- 2 Applications

- 3 Description

- 4 Pin Configuration and Functions

- 5 Specifications

- 6 Detailed Description

- 7 Application and Implementation

- 8 Device and Documentation Support

- 9 Revision History

- 10Mechanical, Packaging, and Orderable Information

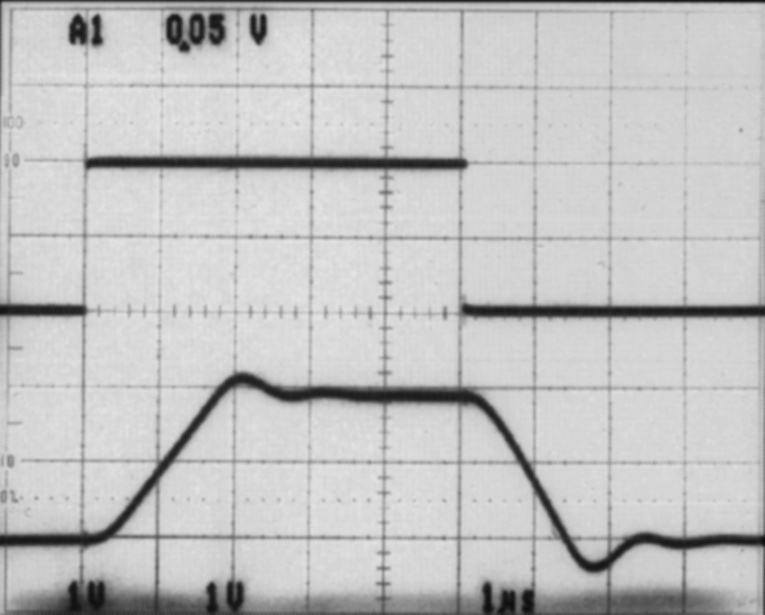

7.2.1.2.2 Capacitive Load Tolerance

The LMC648x can typically directly drive a 100pF load with VS = 15V at unity gain without oscillating. The unity gain follower is the most sensitive configuration. Direct capacitive loading reduces the phase margin of op amps. The combination of the output impedance of the op-amp and the capacitive load induces phase lag. This results in either an underdamped pulse response or oscillation.

Figure 7-10 shows how improved frequency response is achieved by indirectly driving capacitive loads.

R1 and C1 serve to counteract the loss of phase margin by feeding forward the high-frequency component of the output signal back to the amplifiers inverting input, thereby preserving phase margin in the overall feedback loop. The values of R1 and C1 are experimentally determined for the desired pulse response. Figure 7-11 shows the resulting pulse response.

Figure 7-11 Pulse Response of LMC6482

Circuit in Figure 7-10

Figure 7-11 Pulse Response of LMC6482

Circuit in Figure 7-10