-

LM9061 and LM9061-Q1 High-Side Protection Controller

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

- IMPORTANT NOTICE

LM9061 and LM9061-Q1 High-Side Protection Controller

1 Features

- Qualified for Automotive Applications

- AEC-Q100 Qualified With the Following Results:

- Device HBM ESD Classification Level 2

- Device CDM ESD Classification Level C4B

- Withstands 60-V Supply Transients

- Overvoltage Shut-OFF With VCC > 30 V

- Lossless Overcurrent Protection Latch-OFF

- Current Sense Resistor is Not Required

- Minimizes Power Loss With High Current Loads

- Programmable Delay of Protection Latch-OFF

- Gradual Turnoff to Minimize Inductive Load Transient Voltages

- CMOS Logic-Compatible ON and OFF Control Input

2 Applications

- Transmission Control Units (TCU)

- Engine Control Units (ECU)

- Valve, Relay, and Solenoid Drivers

- Lamp Drivers

- DC Motor PWM Drivers

- Logic-Controlled Power Supply Distribution Switches

- Electronic Circuit Breakers

- High-Power Audio Speakers

3 Description

The LM9061 family consists of charge-pump devices which provides the gate drive to an external power MOSFET of any size configured as a high-side driver or switch. This includes multiple parallel connected MOSFETs for very high current applications. A CMOS logic-compatible ON and OFF input controls the output gate drive voltage. In the ON state, the charge pump voltage, which is well above the available VCC supply, is directly applied to the gate of the MOSFET. A built-in 15-V Zener clamps the maximum gate to source voltage of the MOSFET. When commanded OFF a 110-µA current sink discharges the gate capacitances of the MOSFET for a gradual turnoff characteristic to minimize the duration of inductive load transient voltages and further protect the power MOSFET.

Lossless protection of the power MOSFET is a key feature of the LM9061. The voltage drop (VDS) across the power device is continually monitored and compared against an externally programmable threshold voltage. A small current-sensing resistor in series with the load, which causes a loss of available energy, is not required for the protection circuitry. If the VDS voltage, due to excessive load current, exceeds the threshold voltage, the output is latched OFF in a more gradual fashion (through a 10-µA output current sink) after a programmable delay time interval.

Device Information(1)

| PART NUMBER | PACKAGE | BODY SIZE (NOM) |

|---|---|---|

| LM9061, LM9061-Q1 | SOIC (8) | 4.9 mm × 3.91 mm |

- For all available packages, see the orderable addendum at the end of the data sheet.

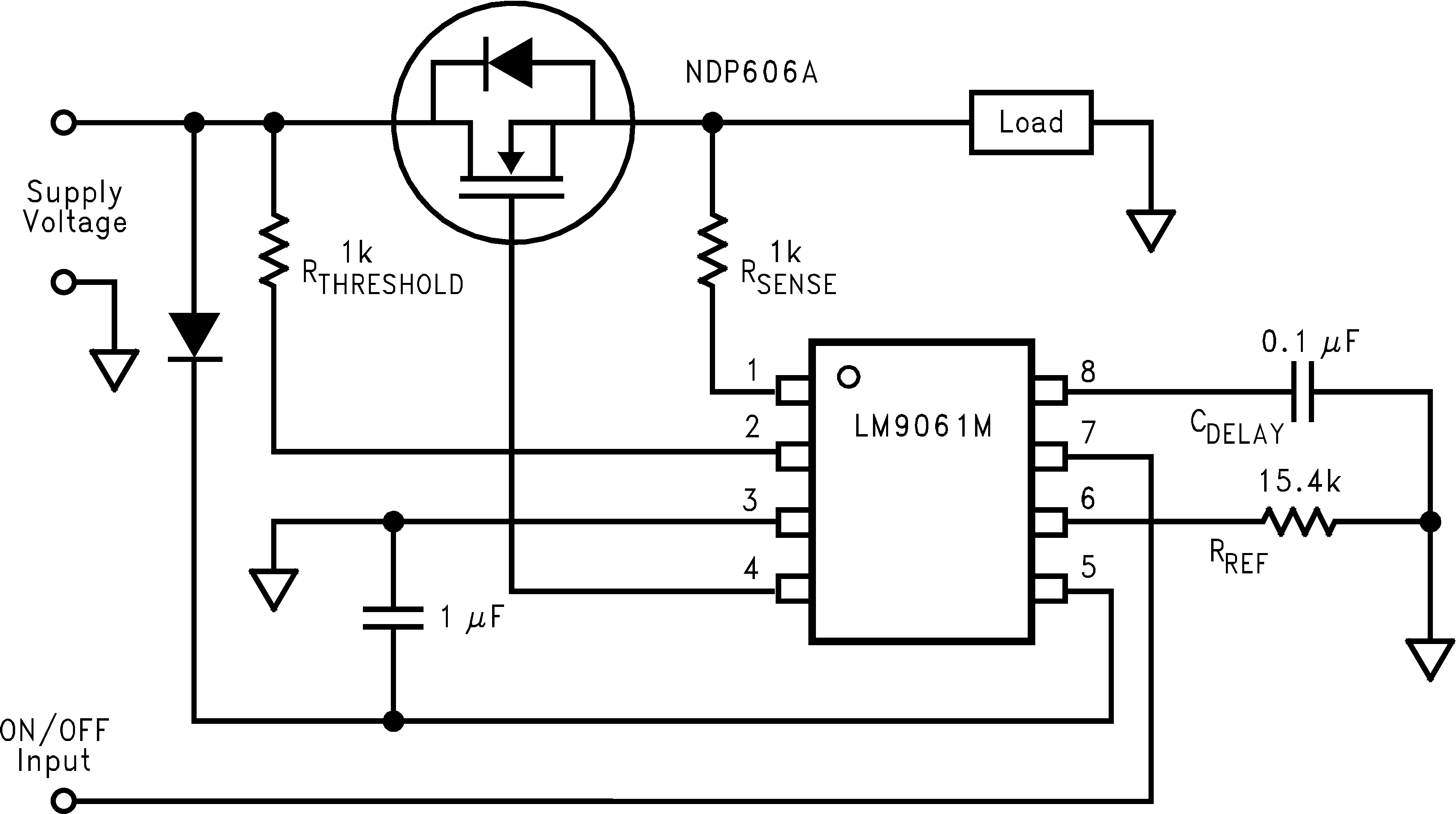

High-Side Driving and Protection to a Connected Load

4 Revision History

Changes from H Revision (January 2015) to I Revision

- Updated data sheet text to the latest TI documentation and translations standards and flowGo

- Added Bidirectional Applications section Go

Changes from G Revision (November 2014) to H Revision

- Changed Handling Ratings to ESD Ratings Go

- Added content to Application and Implementation sectionGo

- Changed Layout Example figure Go

Changes from F Revision (April 1995) to G Revision

- Added AEC-Q100 Qualification Go

- Added Handling Ratings table, Thermal Information table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information sectionGo

Changes from E Revision (April 2013) to F Revision

- Changed layout of National Data Sheet to TI formatGo

5 Pin Configuration and Functions

Pin Functions

| PIN | I/O | DESCRIPTION | |

|---|---|---|---|

| NAME | NO. | ||

| Sense | 1 | I | The inverting input to the protection comparator, connected to the external MOSFET source pin and the load. |

| Threshold | 2 | I | The noninverting input to the protection comparator, and a current sink for the threshold resistor to set the allowed voltage drop across the external MOSFET. |

| Ground | 3 | — | Ground |

| Output | 4 | O | The gate drive connection. Charges, and discharges, the MOSFET gate. |

| VCC | 5 | I | The voltage supply pin. The VCC operating range has a minimum value of 7 V, and a maximum value of 26 V. |

| IREF | 6 | O | A resistor on this pin to ground sets the current through the threshold resistor, which sets the allowed voltage drop across the external MOSFET. |

| On/Off | 7 | I | The control pin. A low voltage, VIN(0), will disable device operation, while a high voltage, VIN(1), will enable device operation. |

| Delay | 8 | O | A capacitor on this pin to ground will provide a delay time between when the protection comparator detects excessive VGS across the MOSFET and when the gate drive circuitry is latched-OFF. |

6 Specifications

6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)(1)| MIN | MAX | UNIT | ||

|---|---|---|---|---|

| Supply voltage | 60 | V | ||

| Output voltage | VCC + 15 | V | ||

| Voltage at sense and threshold (through 1 kΩ) | −25 | 60 | V | |

| ON/OFF input voltage | −0.3 | VCC + 0.3 | V | |

| Reverse supply current | 20 | mA | ||

| Junction temperature | 150 | °C | ||

| Lead temperature soldering, 10 seconds | 260 | °C | ||

| Storage temperature, Tstg | −55 | 150 | °C | |

6.2 ESD Ratings: LM9061

| VALUE | UNIT | |||

|---|---|---|---|---|

| V(ESD) | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001(1) | ±2000 | V |

| Charged-device model (CDM), per JEDEC specification JESD22-C101(2) | ±1000 | |||

6.3 ESD Ratings: LM9061-Q1

| VALUE | UNIT | ||||

|---|---|---|---|---|---|

| V(ESD) | Electrostatic discharge | Human-body model (HBM), per AEC Q100-002(1) | ±2000 | V | |

| Charged-device model (CDM), per AEC Q100-011 | All pins except 1, 4, 5, and 8 | ±1000 | |||

| Pins 1, 4, 5, and 8 | ±1000 | ||||

6.4 Recommended Operating Conditions(1)

over operating free-air temperature range (unless otherwise noted)| MIN | NOM | MAX | UNIT | ||

|---|---|---|---|---|---|

| Supply voltage | 7 | 26 | V | ||

| ON/OFF input voltage | −0.3 | VCC | V | ||

| Ambient temperature: LM9061 | −40 | 125 | °C | ||

| Junction temperature: LM9061-Q1 | −40 | 125 | °C | ||

6.5 Thermal Information

| THERMAL METRIC(1) | LM9061, LM9061-Q1 | UNIT | |

|---|---|---|---|

| D (SOIC) | |||

| 8 PINS | |||

| RθJA | Junction-to-ambient thermal resistance | 150 | °C/W |

| RθJC(top) | Junction-to-case (top) thermal resistance | 46.7 | °C/W |

| RθJB | Junction-to-board thermal resistance | 49.1 | °C/W |

| ψJT | Junction-to-top characterization parameter | 6.2 | °C/W |

| ψJB | Junction-to-board characterization parameter | 48.4 | °C/W |

6.6 Electrical Characteristics

over operating free-air temperature range (unless otherwise noted)7 V ≤ VCC ≤ 20 V, RREF = 15.4 kΩ, −40°C ≤ TJ ≤ +125°C, unless otherwise specified.

| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| POWER SUPPLY | ||||||

| IQ | Quiescent supply current | ON/OFF = 0 | 5 | mA | ||

| ICC | Operating supply current | ON/OFF = 1, CLOAD = 0.025 µF, includes turnon transient output current |

40 | mA | ||

| ON/OFF CONTROL INPUT | ||||||

| VIN(0) | ON/OFF input logic 0 | VOUT = OFF | 1.5 | V | ||

| VIN(1) | ON/OFF input logic 1 | VOUT = ON | 3.5 | V | ||

| VHYST | ON/OFF input hysteresis | Peak-to-peak | 0.8 | 2 | V | |

| IIN | ON/OFF input pulldown current | VON/OFF = 5 V | 50 | 250 | µA | |

| GATE DRIVE OUTPUT | ||||||

| VOH | Charge pump output voltage | ON/OFF = 1 | VCC + 7 | VCC + 15 | V | |

| VOL | OFF output voltage | ON/OFF = 0, ISINK = 110 µA | 0.9 | V | ||

| VCLAMP | Sense to output clamp voltage |

ON/OFF = 1, VSENSE = VTHRESHOLD |

11 | 15 | V | |

| ISINK(Normal-OFF) | Output sink current normal operation |

ON/OFF = 0, VDELAY = 0 V, VSENSE = VTHRESHOLD |

75 | 145 | µA | |

| ISINK(Latch-OFF) | Output sink current with protection comparator tripped |

VDELAY = 7 V, VSENSE < VTHRESHOLD |

5 | 15 | µA | |

| PROTECTION CIRCUITRY | ||||||

| VREF | Reference voltage | 1.15 | 1.35 | V | ||

| IREF | Threshold pin reference current | VSENSE = VTHRESHOLD | 75 | 88 | µA | |

| ITHR(LEAKAGE) | Threshold pin leakage current | VCC = Open, 7 V ≤ VTHRESHOLD ≤ 20 V | 10 | µA | ||

| ISENSE | Sense pin input bias current | VSENSE = VTHRESHOLD | 10 | µA | ||

| DELAY TIMER | ||||||

| VTIMER | Delay timer threshold voltage | 5 | 6.2 | V | ||

| VSAT | Discharge transistor saturation voltage | IDIS = 1 mA | 0.4 | V | ||

| IDIS | Delay capacitor discharge current | VDELAY = 5 V | 2 | 10 | mA | |

| IDELAY | Delay pin source current | 6.74 | 15.44 | µA | ||

6.7 Switching Characteristics

over operating free-air temperature range (unless otherwise noted)7V ≤ VCC ≤ 20V, RREF = 15.4 kΩ, −40°C ≤ TJ ≤ +125°C, CLOAD = 0.025 µF, CDELAY = 0.022 µF, unless otherwise specified.

| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | ||

|---|---|---|---|---|---|---|---|

| TON | Output turnon time | CLOAD = 0.025 µF | 7V ≤ VCC ≤ 10 V, VOUT ≥ VCC + 7 V | 1.5 | ms | ||

| 10V ≤ VCC ≤ 20 V, VOUT ≥ VCC + 11 V | 1.5 | ||||||

| TOFF(NORMAL) | Output turnoff time, normal operation(2) |

CLOAD = 0.025 µF VCC = 14 V, VOUT ≥ 25 V VSENSE = VTHRESHOLD |

4 | 10 | ms | ||

| TOFF(Latch-OFF) | Output turnoff time, protection comparator tripped(2) |

CLOAD = 0.025 µF VCC = 14 V, VOUT ≥ 25 V VSENSE = VTHRESHOLD |

45 | 140 | ms | ||

| TDELAY | Delay timer interval | CDELAY = 0.022 µF | 8 | 18 | ms | ||

Figure 1. Typical Operating Waveforms

Figure 1. Typical Operating Waveforms

Figure 2. Timing Definitions

Figure 2. Timing Definitions

6.8 Typical Characteristics

Figure 3. Standby Supply Current vs VCC

Figure 3. Standby Supply Current vs VCC

Figure 5. Output Voltage vs VCC

Figure 5. Output Voltage vs VCC

Figure 7. Output Sink Current vs Temperature

Figure 7. Output Sink Current vs Temperature

Figure 9. Reference Voltage vs Temperature

Figure 9. Reference Voltage vs Temperature

Figure 11. Delay Charge Current vs Temperature

Figure 11. Delay Charge Current vs Temperature

Figure 4. Operating Supply Current vs VCC

Figure 4. Operating Supply Current vs VCC

Figure 6. Output Sink Current vs Temperature

Figure 6. Output Sink Current vs Temperature

Figure 8. Output Source Current vs Output Voltage

Figure 8. Output Source Current vs Output Voltage

Figure 10. Delay Threshold vs Temperature

Figure 10. Delay Threshold vs Temperature