SNOSDB6D December 2020 – October 2024 LMP7704-SP

PRODUCTION DATA

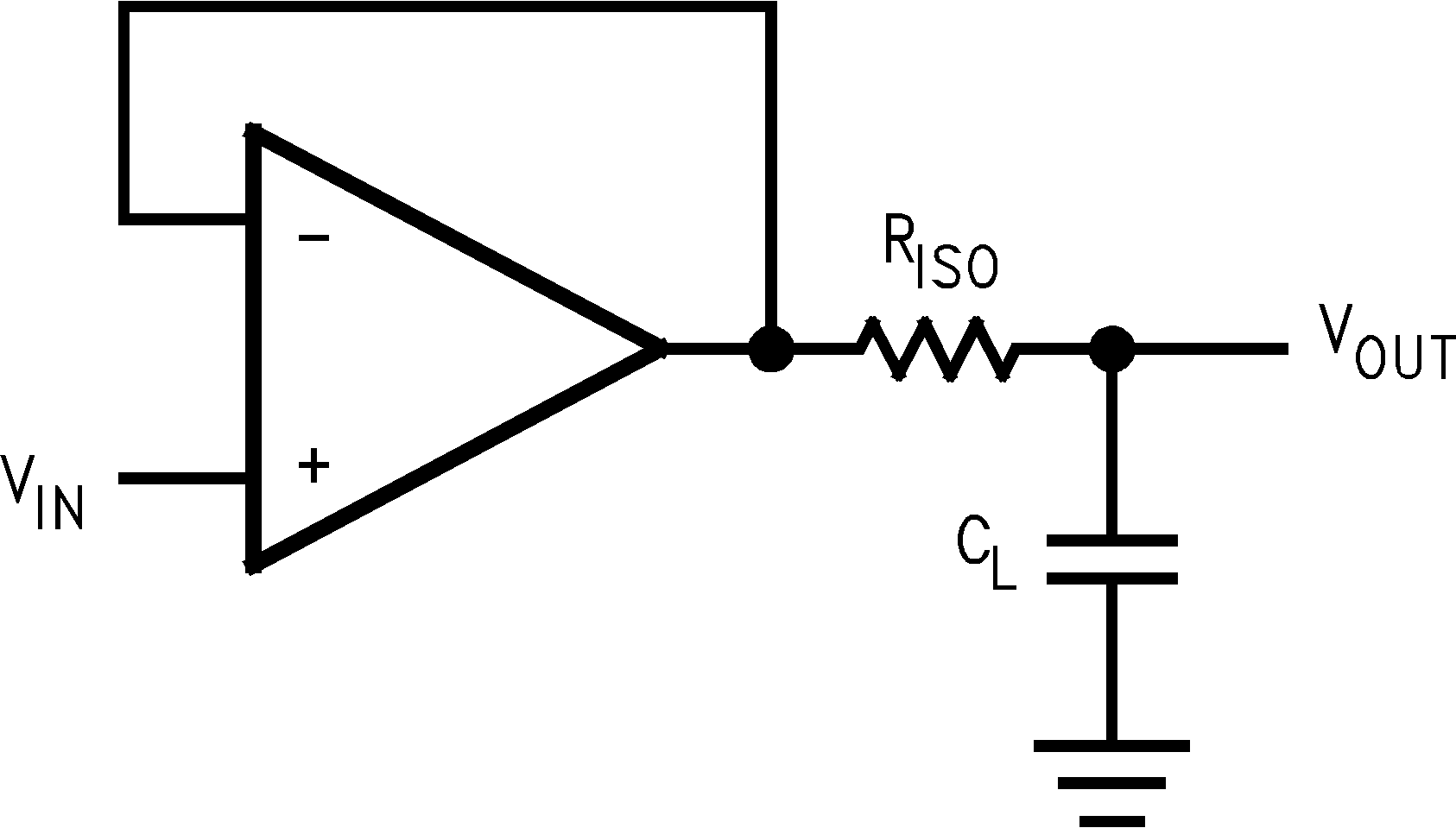

6.3.4 Capacitive Load

The LMP7704-SP can be connected as a noninverting unity gain follower. This configuration is the most sensitive to capacitive loading.

The combination of a capacitive load placed on the output of an amplifier along with the amplifier output impedance creates a phase lag, which in turn reduces the phase margin of the amplifier. If the phase margin is significantly reduced, the response is either underdamped or oscillated.

To drive heavier capacitive loads, use an isolation resistor, labeled as RISO in Figure 6-2. By using this isolation resistor, the capacitive load is isolated from the amplifier output, and thus, the pole caused by CL is no longer in the feedback loop. The larger the value of RISO, the more stable the output voltage. If values of RISO are sufficiently large, the feedback loop is stable, independent of the value of CL. However, larger values of RISO result in reduced output swing and reduced output current drive.

Figure 6-2 Isolating Capacitive Load

Figure 6-2 Isolating Capacitive Load