SPAU023 June 2024

- 1

- Description

- Features

- 4

- 1Evaluation Module Overview

-

2Hardware

- 2.1

System Description

- 2.1.1 Key Features

- 2.1.2 Important Usage Notes:

- 2.1.3 Functional Block Diagram

- 2.1.4 Power ON/OFF Procedures

- 2.1.5 Peripheral and Major Component Description

- 2.1

System Description

- 3Hardware Design Files

- 4Additional Information

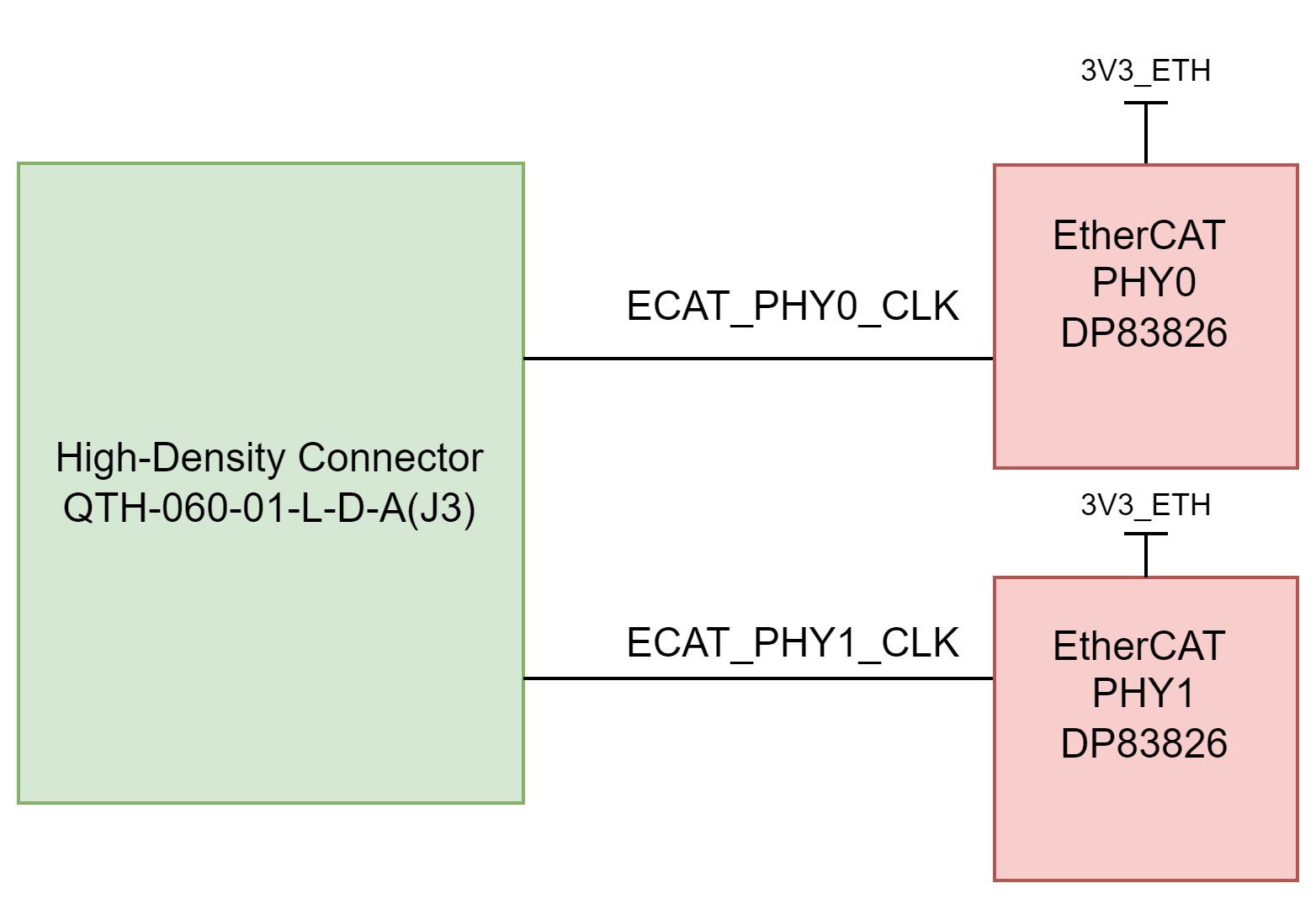

2.1.5.1 Clocking

The Clock architecture of the HSEC Adapter board is shown below.

Figure 2-5 Clock Architecture

Figure 2-5 Clock ArchitectureA clock generator of part number LMK1C1103PWR is used in SOM to drive the 25MHz clock to two EtherCATPHYs, and F28P65x MCU Clock. LMK1C1103PWR is a 1:3 LVCMOS clock buffer, which takes the 25MHz crystal/LVCMOS reference input and provides four 25MHz LVCMOS clock outputs. The clock signal for EtherCAT PHYs is routed from SOM to High-density connector.