SPRACV1B February 2022 – January 2024 AM2434 , AM6411 , AM6412 , AM6421 , AM6441 , AM6442

4.3.1 Test Setup

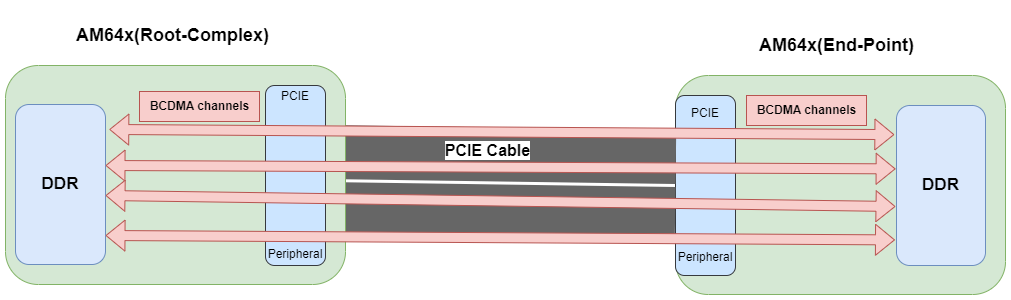

AM64x-PCIE Benchmarking Setup

Here is the setup we used for benchmarking PCIE-BCDMA-DDR read performance (in terms of bandwidth).

Hardware Details:

- TMDS64EVM

- PCIE cable can be obtained from Adex Electronics.

For more details, see:

Software Details:- Test code is available at GitHub Link which is MCU+ SDK 8.6 baselined.

To run the test with more channels than the default configuration, you need to first use the resource management (RM) tool to manage UDMA channel allocation to the cores.

Figure 4-2 AM64x-PCIE Benchmarking

Setup

Figure 4-2 AM64x-PCIE Benchmarking

Setup Figure 4-3 AM64x (PCIE benchmarking) Data

Flow. Here are the details about data flow between 2-AM64x board during PCIE

benchmarking.

Figure 4-3 AM64x (PCIE benchmarking) Data

Flow. Here are the details about data flow between 2-AM64x board during PCIE

benchmarking.EP sets the buffer in PCIE and RC will read and copy it into DDR

For example, on RC side:

PCIE_loc_1 = 0x68000000UL + 0x00000000U

PCIE_loc_2 = 0x68000000UL + 0x01000000U

PCIE_loc_3 = 0x68000000UL + 0x02000000U

PCIE_loc_4 = 0x68000000UL + 0x03000000U

and

DDR_loc_1 = 0xA0000000 + 0x00000000U

DDR_loc_2 = 0xA0000000 + 0x01000000U

DDR_loc_3 = 0xA0000000 + 0x02000000U

DDR_loc_4 = 0xA0000000 + 0x03000000U

And so on.