SPRACX6 June 2021 DRA821U , DRA821U , DRA821U-Q1 , DRA821U-Q1 , DRA829J , DRA829J , DRA829J-Q1 , DRA829J-Q1 , DRA829V , DRA829V , DRA829V-Q1 , DRA829V-Q1 , TDA4VM , TDA4VM , TDA4VM-Q1 , TDA4VM-Q1

5.3 A72 Master Firewall

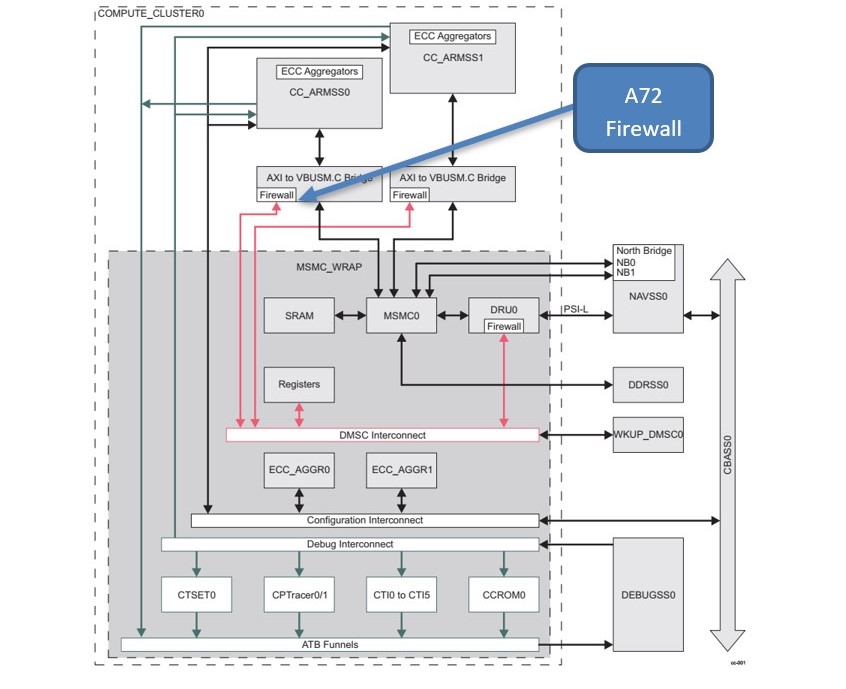

The A72 itself is a master on the interconnect and has a master side firewall capable of filtering outgoing transactions. Figure 5-1 (available in the Technical Reference for the DRA829 / TDA4 device) shows where the firewall to be programmed is located.

The master side firewall for the A72 has a

Firewall Id of 257, as seen in below code example as

CSL_MSTR_FW_A72SS0_CORE0_CPU_0_CPU_0_MSMC_ID.

Figure 5-1 COMPUTE_CLUSTER0 Overview

Figure 5-1 COMPUTE_CLUSTER0 Overview