SPRAD61A March 2023 – November 2023 AM2732 , AM2732 , AM2732-Q1 , AM2732-Q1

- 1

- Abstract

- Trademarks

- 1 Introduction

- 2 Power

- 3 Clocking

- 4 Resets

- 5 Bootstrapping

- 6 JTAG Emulators and Trace

- 7 Multiplexed Peripherals

- 8 Digital Peripherals

- 9 Layer Stackup

- 10Vias

- 11BGA Power Fan-Out and Decoupling Placement

- 12References

- 13Revision History

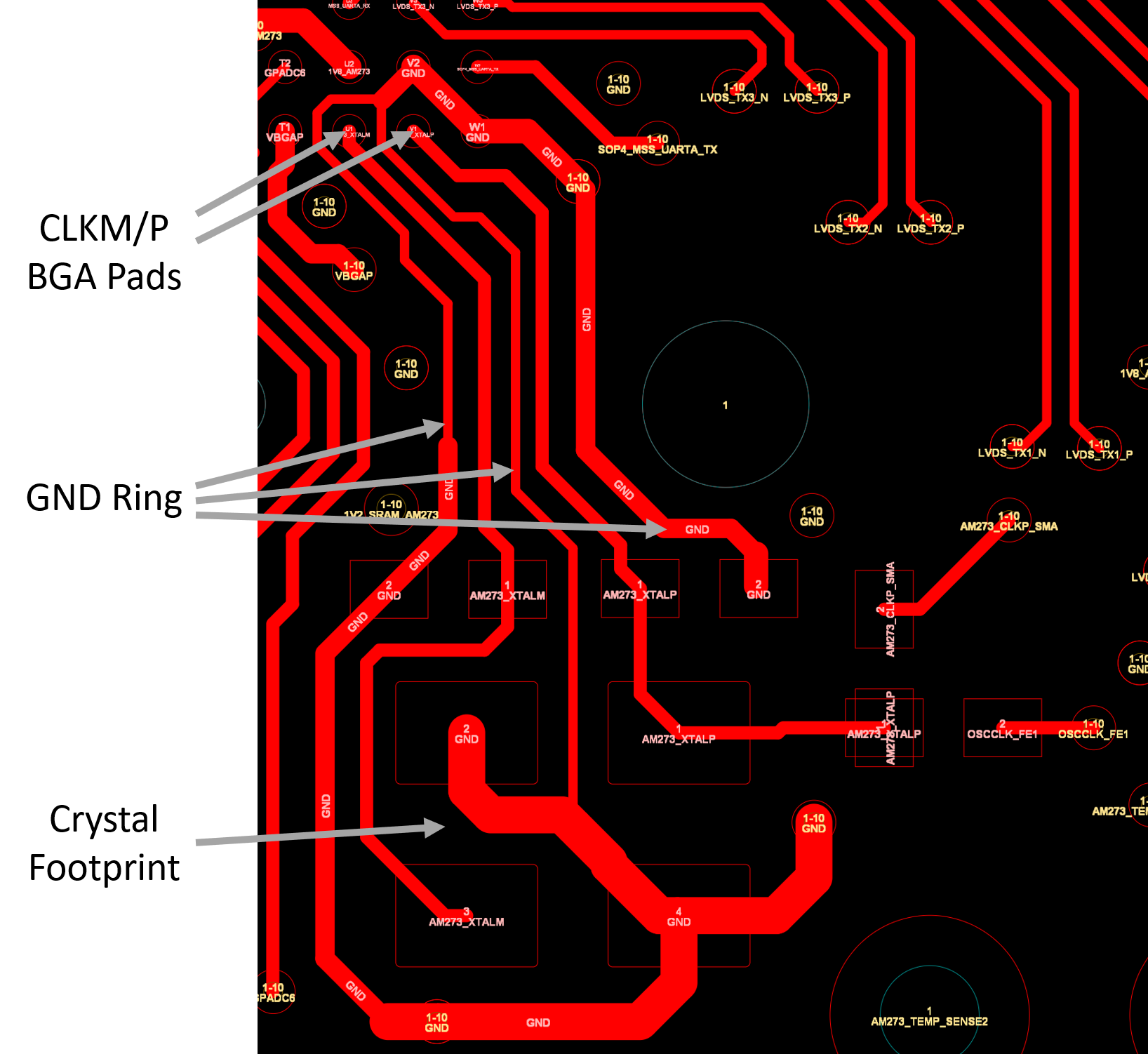

3.4 Crystal Placement and Routing

Crystal oscillator input should be placed as close as possible to the AM273x CLKM/P pads with minimal length traces between crystal and AM273x pads. A ground ring shorted to the local VSS plane should be placed adjacent and between the CLKM and CLKP traces to help prevent coupling from adjacent signals onto the clock higher impedance crystal input paths.

Figure 3-2 Excerpt From AM273x GPEVM

Layout - Crystal Layout and Ground Ring Structure

Figure 3-2 Excerpt From AM273x GPEVM

Layout - Crystal Layout and Ground Ring Structure