SPRADG4A January 2024 – April 2024

- 1

- Abstract

- Trademarks

- 1General Texas Instruments High Voltage Evaluation (TI HV EVM) User Safety Guidelines

- 2Introduction

- 3System Description

- 4System Overview

- 5Hardware

-

6Software

- 6.1 Getting Started With Firmware

- 6.2 SysConfig Setup

- 6.3 Incremental Builds

- 7Testing and Results

- 8References

- 9Revision History

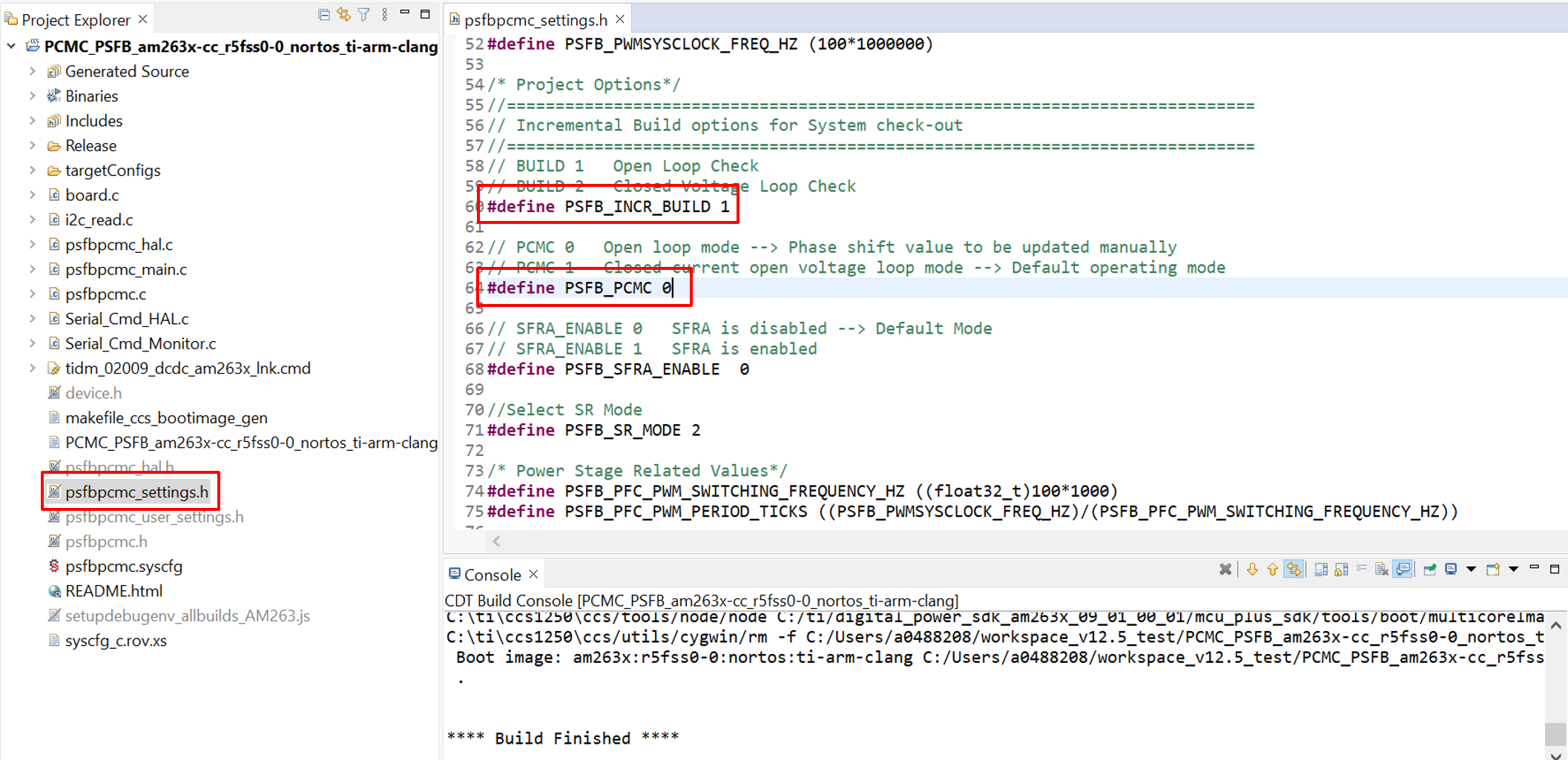

6.3.1.1.3.2 Build and Load the Project for Lab 1

- Click on the expand sign (>) on the left of the project name PCMC_PSFB_am263x-cc_r5fss0-0_nortos_ti-arm-clang and open the psfbpcmc_settings.h as shown in Lab 1 setup. The setting is #define INCR_BUILD 1. This enables the build 1 solution.

- Set #define PSFB_PCMC 0 in the psfbpcmc_settings.h. The default value of PSFB_PCMC is defined as 1 to execute closed current loop (this mode is discussed in detail in upcoming sections).

- Click on the View tab on the top left. Click on Target Configuration. The Target Configuration window opens. Right click on user defined and select Import Target Configuration. Browse to the CCS workspace where the project was imported. Open the targetConfigs folder and select the AM263x_Real_Time_debug.ccxml.

- Double click on AM263x_Real_Time_debug.ccxml and do the Test Connection check. If the check fails, change the COM Port number following the steps mentioned in AM263x Real Time Debug setup. This COM Port number varies from one controlCARD to another. Proceed further only when Test Connection is successfully passed.

- Turn ON the 5V DC bench power supply. Connect the USB cable to the Control card and make sure LD7 is glowing green. In the Target Configuration window, select AM263x_Real_Time_debug.ccxml. Click on the Debug button. The Lab 1 code is built successfully without any error.

- Notice the CCS Debug icon in the upper right corner indicating that the process is now in the Debug Perspective view. Right click on the Cortex_R5_0 in the Debug window and select Connect Target. Now click on the Load icon from the tab on the top side. Load the .out file which was just built successfully. Now .out is successfully loaded to Core_0. The program is stopped at the start of main().

Figure 6-6 Lab 1 Setup

Figure 6-6 Lab 1 Setup